New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

6-30-1989

## Optimal algorithmic testing of re-programmable logic arrays

Arvind Chopra New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Chopra, Arvind, "Optimal algorithmic testing of re-programmable logic arrays" (1989). *Theses*. 2749. https://digitalcommons.njit.edu/theses/2749

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## OPTIMAL ALGORITHMIC TESTING OF RE-PROGRAMMABLE LOGIC ARRAYS

(May 1989)

Arvind Chopra, M.S.E.E., New Jersey Institute of Technology Thesis Advisor: Dr. William N. Carr

This research delineates a test strategy and detailed sequence of test vectors for a new class of programmable logic devices (PLDs). This new class of devices is based on architectures that contain programmable logic arrays (PLAs) programmed by on chip integrated static RAMs or EEPROMS. The new PLD architecture poses unique testing problems which require 100% nodal test coverage. Previous PLAs/PLDs did not require that 100% of the nodes be tested since their circuits utilized fuse link crosspoints and were not dynamically reprogrammable. Such devices could be tested by a unique personality pattern that combined the application and the test circuit. The new PLA/PLD architecture requires testing of arbitrary personality patterns. The dynamic reprogrammability of these devices presents a more challenging 100% test requirement. The same PLA/PLD device can be reconfigured for many different personality patterns permitting a 100% internal node coverage using externally applied test stimulus-response sequences at the packaged device's pins.

This work details the testing of a specific PLA/PLD circuit but attempts to provide a scheme of general applicability. All stuck at, bridge and crosspoint faults are tested. The unified testing scheme minimizes the costs for both the production and application environments.

## OPTIMAL ALGORITHMIC TESTING OF RE-PROGRAMMABLE LOGIC ARRAYS

by Arvind Chopra

Thesis submitted to the Faculty of the Graduate School of the New Jersey Institute of Technology in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering 1989

#### APROVAL SHEET

Title of Thesis:

Optimal Algorithmic Testing of ReProgrammable Logic Arrays.

Name of Candidate:

Arvind Chopra Master of Science in Electrical Engineering, 1989

Thesis and Abstract Approved:

Dr. William N. Carr Professor Electrical Engineering

June 22, 1989

Date

June 23, 1989

Dr. Durga Misra Assistant Professor Electrical Engineering

Date

Dr. N. M. Ravindra Assistant Professor Electrical Engineering

6. 23. 85

Date

#### VITA

Name: Arvind Chopra **Present address:** Degree and date to be conferred: M.S.E.E., 1989. Date of birth: Place of birth: Secondary education: DAV College, Chandigarh 1982. Collegiate institutions Dates Degree Date of Degree attended 8/81-5/85 Panjab University B.E.(Hons.) July,1986

Major: Electrical Engineering.

Positions held:

Assistant Engineer (R&D), Hindustan Computers Ltd., New Delhi, India.

M.S.E.E.

Oct,1989

Research Assistant; Microelectronics Center, NJIT, Newark, NJ.

Teaching Assistant; Physics Dept., NJIT, Newark, NJ.

New Jersey Institute of Technology 01/88-5/89

#### ACKNOWLEDGEMENT

I wish to express my grateful indebtness to Prof. William N. Carr at the EE Department, NJIT for his continuous guidance and encouragement throughout the course of this thesis work. I am beholden to Prof. Durga Misra and Prof. N. M. Ravindra for sparing their valuable time to go over and help in the consolidation of this work. My appreciation is due to my colleagues Jayesh, Praveen, Elie, Alexis and Ravi Prakash, for their suggestions, help and for creating the stimulating atmosphere we all worked in. I am also thankful to Dr. Zheng Teng and Ruyan Wang for making available the Microelectronics Laboratory resources. I am eternally grateful to my mentor and grandfather Prof. R. S. Chopra and my parents for their guidance and support. Finally my special thanks to Ines for her constant encouragement and untiring support.

Arvind Chopra

## Contents

| 1 | Intr           | oduction                                | 1  |

|---|----------------|-----------------------------------------|----|

| 2 | $\mathbf{The}$ | NJIT PLD                                | 4  |

|   | 2.1            | The PLD Alternatives                    | 4  |

|   | 2.2            | NJIT PLD Overview                       | 6  |

|   | 2.3            | NJIT PLD Specifications                 | 9  |

|   | 2.4            | Timing Waveforms                        | 14 |

|   | 2.5            | Programming Model                       | 17 |

| 3 | Test           | ing of NJIT PLD                         | 20 |

|   | 3.1            | Test Approach to the NJIT PLD           | 20 |

|   | 3.2            | Test Equipment for the NJIT PLD Testing | 21 |

|   | 3.3            | Overview of NJIT PLD Testing            | 21 |

|   | 3.4            | Power On Check                          | 25 |

|   | 3.5            | Status Generation Check                 | 26 |

|   | 3.6            | SRAM Testing                            | 30 |

| 4 | $\mathbf{PL}$  | A Cell Testing                          | 37 |

|   | 4.1            | Faults in PLAs                          | 37 |

|     | 4.1.1  | Stuck At Faults                                                        | 37 |

|-----|--------|------------------------------------------------------------------------|----|

|     | 4.1.2  | Bridge Faults                                                          | 38 |

|     | 4.1.3  | Cross Point Faults                                                     | 38 |

| 4.2 | Testin | g of PLAs                                                              | 38 |

|     | 4.2.1  | Production Testing                                                     | 40 |

|     | 4.2.2  | User Testing of PLAs                                                   | 43 |

| 4.3 | PLA (  | Cell Testing in the NJIT PLD                                           | 43 |

|     | 4.3.1  | Taxonomy and Nomenclature of PLA Cell Sections                         | 44 |

|     | 4.3.2  | General Test Sequence                                                  | 47 |

|     | 4.3.3  | Test Length                                                            | 47 |

| 4.4 | Test 1 | (Testing of the X,Y and Z Arrays) $\ldots \ldots \ldots \ldots \ldots$ | 49 |

|     | 4.4.1  | Stuck at 0 Fault Detection in the X Array:                             | 52 |

| 4.5 | Stuck  | at 1 Fault Detection in the X Array                                    | 55 |

|     | 4.5.1  | Stuck at 0 Fault Detection in the Y Array                              | 55 |

|     | 4.5.2  | Stuck at 1 Fault Detection in the Y Array                              | 55 |

|     | 4.5.3  | Stuck at 0 Fault Detection in the Z array                              | 56 |

|     | 4.5.4  | Stuck at 1 Fault Detection in the Z Array                              | 56 |

|     | 4.5.5  | Y Array Bridge Faults                                                  | 56 |

|     | 4.5.6  | Z Array Bridge Fault Detection                                         | 57 |

|     | 4.5.7  | INPUT and Output Array Crosspoint Faults                               | 57 |

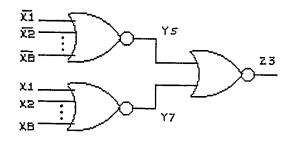

| 4.6 | Test 2 | (Testing of the X,Y and Z Arrays)                                      | 57 |

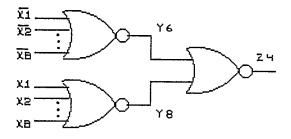

| 4.7 | Test 3 | (Testing of X Array Bridge Faults)                                     | 57 |

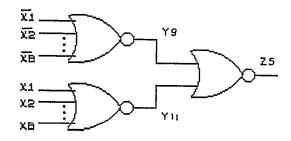

| 4.8 | Test 4 | (Testing of the FEEDBACK Array                                         | 61 |

|     | 4.8.1  | Stuck at 0 Fault Detection on D Lines                                  | 62 |

|              |        | 4.8.2  | Stuck at 1 Fault Detection on D Lines                                     | 62 |

|--------------|--------|--------|---------------------------------------------------------------------------|----|

|              |        | 4.8.3  | Stuck at 0 Fault Detection on Q Lines                                     | 65 |

|              |        | 4.8.4  | Stuck at 0 and stuck at 1 faults on $Y_{17}Y_{18}Y_{20}$ Lines            | 65 |

|              |        | 4.8.5  | Bridge Fault Detection on D Lines                                         | 65 |

|              |        | 4.8.6  | Bridge fault Detection on $Y_{17}Y_{18}Y_{20}$ Lines                      | 66 |

|              |        | 4.8.7  | Bridge Fault Detection on Q Lines                                         | 66 |

|              | 4.9    | Cross  | point Fault Detection in the I/P and O/P Arrays                           | 66 |

|              | 4.10   | Crossp | point Fault Detection with EWHMSAI (Test 1) Pattern                       | 70 |

|              |        | 4.10.1 | Crosspoint Short Detection in the I/P Array                               | 70 |

|              |        | 4.10.2 | Crosspoint Open Detection in the I/P Array                                | 73 |

|              |        | 4.10.3 | Crosspoint Short Fault Detection in the O/P Array                         | 76 |

|              |        | 4.10.4 | Crosspoint Open Fault Detection in the O/P Array $\ldots$ .               | 78 |

|              | 4.11   | Test 5 | (Crosspoint Fault Detection in the D Array)                               | 79 |

|              |        | 4.11.1 | Crosspoint Short Fault Detection in the D Array                           | 79 |

|              |        | 4.11.2 | Crosspoint Open Fault Detection in D Array                                | 82 |

|              |        | 4.11.3 | Crosspoint Short Fault Detection in $Y_{17}Y_{20}$ -X Array               | 82 |

|              |        | 4.11.4 | Crosspoint Open Fault Detection in the $Y_{17}Y_{20}$ Array               | 82 |

|              | 4.12   | Test 6 | (Crosspoint Faults in the Q Array)                                        | 85 |

|              |        | 4.12.1 | Crosspoint Short Fault Detection in the $Y_{17}Y_{20} - X$ Array .        | 85 |

|              |        | 4.12.2 | Crosspoint Open Fault Detection in the $Y_{17} \ldots Y_{20} - X$ Array . | 88 |

|              | 4.13   | Conclu | nsion                                                                     | 88 |

| Re           | eferei | nces   |                                                                           | 92 |

| $\mathbf{A}$ | Test   | Equip  | oment for NJIT PLD                                                        | 94 |

# List of Figures

| 2.1 | Different Forms of Programmable Logic Devices | 7  |

|-----|-----------------------------------------------|----|

| 2.2 | NJIT PLD Block Diagram                        | 8  |

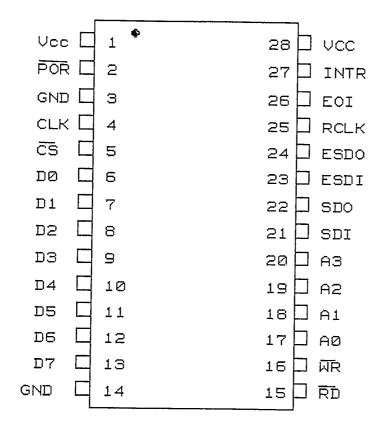

| 2.3 | NJIT PLD Pin Out Diagram                      | 10 |

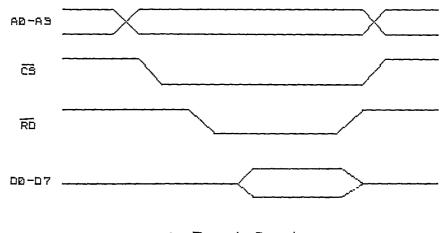

| 2.4 | NJIT PLD Read and Write Cycles                | 15 |

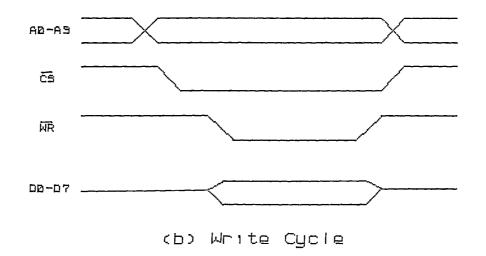

| 2.5 | Power On Reset, SRAM Read and Write Cycles    | 16 |

| 2.6 | Programmer's Model of the NJIT PLD            | 18 |

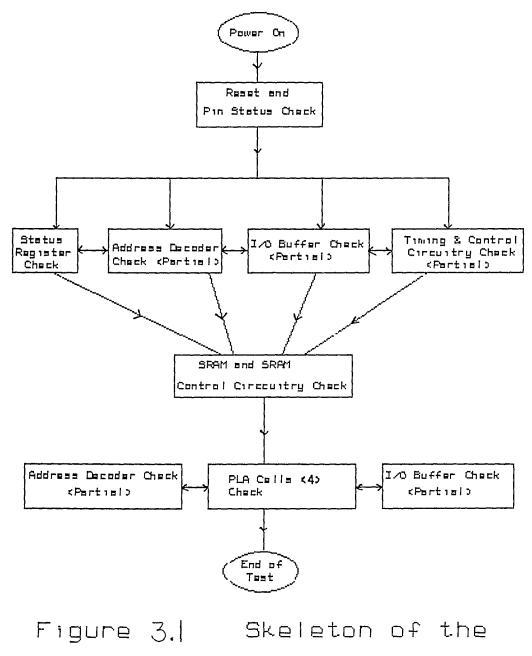

| 3.1 | Skeleton of the NJIT PLD Test Scheme          | 23 |

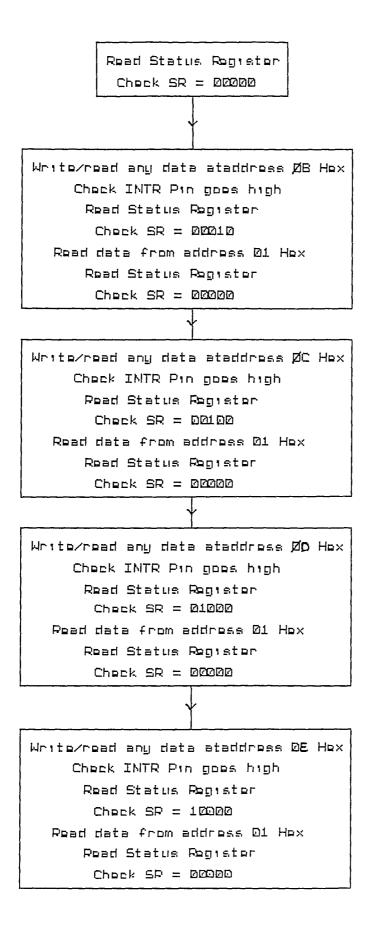

| 3.2 | Status Generation Check                       | 28 |

| 3.3 | SRAM Check Pattern                            | 33 |

| 4.1 | Faults in PLAs                                | 39 |

| 4.2 | Node Coverage in PLA Designs                  | 42 |

| 4.3 | Naming of PLA Sections                        | 45 |

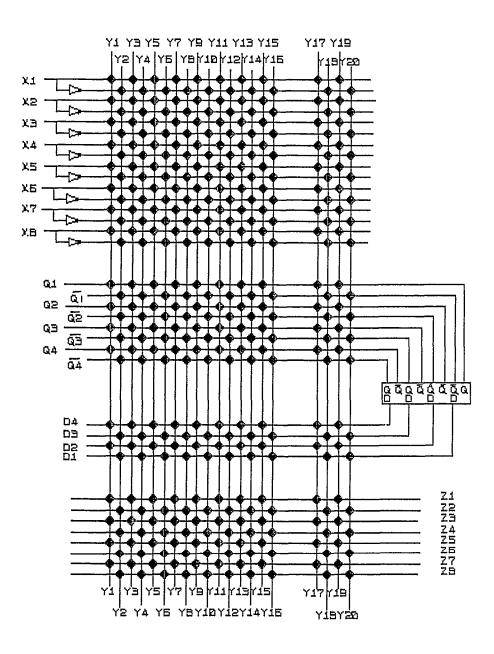

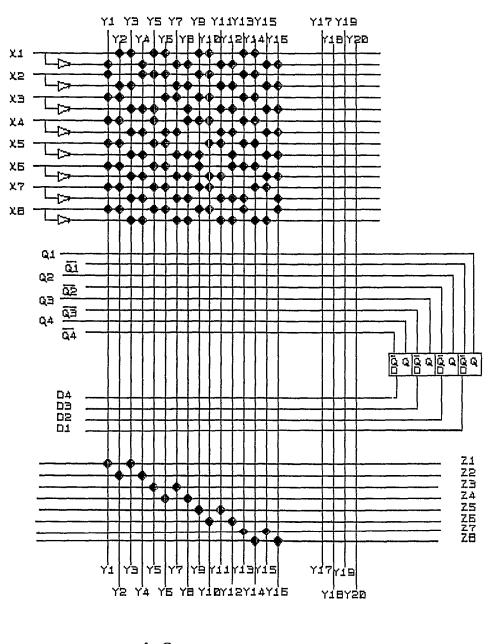

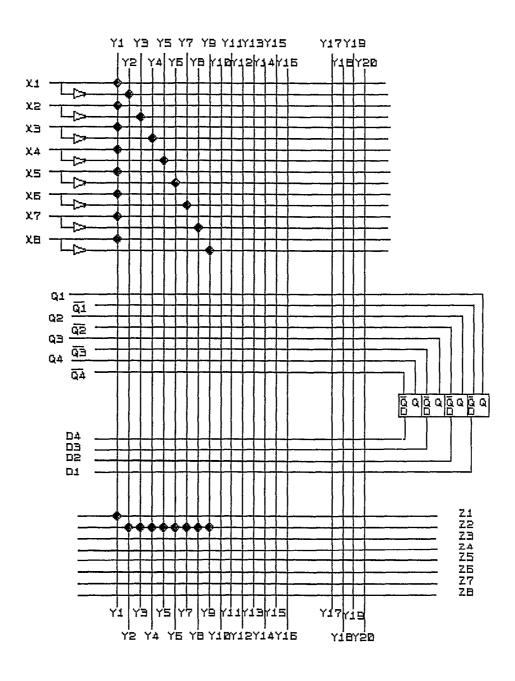

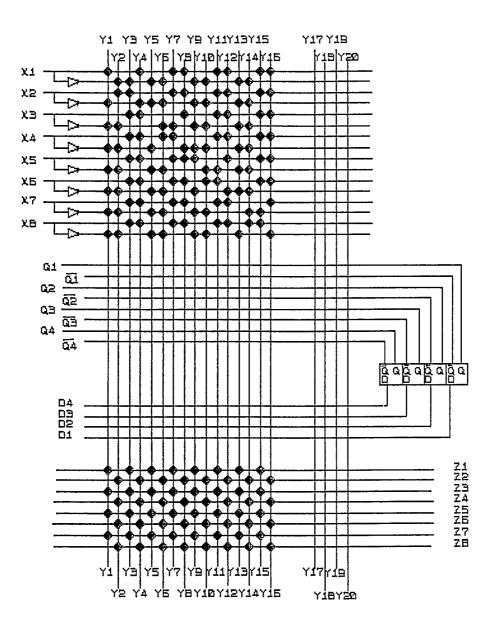

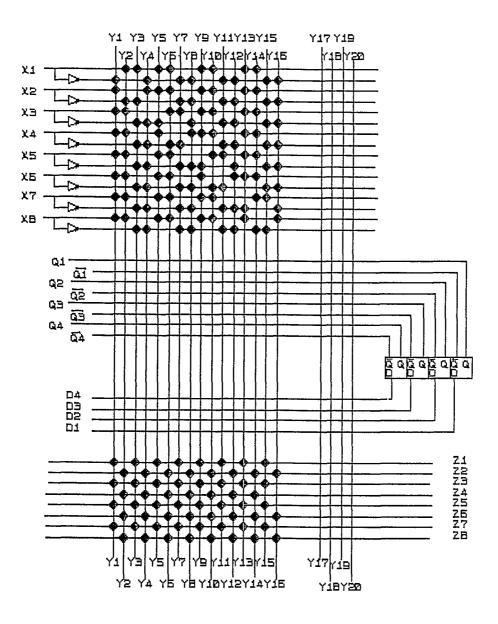

| 4.4 | EWHMSAI Pattern for Test 1                    | 50 |

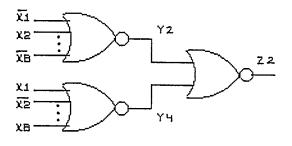

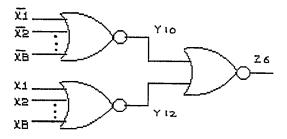

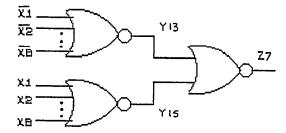

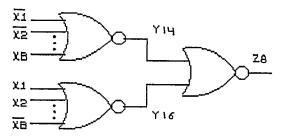

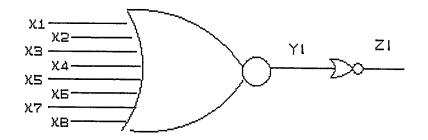

| 4.5 | Circuit Realization for EWHMSAI Pattern 1     | 54 |

| 4.6 | EWHMSAI Pattern 2                             | 58 |

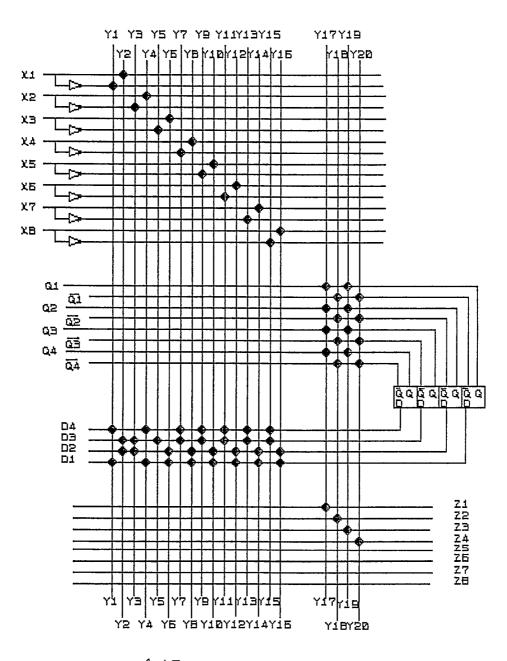

| 4.7 | PLA Cell Pattern for Test 3                   | 59 |

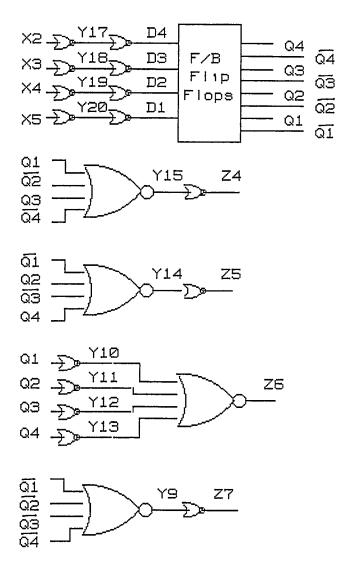

| 4.8 | Circuit Realization for Test 3 Pattern        | 60 |

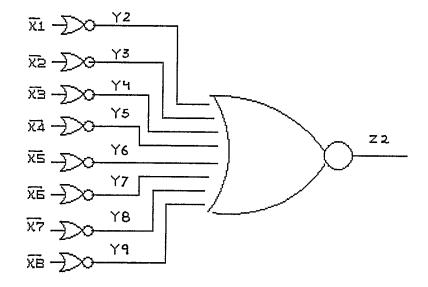

| 4.9  | PLA Cell Pattern for Test 4.                               | 63 |

|------|------------------------------------------------------------|----|

| 4.10 | Circuit Realization for Test 4 Pattern                     | 64 |

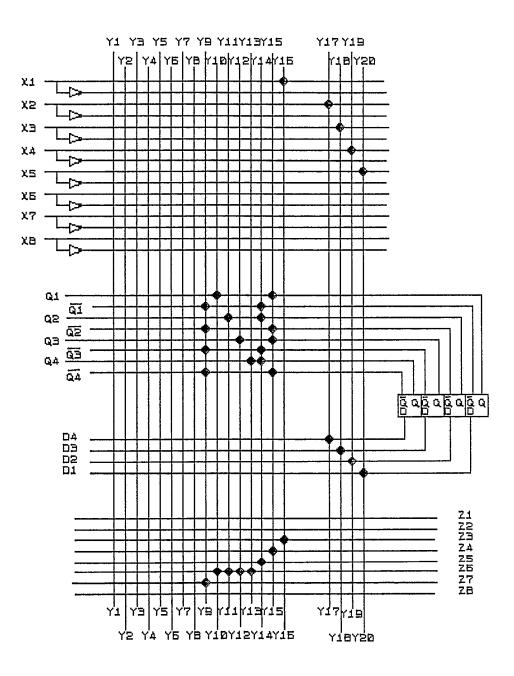

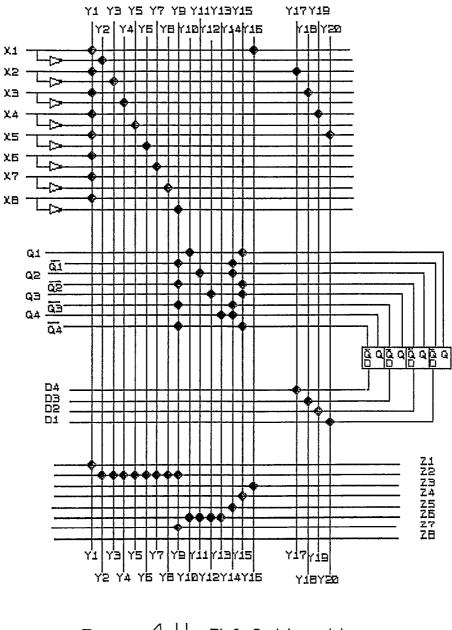

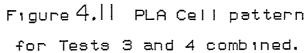

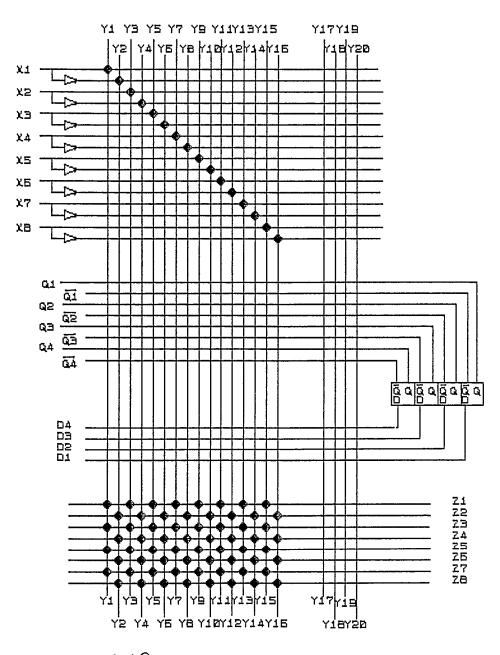

| 4.11 | PLA Cell Pattern for Test 3 and 4 Combined                 | 67 |

| 4.12 | General Scheme for Checking Crosspoint Faults              | 69 |

| 4.13 | EWHMSAI-Checkerboard Pattern 1                             | 71 |

| 4.14 | EWHMSAI-Checkerboard Pattern 2                             | 77 |

| 4.15 | D Array Crosspoint Check Pattern 1                         | 80 |

| 4.16 | Circuit Realization for D Array Crosspoint Check Pattern 1 | 81 |

| 4.17 | D Array Crosspoint Check Pattern 2                         | 84 |

| 4.18 | Q Array Crosspoint Check Pattern 1                         | 86 |

| 4.19 | Circuit Realization for Q Array Crosspoint Check Pattern 1 | 87 |

| 4.20 | Q Array Crosspoint Check Pattern 2                         | 90 |

| A.1  | IMS Test System Cofiguration Screen.                       | 96 |

| A.2  | IMS Test System Resource Assignment Screen                 | 96 |

| A.3  | IMS Test System Operating Conditions Screen                | 97 |

| A.4  | IMS Test System Pattern Control Screen.                    | 97 |

## List of Tables

| 2.1  | NJIT PLD Pin Functions                                                     | 11 |

|------|----------------------------------------------------------------------------|----|

| 4.1  | PLA Cell Sections                                                          | 48 |

| 4.2  | Test 1a (Stuck at 0 Fault Detection in the X and Z Arrays,                 |    |

|      | Stuck at 1 fault detection in the Y Array)                                 | 53 |

| 4.3  | Test 1b (Stuck at 1 Fault detection in the X and Z Arrays,                 |    |

|      | Stuck at 0 in Y Arrays and Bridge Faults in Y and Z Arrays.) $\ldots$      | 53 |

| 4.4  | Test 3 (Testing of X Array Bridge Faults)                                  | 61 |

| 4.5  | Test 4a (Stuck at 0, Stuck at 1 and Bridge Fault Detection on D            |    |

|      | Lines, Stuck at 1 Fault Detection on Q Lines)                              | 62 |

| 4.6  | Test 4b (Stuck at 0 Fault Detection on Q Lines)                            | 65 |

| 4.7  | Test 4c (Bridge Fault Detection on Q Lines)                                | 66 |

| 4.8  | Test 1c (Crosspoint Short                                                  |    |

|      | Detection in the I/P Array)                                                | 72 |

| 4.9  | Test 1d (Crosspoint Open Detection                                         |    |

|      | in the I/P Array)                                                          | 74 |

| 4.10 | Test 5a (Crosspoint Short Fault Detection in the D Array)                  | 82 |

| 4.11 | Test 5b (Crosspoint Open Fault Detection in D Array)                       | 83 |

| 4.12 | Test 5c (Crosspoint Short Fault Detection in the $Y_{17}Y_{20} - X$ Array) | 85 |

|      |                                                                            |    |

| 4.13 | Test 5d (Crosspoint Open Fault Detection in the $Y_{17}Y_{20} - X$ Array) | 89 |

|------|---------------------------------------------------------------------------|----|

| 4.14 | Summary of Test Sequences                                                 | 91 |

# Chapter 1 Introduction

The last few years have seen an increasing use of programmable logic devices such as PROMs, PALs and PLAs. PLAs are being increasingly used to replace random glue logic in large circuit designs. The PLAs offer a smaller turn around time than full custom design and yet a proprietary circuit customization. The use of PLAs poses unique testing problems. The PLAs are usually one time programmable and hence cannot be checked for production faults by the conventional methods. The production tests must completely check the chip for all possible faults. The one time programmability of the PLAs limits the section of the circuitry that can be checked from the external pins. Therefore production testing is done before packaging by wafer probing which requires special equipment and is time consuming. Furthermore after packaging the chip cannot be completely tested and the user must design some test scheme and circuitry to be implemented along with his actual circuit.

A new approach to the design and testing of PLAs is to employ a static RAM instead of one time fusable metal links to enable and disable the crosspoint links in the Input and Output arrays. The reprogrammability allows new circuit implementations at will but also neccessiates a complete diagnostic check to be performed, preferably continuously but at least periodically, say at power on. The reprogrammability would make the chip completely fault testable from the external pins and would also obviate the need to program redundant test circuitry along with the actual circuit.

The NJIT PLD is a SRAM programmable array of four PLA Cells and is used as a model for test derivation. The design and layout of the initial SRAM cell has been done by RAVI VADIYANATHAN in his master's thesis *CMOS SRAM Design for initializing Programmable Logic Devices.* The design and layout of the PLD chip has been implemented by PRAVEEN K. PARVATHALA for his master's thesis *A Dynamic CMOS Programmable Device.* This thesis highlights the design for testability aspects of the chip and its testing scheme in production runs. The production tests may also be executed by a user to check the correct functioning of the chip.

Chapter 2 describes the NJIT PLD as it appears to a user. This chapter describes the various blocks in the chip. It also provides other necessary application information such as the different Pin functions, signal timings, the programmer's model and the the SRAM writing/reading for circuit implementations.

Chapter 3 describes the testing approach to the NJIT PLD. It explains the testing of all the sections except PLA Cells on the chip.

Chapter 4 describes the faults that arise in PLAs. It then discusses the detailed testing of the PLA cells. It details the various test patterns and vectors for detection of different faults in the PLAs.

The test equipment used for actual testing of the NJIT PLD is INTEGRATED MEASUREMENT SYSTEM's HS1000 test station which consists of an IMS1000 Mainframe and VS1000 Verification System. Appendix A gives an overview of the equipment and its use.

# Chapter 2 The NJIT PLD

## 2.1 The PLD Alternatives

Today a logic designer has a plethora of alternatives available for his circuit implementations. These range from standard products to fully customized integration. In between these two extremes are the semi-custom products that include gate arrays, programmable logic devices (PLDs) and standard cell libraries. The major advantages of the PLDs over other types are that they offer a significant chip count reduction from the standard circuit design and have a faster design and development cycle compared with fully customized integration.

The PLD category includes a number of competing alternatives, all based on a programmable AND-OR plane architecture. Bipolar PLDs are programmed by burning or opening fuse links. CMOS PLAs can be one-time programmable, electrically programmable (EPLDs), or electrically erasable (EEPLDs). These PLDs are often used in place of five to ten SSI/MSI devices.

Programmable Read-Only Memories (PROMs), Programmable Array Logic (PALs) devices and Programmable Logic Arrays (PLAs) constitute the three most popular forms of Programmable Logic Devices today. All these PLDs have the same basic two level AND-OR architecture, but vary in their logic features and programmability aspects. The basic AND-OR structure of PLDs makes them ideal for implementing logic equations in Boolean Sum-of-Product form.

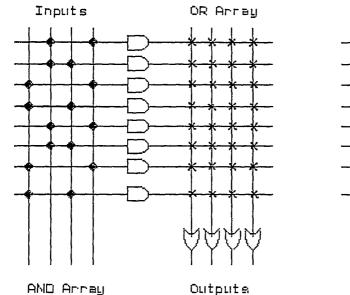

#### PROM

The basic logic structure of the PROM consists of a fixed AND array whose outputs feed a programmable OR array (Fig 2.1a). The PROM inputs are fully decoded by the fixed-AND array. This means that every combination of inputs is represented by a separate AND gate. Since the OR array is programmable, the outputs can be programmed individually corresponding to every possible input combination. A limitation of the PROM is that it is difficult to accommodate a large number of inputs. Each additional input doubles the size of the matrix.

#### $\mathbf{PAL}$

The basic logic structure of the PAL consists of a programmable AND array whose outputs feed a fixed OR array (Fig 2.1b). Unlike the PROM ,the AND array of a PAL device is programmable therefore all the inputs need not be fully decoded. PAL devices may contain additional architectural features such as programmable I/O pins, registered or combinatorial outputs with internal feedback etc. that make them well suited for implementing logic functions.

#### $\mathbf{PLA}$

The basic logic structure of the PLA consists of a programmable AND array and a programmable OR array (Fig 2.1c). The designer has complete control over all inputs and outputs. PLAs allow a great flexibility for implementing logic functions. A limitation of PLAs is that due to the extra programmable-OR plane, a given signal has to pass through two programmable arrays ; as a result, PLAs are inherently slower than PAL devices and PROMs.

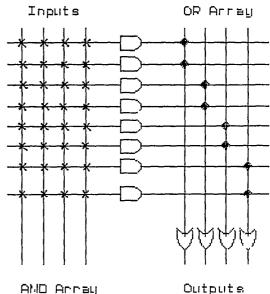

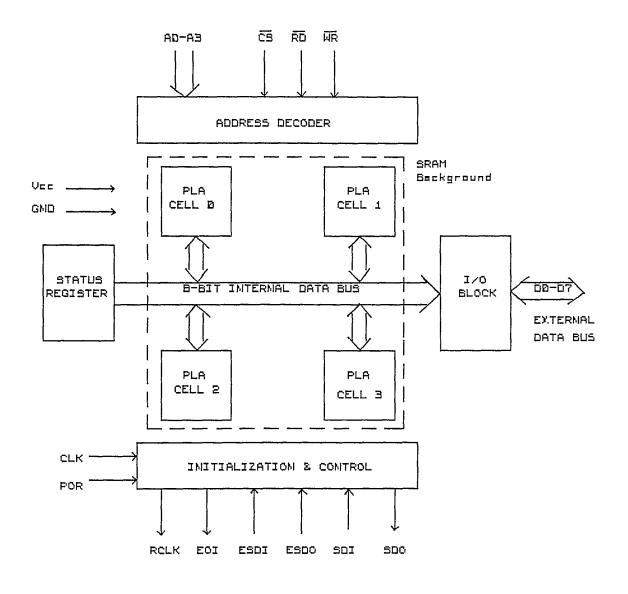

### 2.2 NJIT PLD Overview

The NJIT PLD is an advanced LSI design. It consists of four PLA cells linked by an 8-bit internal data bus. Figure 2.2 shows the basic block diagram. Each of the four PLA cells is individually programmable. There is an I/O block that interfaces the internal bus to an external 8 bit data bus. Each of the four PLA cells has an address to be selectively loaded or read via the data bus. This architecture allows for concurrent operations in the four cells. The PLD is usually connected to a microprocessor or another intelligent unit that issues appropriate commands and data.

To allow dynamic re-programmability each of the PLA cell derives its personality pattern from a SRAM embedded in the background. This SRAM is arranged as 2960 bit (74row X 40column) matrix. Each bit has one to one correspondence with a node in the AND or the OR matrix in the PLA cells. Thus by reprogramming the SRAM the function of the PLA cells may be changed even while powered on. The SRAM is programmed with a serial bit stream and may also be serially readout anytime. There is a daisy chain feature that allows sequential programming of

AND Annay

(b) PAL

(a) PROM

- Indicates Fixed ۰ Connection

- Indicates Programmable X Connection

(c) PLA

Figure 2.1 Different forms of Programmable Logic Devices

Figure 2.2 NJIT PLD Block Diagram

multiple PLDs from a serial source such as the XLINK

Other features of the chip include a status register. This five bit register indicates whether the SRAM has been properly (completely) initialized and the status of each PLA cell. The status register can be read at any time.

Each PLA cell has four feed back flip-flops and hence can be configured as a 16 state machine. There is a feature that enables each cell to signify end of its processing sequence. The CPU can configure the cells as state machines and also implement a *state detection* circuitry that would indicate the end of processing or any other function. This *End of Operation* signal can be used to latch the out put of the PLA cell and also generate an interrupt and set a status bit in the status register.

This is a distinctive feature compared to other contemporary designs. The NJIT PLD is not intended for use as a replacement of glue logic but for processing intensive hardwares for image analysis, signal processing etc. This justifies the multiplexing of the four PLA cells' inputs and outputs on the common data bus. Appendix A contains greater details about the NJIT PLD circuitry.

## 2.3 NJIT PLD Specifications

The pin out diagram of the NJIT PLD is shown in figure 2.3. Table 2.1 describes the various pins and their functions.

## Figure 2.3 NJIT PLD Pin Out Diagram.

| PIN             | I/0 | FUNCTION                                               |  |  |  |  |

|-----------------|-----|--------------------------------------------------------|--|--|--|--|

| V <sub>CC</sub> | -   | +5V Power Supply.                                      |  |  |  |  |

| GND             | -   | Power Supply and signal ground.                        |  |  |  |  |

| A0-A3           | I   | 4 bit address. The address is used to select different |  |  |  |  |

|                 |     | PLA cells and the status register.                     |  |  |  |  |

|                 |     | Address Block Selected                                 |  |  |  |  |

|                 |     | $0 \qquad \text{Cell 0 I/P (CIS0)}$                    |  |  |  |  |

|                 |     | 1 Cell 0 O/P (COS0)                                    |  |  |  |  |

|                 |     | 2 Cell 1 I/P (CIS1)                                    |  |  |  |  |

|                 |     | $3 \qquad \text{Cell 1 O/P (COS1)}$                    |  |  |  |  |

|                 |     | 4 Cell 2 I/P (CIS2)                                    |  |  |  |  |

|                 |     | 5 Cell 2 $0/P$ (COS2)                                  |  |  |  |  |

|                 |     | 6 Cell 3 I/P (CIS3)                                    |  |  |  |  |

|                 |     | 7 Cell 3 O/P (COS3)                                    |  |  |  |  |

|                 |     | 8 Nibble Mode 1 (NM1)                                  |  |  |  |  |

|                 |     | 9 Nibble Mode 2 (NM2)                                  |  |  |  |  |

|                 |     | 10 Status Register (SR)                                |  |  |  |  |

|                 |     | 11 PLA 0 O/P Latch Enable (EOP0)                       |  |  |  |  |

|                 |     | 12 PLA 1 O/P Latch Enable (EOP1)                       |  |  |  |  |

|                 |     | 13 PLA 2 O/P Latch Enable (EOP2)                       |  |  |  |  |

|                 |     | 14 PLA 3 O/P Latch Enable (EOP3)                       |  |  |  |  |

|                 |     | 15 Not Used                                            |  |  |  |  |

| D0-D7           | I/O | Bidirectional 8-bit data bus.                          |  |  |  |  |

Table 2.1: NJIT PLD Pin Functions.

|                  | 1 = 7 = - |                                                                                |

|------------------|-----------|--------------------------------------------------------------------------------|

| PIN              | I/O       | FUNCTION                                                                       |

| $\overline{CS}$  | Ī         | Chip Select. A low on this pin enables the PLD to be                           |

|                  |           | read or written.                                                               |

|                  | (         | The SRAM can be serially initialized irrespective of the                       |

|                  | 1         | status of this pin.                                                            |

|                  | }         | The state transitions of the PLA cells are not affected                        |

|                  |           | by this signal.                                                                |

| CLK              | I         | Master Clock. All internal clocks are derived from this                        |

|                  |           | master clock. A clock signal meeting the clock specifi-                        |

|                  |           | cations and must always be applied to this pin. Under                          |

|                  |           | no circumstances should it be gated off.                                       |

| $\overline{POR}$ | I         | Power on reset. This active low signal is used to reset                        |

|                  |           | the chip at power up (and at other times as well). It                          |

|                  |           | results in a request of reprogramming of the SRAM.                             |

|                  |           | Power on reset                                                                 |

|                  |           | 1. Resets the SRAM initialization circuitry such that                          |

|                  |           | it is ready to be reprogrammed at bit location 0.                              |

|                  |           |                                                                                |

|                  |           | 2. Resets EOI to low state.                                                    |

|                  |           | 3. Resets all the bits in the status register.                                 |

|                  |           | 4. Resets all internal flip-flops (PLA cell input, out-                        |

|                  | ļ         | put and feedback latches).                                                     |

|                  |           |                                                                                |

| $\overline{RD}$  | I         | Read. This active low signal together with $\overline{CS}$ and $\overline{WR}$ |

|                  |           | control the data transfer. When $\overline{CS}$ is low, a low $\overline{RD}$  |

|                  |           | would read out the data from the source whose address                          |

|                  |           | appears on the address lines.                                                  |

| $\overline{WR}$  | I         | Read. This active low signal together with $\overline{CS}$ and $\overline{RD}$ |

|                  |           | control the data transfer. When $\overline{CS}$ is low, a low $\overline{WR}$  |

|                  |           | would write in the data from the source whose address                          |

|                  |           | appears on the address lines.                                                  |

|                  | •         | 1                                                                              |

Table 2.1 NJIT PLD Pin functions.

,

| PIN  | I/0 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                        |

|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDI  | I   | Serial data input. When ESDI is high and EOI low the<br>serial data on this pin is written to the SRAM. The 2960<br>bit serial data stream provided by an external device is<br>latched at the rising edge of the RCLK.                                                                                                                                                         |

| SDO  | 0   | Serial data output. When ESDO and EOI are high the<br>SDO pin serially outputs the contents of the SRAM<br>Each positive edge of the RCLK latched the next bit on<br>this pin.                                                                                                                                                                                                  |

| ESDI | I   | Enable serial data input. This active high signal set<br>up the SRAM for serial programming. If EOI is high<br>(ie SRAM has been initialized since last reset) the ESD<br>pin status is ignored. It is then necessary to reset the<br>chip again to reprogram the SRAM.                                                                                                         |

| ESDO | I   | Enable serial data output. This active high signal allow<br>a serial read out of the SRAM when EOI is high. Seria<br>data bits are shifted out at the rising edge of the RCLK                                                                                                                                                                                                   |

| RCLK | 0   | Request Clock. It has two fold purpose. When ESD<br>is high and EOI low it acts as a request clock to an<br>external device which supplies serial data for SRAM<br>programming. The data on the SDI pin is latched a<br>the rising edge of RCLK.<br>When ESDO and EOI are both high the RCLK latche<br>out the serial data from the SRAM on the SDO pin a<br>every rising edge. |

| EOI  | 0   | End of initialization. This signal is set high when all<br>the 2960 bit nodes of the SRAM have been programmed<br>after a reset. Resetting the chip sets EOI low.                                                                                                                                                                                                               |

| INTR | 0   | Interrupt. This signal is set high when a of the process<br>ing sequence in any PLA cell is completed. The proces<br>sor must then read the output of a predetermined cel<br>or check the status register to determine which PLA cel<br>has finished its processing. A read from the appropriate<br>cell or the status register will reset this line.                           |

Table 2.1 NJIT PLD Pin functions.

•

### 2.4 Timing Waveforms

This section describes the basic timing sequences for the read, write power on reset, serial data write and read operations. The PLD connects as an asynchronous device to the  $\mu$ P bus.

#### Read Cycle

The microprocessor starts the read cycle by driving the address on the address lines, fig 2.4a. The address is decoded externally to generate the  $\overline{CS}$  signal. A low  $\overline{CS}$ sets up the PLD for an I/O operation. When  $\overline{RD}$  goes low the PLD outputs 8 bit data, from the address specified on A0-A3, on the data bus. The address must remain stable and  $\overline{CS}$  active while the data is being read.

#### Write Cycle

The microprocessor starts the write cycle by driving the address on the address lines, fig 2.4b. The address is decoded externally to generate the  $\overline{CS}$  signal. A low  $\overline{CS}$  sets up the PLD for an I/O operation. The processor outputs the data on the data bus and sets  $\overline{WR}$  low. The PLD latches this 8 bit data, at the address specified on A0-A3, on the data bus. The address must remain stable and  $\overline{CS}$  active while the data is being written.

#### Power On Reset

At power on the  $\overline{POR}$  must be held low for a duration of at least 10ms to properly initialize the chip, figure 2.5a. The reset signal may be applied at any other time

<a>) Read Cycle</a>

Figure 2.4 NJIT PLD Read and Write Cycles

as well and its minimum duration must be  $1\mu$ s. After a reset the SRAM has to be reprogrammed.

#### Serial Data Write

After a reset the EOI pin is set low and the SRAM has to be programmed serially. When ESDI pin is driven high the PLD generates a request clock, RCLK to serially shift in the data on the SDI pin, figure 2.5b. After the 2960 bits of the SRAM have been programmed the EOI signal goes high and RCLK is tristated. ESDI must be held high until EOI goes low. The RCLK frequency is 1/16 of the CLK frequency. The initialization time is  $16 * \frac{1}{f_{CLK}} * 2960 = \frac{48360}{f_{CLK}} secs$ .

By connecting the EOI pin to the ESDI pin of another PLD multiple PLDs may be programmed sequentially from a single serial data source.

#### Serial Data Read

The SRAM contents can be read out at any time by pulling the ESDO pin high. Serial bit stream will be shifted out on the SDO pin at each positive transition of the RCLK, see figure 2.5c. It is not necessary to read out all the 2960 bits and ESDI may be driven low before all bits have been read. However when ESDO is driven high again the serial data from the next location in the SRAM will be shifted out unless the chip has been reset.

### 2.5 Programming Model

Figure 2.6 shows the programming model of the NJIT PLD. There are four input and four output registers, one pair for each PLA cell.

| <br> |   |     |

|------|---|-----|

| PLA  | Ø | I/P |

| PLA  | 1 | I/P |

| PLA  | 2 | I/P |

| PLA  | З | I/P |

- CELL Ø Input Register

- CELL 1 Input Register

- CELL 2 Input Register

- CELL 3 Input Register

| PLA | Ø | 0/P |

|-----|---|-----|

| PLA | 1 | 0/P |

| PLA | 2 | 0/P |

| PLA | З | 0/P |

CELL 0 Output Register CELL 1 Output Register CELL 2 Output Register CELL 3 Output Register

| PLA Ø 0/P | PLA 1 0/P |

|-----------|-----------|

| PLA 2 0/P | PLA 3 0/P |

Nibble Mode 1 Register Nibble Mode 2 Register

Status Register

Figure 2.6 Programmer's model of the NJIT PLD There is a 5 bit status register. Bit 0 is set at the end of SRAM initialization. Bits P0-P3 are set if the corresponding PLA cell has finished processing. At this time the result is available in the corresponding PLA O/P register.

Each PLA cell has an extra OR term that is used to detect the end of processing, latch the result at the PLA cell O/P register and set the corresponding bit in the status register.

There is a provision for four bit data modes referred to as nibble modes. Each nibble mode register allows simultaneous reading of 4 bits from two PLA cell O/P registers. Nibble mode 1 (NM1) reads the upper four bits from the PLA cell 0 O/P register and lower 4 bits from the PLA cell 1 O/P register. Nibble mode 2 allows reading of the upper four bits from PLA cell 2 O/P register and lower four bits from PLA cell 3 O/P register.

# Chapter 3 Testing of NJIT PLD

### 3.1 Test Approach to the NJIT PLD

The NJIT PLD is a unique chip and so is its testing. Like any other PLA the NJIT PLD must pass through exhaustive production testing where in every fault is checked for. When in use the chip has the unique feature of *reprogramming*. The *personality* of the chip or in other words the circuit realization in each of the four PLA cells in the NJIT PLD may be changed at any time. This poses a unique test problem when testing the PLA cells in the NJIT PLD. The solution to this problem is equally unique and the reprogrammability of the chip is utilized to create a unified production and user test program for complete testing of the PLA cell.

The complete testing proceeds in a sequence of tests starting at power on. The chip is viewed as if partitioned into blocks and these blocks are tested either independently or together in groups. The following sections provide detailed discussion on the actual testing of the NJIT PLD in a packaged form.

## 3.2 Test Equipment for the NJIT PLD Testing

As noted earlier the NJIT PLD is tested in a completely packaged form by applying signals externally through the pins and observing the output responses. The actual application of test vectors and sensing of the outputs is done on the INTEGRATED MEASUREMENTS SYSTEMS (IMS) HS1 workstation. This comprises of a IMS 1000 LOGIC MASTER system and a VS1000 VERIFICATION STATION. The IMS 1000 connects to a computer or a terminal from which test programs can be run. The device under test is wired on a test board on the VS 1000 verification station. The Logic Master acts as a controller for the VS1000 and sends test data, clocks, power supply and acquires input data which may then be compared with reference response. More details about the IMS test system are presented in Appendix B.

## 3.3 Overview of NJIT PLD Testing

As discussed above the NJIT PLD has a unified production and user test set. This section describes the overall test scheme for the chip.

Referring to figure 2.2 the blocks of the NJIT PLD are:

- 2960 bit serial read/write static RAM for programming a circuit in each of the four PLA cells.

- Four PLA cells each with 8 inputs, 8 outputs, 4 feedback terms (through D type flip-flops). Each cell has twenty 20 input *product* terms and nine 20 input sum<sup>1</sup> terms.

<sup>&</sup>lt;sup>1</sup>The actual PLA implementation is NOR-NOR for speed considerations. Here the standard *product* and *sum* term terminology is used to refer to the input NOR and output NOR terms.

- 3. Status register with five bits. Four of these bits indicate end of processing in the corresponding PLA cells. Bit 0 is set to indicate end of initialization, that is to signal completion of the SRAM programming.

- 4. Input-Output buffers to route data to/from any of the PLA cell input, output or the status register to the external data bus.

- 5. Address decoder to select a PLA cell input or output register for reading or writing and to select the status register for reading. In addition the address decoder can also clock the output registers of each PLA and hence load the PLA cell result in its output register during testing.

- 6. Timing and control block is responsible for proper powering up of the chip and generation of internal clocks, serial data requests, serial data read and write, interrupts and other status signals such as EOI etc.

The overall chip testing involves checking of each of these blocks individually. Failure in any one block implies an overall test failure. Some blocks can be checked independently of others while some cannot be. When testing for faults in a block that cannot be checked independently the other interacting blocks are assumed to function correctly or a fault in the interacting blocks will result in a faulty response from the block being tested. However each block must be examined for all possible faults either separately or in sections along with other blocks.

Figure 3.1 shows the skeleton of the test scheme for the NJIT PLD. After powering on the initial hardware status is checked. All the inputs are either driven to the inactive state or left in hi-Z state. The status of all the outputs and the hi-Z inputs is sensed and compared.

NJIT PLD test scheme.

The status register is read next and its value is compared with expected value. Note that reading of the status register requires correct operation of the address decoder, input-output buffer and control circuitry to a certain extent. Neither of the above interacting sections can be checked just by itself. The probability of having some faults in any one or more from the status register, address decoder, input-output, or control blocks mask a fault in another block is almost zero. In general

In any interaction of two or more blocks a fault in any one block will not mask a fault in another block and vice-versa as long as these blocks interact only via signals controlling each other and do not share any data flow.

Also note that the testing of any one block in such a combination would also check out the parts of other blocks that interact with the block under test. Hence along with the status register the *End of Processing* signal generation, interrupt generation and address decoding for the status register and other blocks used in this test are also checked. All these tests will hereafter be collectively called **Status Generation** test.

The SRAM is checked next. The SRAM is checked after the status generation test because it requires more time. For a go/no-go type of test all faults that can be detected quickly must be checked first. In testing of the NJIT PLD the different checks are performed in an increasing order of their time requirements. Checking of the SRAM also tests the initialization control circuitry and bit 0 (EOI) of the status register.

Finally each of the four PLA cells is checked. Checking of the PLA cells is

the biggest challenge in the test design on which various schemes have appeared in literature. However the NJIT PLD has a unique *reprogrammable personality* and is checked differently from all the other schemes. The NJIT PLD allows a unison of user and production testing. It is unique in the aspect that it allows a *complete fault detection of all the resources from the external pins*.

Each PLA cell is tested individually. Along with the testing of each cell the interacting sections of the address decoder, input-output buffer and the control circuitry is also tested. The testing of the four PLA cells is *concurrent* but *distinct*, that is at any time each of the four PLA cells is in a different state.

More detailed testing of each block is discussed in the following sections.

## 3.4 Power On Check

The is the first test in the sequence after the chip has been powered on and applied a reset signal. All the input pins are driven inactive and if those pins which do not have any inactive states are left in high impedance or tristate condition. The state of all the output pins and the tristated input pins is noted and compared with the values indicated in the table 3.1.

| Pin Name         | I/0 | Power On Status |

|------------------|-----|-----------------|

|                  | 1   |                 |

| $\overline{POR}$ | I   | High            |

| CLK              | I   | 1MHz clock      |

| $\overline{CS}$  | I   | High            |

| $\overline{RD}$  | I   | High            |

| $\overline{WR}$  | I   | High            |

| $A_0 - A_3$      | I   | Tristate        |

| $D_{0} - D_{7}$  | I/O | Tristate        |

| ESDI             | I   | Low             |

| ESDO             | I   | Low             |

| SDI              | I   | Tristate        |

| SDO              | 0   | Low             |

| RCLK             | 0   | Low             |

| EOI              | 0   | Low             |

| INTR             | 0   | Low             |

|                  |     |                 |

Table 3.1 NJIT PLD pin status after power on and reset.

# 3.5 Status Generation Check

This check detects faults in all the circuitry associated with generation of status. The only exception is the *end of initialization* circuitry which is tested along with the static RAM. The status of the chip is indicated by the following pins and registers:

1. Status Register: The five bits in the status register indicate the end of processing for each of the four PLA cells and the end of initialization.

### EOP3 EOP2 EOP1 EOP0 EOI

Each of these bits is set to 1 on occurance of the corresponding condition.

- 2. Interrupt (INTR) Pin: The occurance of end of processing in any of the PLA cells sets the INTR line high. This indicates an interrupt request. The CPU has to poll the status register to determine which of the four PLA cells had actually finished processing. A read from the status register or the output register of the PLA cell that has finished processing will reset this request.

- 3. End of Initialization (EOI) Pin: This signal is driven high by the PLD when the SRAM has been completely loaded with PLA cell configuration data. This signal is tested in the SRAM check.

The parts or sections of the chip that would be tested are:

- 1. Status Register.

- 2. Interrupt generation and reset.

- 3. End of processing generation in each cell.

- 4. Address decoder for addresses A,B,C,D and E (Hex).

The status generation check proceeds in the following steps: (see figure 3.2)

- 1. At the outset the status register is read. All the bits in the status register must be zero to confirm that

- (a) Initialization of SRAM is not yet complete.

- (b) No PLA cell has detected end of processing.

Any deviation indicates a fault.

Figure 3.2 Status generation check

- 2. The second step is the checking of end of processing signal generation in the first PLA cell (Cell0). It proceeds as follows:

- (a) An address of 0B (Hex) is put on the address bus. This location is neither readable nor writable but has been created exclusively for test purposes. Any read or write activations at this address would be ignored by the PLD chip.

Normally the output of a PLA cell is latched onto a cell output register/buffer. The clock signal for loading the output data of the PLA cell in its register is generated in the cell itself. Each PLA cell has nine output terms out of which only eight are brought on the data bus. The extra output is used to clock the cell output latch. Thus a state detection can be implemented and the cell output latched when the cell reaches a pre-defined state. For test purposes the application of an address 0B-0E (Hex) on the address bus would enable the latching of the corresponding cell's output. The cell output latching is independent of the  $\overline{RD}$  and  $\overline{WR}$  lines and the data present on the data bus is of no interest. Thus the end of processing status generation circuitry is activated.

- (b) The next step is to check the status on the INTR pin. Latching of the cell 0 output data must also set the INTR request high.

- (c) The status register is polled now to determine which cell had actually reached end of processing. All the bits except the EOP 0 bit in the status register must be zero.

- (d) The Cell0 output register is read. This should reset the INTR pin. The resetting of the INTR pin is now checked.

- (e) Finally the status register is read again to verify that bit EOP 0 has been cleared. The status register again reads 00000.

- 3. The third step is the checking of end of processing signal generation in the second PLA cell (Cell1). It proceeds in a similar manner to the checking of EOP status generation for cell 0 except that address 0C Hex is read/written to set EOP1 and INTR signal and the Cell1 output is read from Cell Output Register at address 03 Hex.

- 4. The next step is the checking of end of processing signal generation in the third PLA cell (Cell2). It proceeds in a similar manner to the checking of EOP status generation for cell 0 except that address 0D Hex is read/written to set EOP1 and INTR signal and the Cell1 output is read from Cell Output Register at address 05 Hex.

- 5. The final step is the checking of end of processing signal generation in the fourth PLA cell (Cell3). It proceeds in a similar manner to the checking of EOP status generation for cell 0 except that address 0E Hex is read/written to set EOP1 and INTR signal and the Cell1 output is read from Cell Output Register at address 07 Hex.

This completes the Status Generation checking.

# 3.6 SRAM Testing

The static RAM is used to implement the desired circuit in the PLA cells. Each PLA cell consists of 740 programmable nodes (links or cross-points) in the input, output and feedback arrays. The total SRAM capacity is 4\*740 = 2960 bit capacity.

To keep address decoding simple and to reduce pin count of the chip the SRAM is read or written serially. This is justifiable since the SRAM needs to be read or written only once for each circuit implementation. The positive transition of the RCLK signal latches the data on the SDI pin onto the next SRAM bit location when ESDI pin is high. When ESDO pin is high the SRAM is set for serial read out and each positive transition of the RCLK signal latches the next bit on the SDO pin.

The RCLK is derived from the CLK input to the PLD by dividing it by 16. Thus the time taken to serially read or write the entire SRAM is

$$T_{SRAM} = 2960 * \frac{16}{f_{CLK}} \text{ or}$$

$$T_{SRAM} = 47360 * T_{CLK}$$

The time taken to read or write the SRAM is 47ms at a clock frequency of 1MHzand 4.7ms at 10MHz.

The layout of the SRAM cells is interspersed with the layout of the input, output and feedback arrays. This justifies a straightforward testing of the SRAM rather than designing any specially designed or optimized tests. The SRAM tests include the following:

- 1. Each bit of the SRAM must be programmable to store values 0 and 1. This checks for any stuck at 0 or stuck at 1 faults.

- Each bit location of the SRAM must be capable of being set or reset independently of the neighbouring<sup>2</sup> bits.

<sup>&</sup>lt;sup>2</sup>The neighbour criterion is determined from the physical layout of the SRAM cells and not necessarily according to the read or write sequence.

3. The SRAM read and write control circuitry must also be checked proper operation and timing relationships. The control circuitry includes the RCLK generator, SRAM address counters and read write buffers.

To perform all the above checks a 1010... pattern is shifted into the SRAM and then read out serially to verify correct programming. Next a complimentary pattern 0101... is shifted into the SRAM and then verified by another read out . Each of these two pattern result in a **checker board** pattern being programmed in all the four PLA cells as shown in figure 3.3. These checker board patterns will check the following sections of the PLD:

- SDI and SDO pins: Any stuck at 0 or stuck at 1 fault on the SDI or SDO pins will result in a fixed output voltage at the pin SDO when the SRAM is read. The s-a-0 or s-a-1 fault on SDI will result in the programming of the SRAM with all 0s or all 1s. Hence the SRAM read out will be a fixed voltage.

- 2. ESDI and ESDO pins: The faults detected with the SRAM read and write enable circuitry are detected in three steps:

- (a) A s-a-0 on the ESDI or ESDO will never allow reading or writing of the SRAM. This will result in a fixed voltage level on the SDO pin when attempting to read the SRAM.

- (b) A s-a-1 on the ESDI would result in an unintentional programming of the SRAM immediately after power on. Once all the bits of the SRAM have been written (erroneously) to the reprogramming of the the SRAM is inhibited till a reset. Thus in the current test the checker board pattern will never get written to the SRAM because of some random pattern

Figure 3.3 PLA Cell Configuration with Checkerboard SRAM Programming.

already being there. Further a s-a-1 on the ESDI will result in appearance of RCLK pulses immediately after power on and EOI pin will go high after all the bits in the SRAM have been programmed. This would be detected by the power on check.

- (c) A s-a-1 on the ESDO is detected by the appearance of RCLK signal right after power on and shifting out of the random SRAM data on the SDO pin. This would be detected by the power on check.

- 3. RCLK pin: Any s-a-0 or s-a-1 faults on the RCLK pin would become evident while programming the SRAM with the checker board patterns. Any such fault would inhibit programming and readout. The ÷16 relationship between the RCLK and the CLK input to the chip can also be checked for at this time.

- 4. EOI status circuitry: The EOI pin must initially be low (as checked by the power on tests) and then go high after the programming is complete. At this point any s-a-0 fault on the EOI pin would be detected. Note that a s-a-1 fault on the EOI would have been detected by the power on check. Also after the SRAM has been initialized the EOI bit in the status register would have been set. This bit remains set till a reset occurs.

- 5. SRAM faults: The checking of the faults associated with the SRAM are now described.

- (a) Stuck at 0 and stuck at 1 faults: The checker board pattern 1010...

is first written and then read from the SRAM. This checks for the sa-0 faults on half of the bit cells (which have been programmed with

1s). The other half (those programmed with 0s) are checked for s-a-1 faults because any of these faults would disrupt the regularity of the 1010... pattern. Next the chip is reset and a complimentary pattern of the above, 0101..., is written to the SRAM. The SRAM contents are then read again. Any s-a-0 faults in the bit cells programmed with 1s (which had earlier been programmed with 0s and tested for s-a-1) or s-a-1 faults on bit cells programmed with 0s (earlier programmed with 1s and tested for s-a-0) would disrupt the regularity of the 0101... readout pattern.

- (b) Bridging faults: Due to checkerboard pattern programming every bit cell programmed with 0 is surrounded by bit cells programmed with 1s and in turn every bit cell programmed with 1 is surrounded by bit cells programmed with 0s any bridging faults between the adjacent cells will disrupt the regularity of the checkerboard pattern and will get detected on readout.

- 6. Reset circuitry: After programming the 1010... pattern the chip is reset and the status on the out put pins checked again as in the power on check. The status generation test are performed again to verify the effects of reset. Next the 0101... pattern is serially loaded onto the SRAM and all the above tests are repeated.

To sum up the SRAM check tests the following circuits in the chip:

- 1. SRAM bit cells.

- 2. SRAM read and write pins (SDI and SDO).

- 3. SRAM read and write control (ESDI, ESDO, RCLK).

4. EOI status generation (EOI pin and EOI bit in the status register).

# Chapter 4 PLA Cell Testing

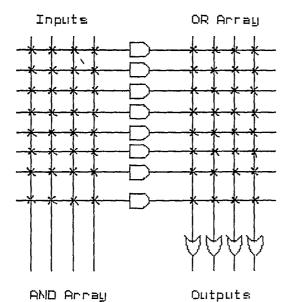

# 4.1 Faults in PLAs

There can be three types of faults in PLAs [1-3].

#### 4.1.1 Stuck At Faults

These faults result from a metal, polysilicon or diffusion path being shorted to ground or positive supply voltage. Even an open circuit manifests as a stuck at fault, for example a open circuit gate can appear as a stuck at 0 fault. Also a short between the source and drain may be construed as a stuck at 1 or stuck at 0 on the drain of a NMOS and PMOS transistor respectively. Any shorting of the polysilicon gate to the drain or source due to defects in the SiO<sub>2</sub> layers will also effect in a stuck at fault.

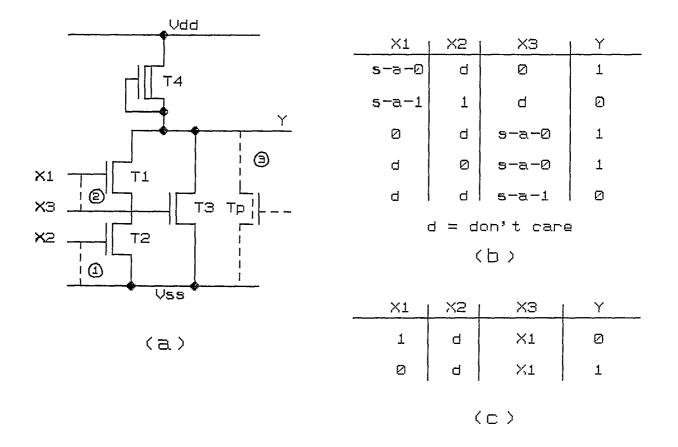

A stuck at fault may or may not propagate along the circuit network [4-8]. Hence test vector sets must allow for propagation of all possible stuck at faults. A stuck at fault may pass through several polarity inversions at each transistor stage. Figure 4.1 shows a 2-1 input AND-OR-INV gate and propagation of stuck at faults on the inputs.

## 4.1.2 Bridge Faults

Bridge faults are caused by shorting of two or more metal, polysilicon or diffusion lines. As noted above certain types of shorts such as those between a gate and source manifest as stuck at faults. For testing purpose bridge faults represent the abnormal connection of two or more different inputs that results in a faulty output different from the output because of a stuck at fault Figure 4.1 also shows a bridge fault and the resulting response.

#### 4.1.3 Cross Point Faults

A crosspoint fault is caused by the abnormal absence or presence of a diode or transistor. For example a missing transistor T3 in the circuit of figure 4.1 is a crosspoint fault. The presence of an extra parasitic transistor  $T_P$  also constitutes a crosspoint fault. Usually cross point faults arise in circuits using grid or array models such as memories, PLAs etc.

The cross point fault in the above example is equivalent to a stuck at 0 fault on the gate of transistor T3. However a parasitic transistor across the source and drain of T3 would be harder to detect especially if it turned on and off with time.

# 4.2 Testing of PLAs

The testing of PLAs is a unique problem of its own. Unlike the SSI and MSI circuits there is no standard way of testing a PLA. However the regular and structured architecture of PLAs allow their testing with simpler schemes than other LSI and

Figure 4.| Faults in PLAs. (a) 1: Stuck at fault, 2: bridge fault and 3: cross point fault. (b) Output response for stuck at faults on input. (c) Output response for a bridge fault. Note how the bridge fault changes the circuit's logic to an inverter.

VLSI devices.

A PLA could be tested by the manufacturer or the user. These two groups have markedly different test philosophies, goals and equipment. The different aspects of production and user testing are now discussed.

#### 4.2.1 Production Testing

The production testing must be exhaustive. It must check for all the types of faults that may result due to processing and packaging irregularities. The simple way of testing a PLA is straightforward but rather inefficient. A look at the simple testing technique will highlight the many a uniqueness of PLA testing. To test the PLA well we must excite all faults and check the output for incorrect responses. However most PLAs are one time programmable. This means that once we *burn* a circuit onto a PLA we cannot alter it. This is indeed the severest limiting factor for the straightforward testing technique. The fault coverage of such a test would depend upon the fraction of total nodes used in *burning* of the test circuit onto the PLA. This fraction is in turn dependant on the complexity of the circuit *burned* in. Greater complexity would require generation of more complex (with respect to size as well as sequence) test vectors. For any circuit's implementation on a PLA the following rule applies:

Any non trivial circuit implementation cannot have a node coverage greater than 50% in the INPUT<sup>1</sup> array.

<sup>&</sup>lt;sup>1</sup>Different PLA schemes use different implementations such as AND-OR, NAND-NAND, NOR-NOR etc. The general form used here is INPUT-OUTPUT array.

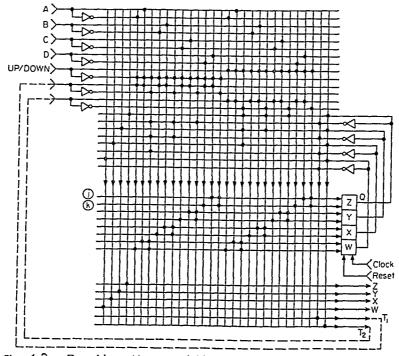

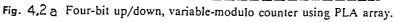

This is true because no non trivial<sup>2</sup> sum or product term can have a signal and its complement together. Hence the test circuit realization can use a maximum of 50% nodes in the INPUT array. Therefore the fault coverage of the INPUT array cannot exceed 50%. The node coverage (and hence fault coverage) of the OUTPUT array depends upon the number of INPUT terms in the OUTPUT array. For a very small number of INPUT terms it is possible to have 100% node coverage but this is very rare. Usually a PLA will have 8-24 INPUT terms per OUTPUT gate. Fig. 4.2 illustrates the node coverage possible with some PLAs implementations of medium complexity circuits. The density of dots in the AND and OR arrays gives an idea about the node coverage. This explains why simple testing of PLAs is rarely done by a user.

The above discussion highlights that it is impossible to test with 100% node coverage on a one time programmable PLA. However a manufacturer must test his product completely before marketing. Usually a manufacturer would take a sample of chips from a production run. Each of these chips would have a different *pattern* burned onto them so that they collectively cover all nodes. Different sets of the sampled chips would be tested with members of each set collectively covering all faults. This would give a statistical yield for the production run. A manufacturer might also test pre-packaged chips using wafer probes and other test equipment. Wafer probing is done when packaging costs are high and yield is relatively low. Wafer probe also helps in fault location and determination of fault causes. However the wafer probe method is quite delicate, expensive and time consuming. Hence it is desirable to be able to test a chip to the greatest possible extent from the external

<sup>&</sup>lt;sup>2</sup>A non trivial sum or product term is one that does not have an output fixed at 0 or 1 irrespective of the input

Fig. 4,2b Bit-serial adder/subtracter using PLA format (4-bits) PLA implementation with *D*-type flip-flops only, PLA implementation with shift registers substituted in the feedback circuit.

Adapted from "MOS/LSI Design and Application", William N. Carr & Jack P. Mize Texas Instruments Electronics Series, McGraw Hill, 1972. pins.

#### 4.2.2 User Testing of PLAs

The impossibility of testing every node of a one time programmable PLA was discussed above. In practice it is not even necessary for a user to test all the nodes of the PLA. A user would normally *burn* in a circuit of his own application. After that he is concerned only with the fault free working of his circuit and it is immaterial whether any faults develop in the unused resources<sup>3</sup> of the PLA.

To aid the complete testing of the user implemented portion of the PLA it is recommended that the user *burn* additional redundancy or test circuitry along with his own circuit. The redundancy or the test circuitry is then used to check itself and the user circuit. Many schemes of creating a testable PLA design have been proposed [9-13]. These include error detection and correction encoding of outputs, extra terms in the output function to create *disjoint* terms etc.

# 4.3 PLA Cell Testing in the NJIT PLD

A user normally *burns* some redundancy or test circuitry along with the actual circuit on the PLA. However the NJIT PLD may be reprogrammed at will. Each reprogramming may be intended to result in a different circuit realization. So the user might have to design a different test circuit for each application. Some times the new design may even be adaptive and indeterministic beforehand. This would make testable design very formidable.

<sup>&</sup>lt;sup>3</sup>The unused input lines, output lines and other gates etc. are collectively referred to as the unused resources of the PLA.

However the NJIT PLD exploits reprogrammability to permit enhanced testing. Reprogramming of the SRAM matrix to yield a new circuit realization at will allows comprehensive production as well as user testing for a complete fault coverage. This is a unique unison of production and user testing and both tests are identical. The user is freed from creating a special design for testability and generating test vectors. The production testing is made much more economical because all faults are tested from the pins. Wafer probing is required only for location of faults due to processing imperfections. This reduces the time and costs of wafer probing. Packaged chips are completely testable for fault detection at any time.

The detailed testing of the PLA cell is discussed in the next sections. Along with the testing of the PLA cells sections of other interacting circuitry such as address decoder, input-output buffer and timing and control circuitry are also tested.

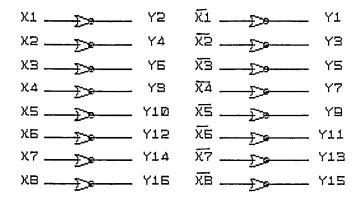

## 4.3.1 Taxonomy and Nomenclature of PLA Cell Sections

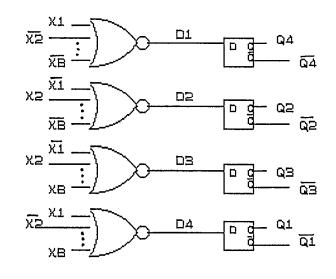

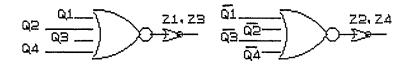

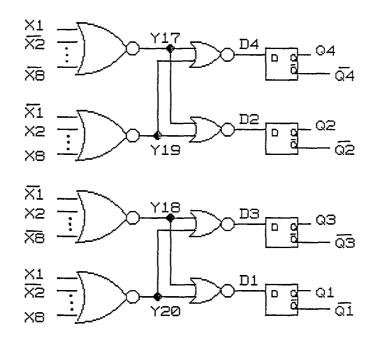

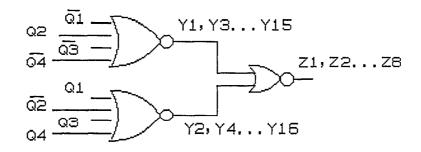

Figure 4.3 shows a complete schematic of a PLA Cell. The PLA is implemented as a NOR-NOR matrix. These will henceforth be referred to as INPUT NOR and OUTPUT NOR (abbreviated as I/P NOR and O/P NOR) matrices. The I/P NOR matrix has 20 NOR gates. Each gate has 24 *programmable* inputs (8 inputs, 8 complementary of inputs, 4 feedback Lines and 4 complementary feedback Lines). The O/P NOR matrix has 8 gates each with 20 *programmable* inputs. Each input to the O/P NOR matrix gate corresponds to a output of an I/P NOR gate.

The feedback is through 4 D type flip flops. The inputs and outputs of these flip flops constitute the FEEDBACK matrix.

The inputs to the I/P NOR matrix are called X Inputs. Thus  $X_1X_2...X_8$  are the inputs to the PLA cell. These are latched from the external data bus  $D_0 - D_7$

Figure 4.3 Naming of the different PLA Cell sections

to the Cell Input Latch of the PLA cell. Hence any test vector for the PLA cell check is a set of 8 elements in the form

$$X = \{X_1 X_2 \dots X_8\}$$

where  $X_i = 0$  or 1. The 8 input Lines and their 8 complements are collectively referred to as the X Array or the X Lines. Thus the X Array has 16 elements whereas there are only 8 X Inputs.

The output of each 24 I/P NOR gate run on metal Lines across the chip. These outputs of the I/P NOR gates are called Y Lines and are collectively referred to as Y Array. The status of these Y Lines in response to a test vector

$$X = \{X_1X_2...X_3\}$$

is given by  $Y = \{Y_1Y_2...Y_{20}\}$

where  $X_i, Y_i = 0$  or 1.

The 8 output Lines are also called Z Lines. These form an 8 element Z Array

$$Z = \{Z_1 Z_2 ... Z_8\}$$

where  $Z_i = 0$  or 1.

The feedback is through 4 D type flip flops. The inputs to these flip flops are called the D Lines and constitute a 4 element D Array such that

$$D = \{D_1 D_2 ... D_4\}$$

where  $D_i = 0$  or 1.

There are four normal (Q) and four complementary  $(\overline{Q})$  outputs from the D flip flops. These are collectively referred to as Q Lines and constitute a 8 element Q Array such that

$$Q = \{Q_1 \overline{Q_1} \dots Q_4 \overline{Q_4}\}$$

where  $Q_i = 0$  or 1.

Table 4.1 summarizes all these notations.

## 4.3.2 General Test Sequence

The test sequence for the PLA cell testing consists of the following steps.

- 1. Reset the PLD chip and program the SRAM so as to realize a test circuit configuration in each PLA cell.

- Apply one or more test vectors on the X Lines and obtain the response from the Z Lines.

- 3. Compare the obtained response with the expected response and check for errors.

#### 4.3.3 Test Length

The total length of the test depends upon various factors. It also depends upon the test equipment and apparatus set up times. However the test time measured herein will be the time used exclusively for the checking of the PLA cell. This time depends upon:

- 1. PLD reset time  $(T_{RESET})$ .

- 2. SRAM read and write times  $(T_{SRAM})$ .

- 3. Total number of test vectors. The time spent on applying a test vector to the PLA cell and obtaining the response is

$$T_{TV} = T_{WR} + T_{RD}$$

| Group Name                | Symbolic Represen-<br>tation                 | Remarks                                                                                                |  |

|---------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

|                           |                                              |                                                                                                        |  |

| I/P NOR Ma-<br>trix       |                                              | Consists of 20 INPUT NOR gates each with 24 programmable inputs.                                       |  |

| O/P NOR<br>Matrix         |                                              | Consists of 8 OUTPUT NOR gates each with 20 programmable inputs.                                       |  |

| FEEDBACK<br>Matrix        | ·                                            | Consists of the four feedback flip flops and their input and output matrices.                          |  |

| I/P Array or<br>I/P Lines | $X = \{X_1 X_2 X_8\}$                        | This is the 8 bit input to the PLA Cell.<br>This comes from the data bus $(D_0 - D_7)$<br>Lines.       |  |

| X Array or<br>X Lines     | $X = \{X_1 X_2 \dots X_{16}\}$               | These are the 8 inputs and their comple-<br>ments. Thus the INPUT Array is a subset<br>of the X Array. |  |

| Y Array or<br>Y Lines     | $Y = \{Y_1 Y_2 X_{20}\}$                     | These are the 20 outputs of the INPUT NOR gates.                                                       |  |

| Z Array or<br>Z Lines     | $Z = \{Z_1 Z_2 Z_8\}$                        | These are the 8 outputs of the OUTPUT NOR gates.                                                       |  |

| D Array or<br>D Lines     | $D = \{D_1 D_2 D_4\}$                        | These are the 4 inputs to the D type flip flops.                                                       |  |

| Q Array or<br>Q Lines     | $Q = \{Q_1\overline{Q_1}Q_4\overline{Q_4}\}$ | These are the four normal (Q) and four complementary $(\overline{Q})$ outputs from the D flip flops.   |  |

Table 4.1: PLA Cell Sections

therefore  $T_{test} = T_{Reset} + 2 * T_{SRAM} + n * (T_{WR} + T_{RD})$  where n is the number of test vectors in a test. The total time to test the chip is the sum of times for all the tests.

The reset time for the chip is fixed at 1ms. The SRAM read and write times are also fixed and depend upon the CLK frequency. At 10MHz the read or write time for the SRAM is 4.7ms. Hence the test design challenge has two aspects:

- Design of such PLA configurations that permit a wider fault coverage for each implementation. Thus every programming of the SRAM should be designed to result in a circuit that checks for maximum number of faults in the PLA cell.

- 2. Minimization of total number of test vectors.

A comparison of the test times must be made when there are different and alternative ways to test. It must be kept in mind that the time taken to reprogram the SRAM is greater than of a write-read cycle by an order of 10000.

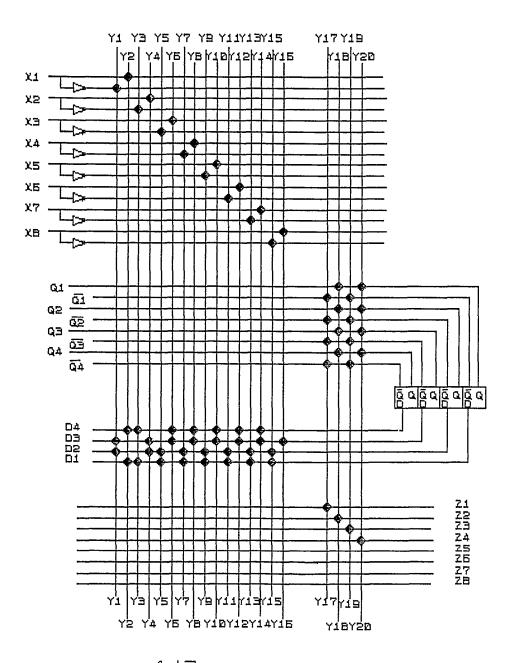

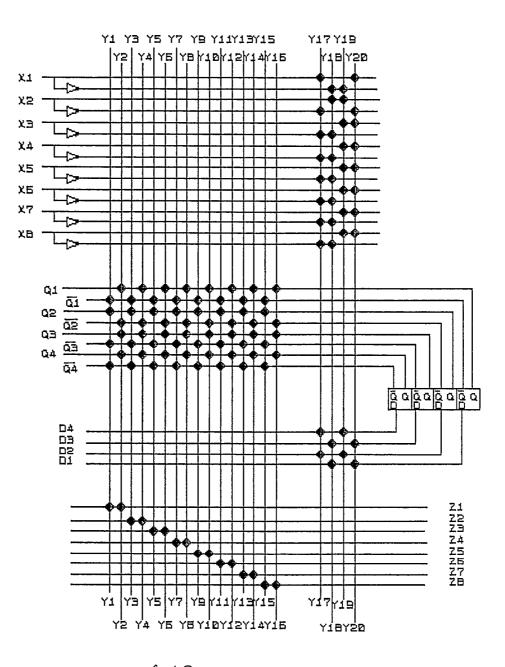

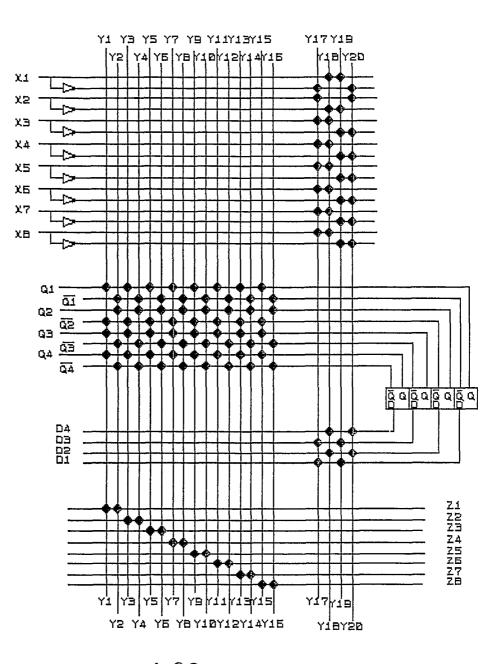

# 4.4 Test 1 (Testing of the X,Y and Z Arrays)

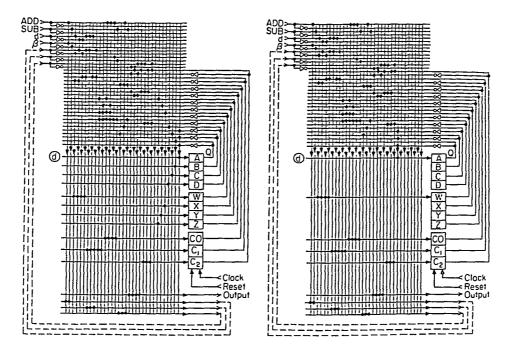

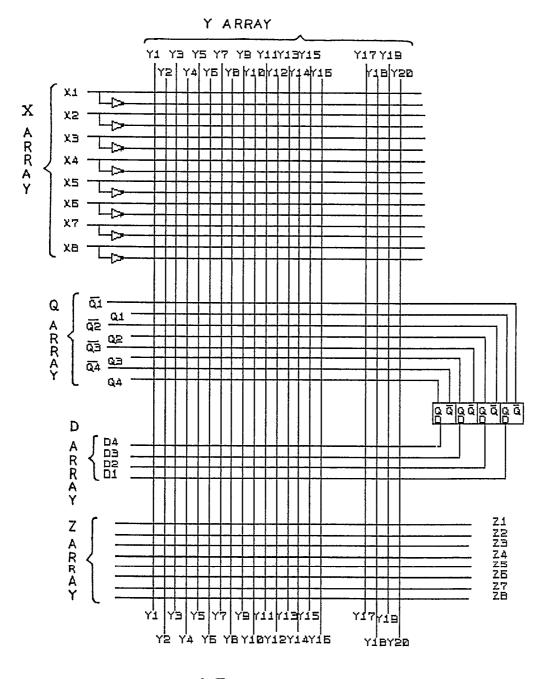

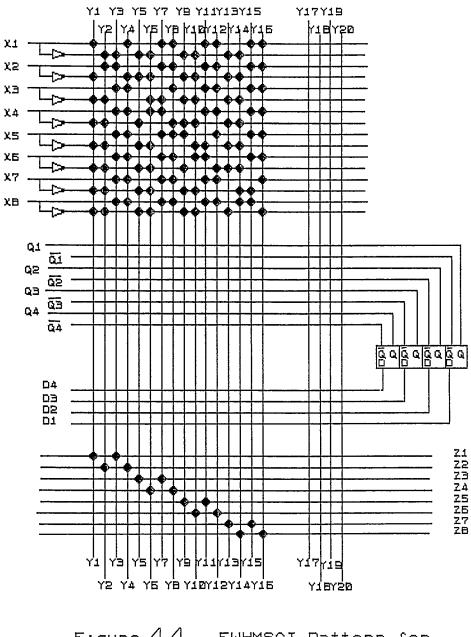

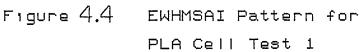

The first test involves a programming pattern that would detect s-a-0 and s-a-1 on the X Lines, s-a-0, s-a-1 and bridge faults on the Y Lines and s-a-0, s-a-1 and bridge faults on the Z Lines. The first step is loading of a special pattern into the SRAM. This pattern is equal weightage, half matrix, single activation and interleaved (abbreviated as EWHMSAI pattern), see figure 4.4. The characteristics of this pattern that aid testing are:

- Equal Weightage: All the X Lines are loaded the same. So are all the Y

Lines and all the Z Lines. The equal loading makes the transient and heating

effects be distributed along the chip area and minimizes spurious faults and

other irregularities.

- 2. Half Matrix: As discussed in a previous section the INPUT NOR matrix cannot have a node coverage greater then 50%. The EWHMSAI pattern has the maximum node coverage of 50%. This is very advantageous in testing of cross point open faults since it is possible to test for all crosspoint faults with *two* programmings of the SRAM.

- 3. Single Activation: Single activation implies that in each of the X, Y and Z arrays only one line is active (high or low) at any time and all the rest are complementary. This is very essential for bridge fault detection.

- 4. Interleaving: Two adjacent signals that are input to the same gate can mask each other's bridge faults. Hence no two Y Lines form inputs to the same gate.

Design of the EWHMSAI Pattern: For a PLA with n inputs (including the complementary inputs as well) the EWHMSAI pattern will cover (n\*n)/2 nodes in the Input matrix and (n\*m)/2 nodes in the Output matrix where the PLA has m outputs. This pattern is derivable for an even number of X inputs (not including the derived  $\overline{X}$  inputs). For PLAs having odd X inputs two even subsets of the inputs may be considered such that they together cover all inputs. The complementary of the EWHMSAI pattern shown in figure 4.6 is also an EWHMSAI pattern and is used to check the other (n\*n)/2 and (n\*m)/2 nodes in the Input and Output matrices

with the same test vectors as will be derived for the first EWHMSAI pattern.