New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

1-31-1991

# A machine vision system with remote host

Chieyeon Jason Chen New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Chen, Chieyeon Jason, "A machine vision system with remote host" (1991). *Theses*. 2443. https://digitalcommons.njit.edu/theses/2443

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

# ABSTRACT

Title of Thesis: A Machine Vision System with Remote Host Chieveon Jason Chen, Master of Science in Electrical Engineering, 1991

Thesis directed by: Dr. Anthony Robbi

Department of Electrical and Computer Engineering

The modem plays an important role in data communication using the Public Swiched Telephone Network. In this thesis, the modem function is merged into a low cost machine vision system based on the Motorola 68HC11 Evaluation Board. The system comprises the intelligent machine vision controller and a remotely located host computer, such as an IBM-PC. It supports extra long distance communication capability so that the controller and the host can be anywhere in the world where there is a telephone line. Because of the limit of a 2400 bps modem, software data compression is implemented here to save transmission time.

# A MACHINE VISION SYSTEM WITH REMOTE HOST

by

Chieyeon Jason Chen

Thesis submitted to the faculty of the Graduate School of the New Jersey Institute of Technology in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering 1991

# APPROVAL SHEET

## Title of Thesis: A MACHINE VISION SYSTEM WITH A REMOTE HOST

### Name of Candidate: CHIEYEON JASON CHEN MASTER OF SCIENCE IN ELECTRICAL ENGINEERING, 1991

#### Thesis and Abstract Approval:

Dr. Anthony Robbi, Advisor Associate Professor

Date

### Signatures of other members of the thesis committee

Dr. C. Manikopoulos Associate Professor Date

Dr. E. Hou Assistant Professor

Date

-----

# VITA

| Name: Chieyeon Jason Chen                          |           |          |                |

|----------------------------------------------------|-----------|----------|----------------|

| Address                                            |           |          |                |

| Degree and date to be conferred: M.S.E.E., 1991    |           |          |                |

| Date of birth:                                     |           |          |                |

| Place of birth:                                    |           |          |                |

| Collegiate institutions attended                   | Dates     | Degree   | Date of Degree |

| National college of Marine Science and technology, | 9/76-5/80 | B.S.E.E. | May, 1980      |

| Taiwan, R.O.C.                                     |           |          |                |

| New Jersey Institute of Technoloy                  | 9/88-1/91 | M.S.E E  | Jan, 1991      |

Major Electrical and Computer Engineering Position held: Engineer

# ACKNOWLEDGEMENT

I am very grateful to Dr. Anthony Robbi, my advisor, for his continued support and guidance during this thesis. I would like to thank Dr. Manikopoulos for his providing research equipment. Mr. Bob Dillon helped the team to write the VGA program (called IMAGE) which shows the CCD image and the status of the analog input levels and control switches. Thanks also go to Mr. Xiao-Fang Qi, Mr. Mirko Delgado, and Mr. Hsuch-Chung Feng for their help.

# Contents

| 1 | Inti | oduction                                    | 1   |

|---|------|---------------------------------------------|-----|

|   | 1.1  | Role of the Modem in Machine Vision Systems | 1   |

|   | 12   | Machine Vision System Developed at NJIT     | 2   |

|   | 1.3  | Thesis Description                          | 2   |

| 2 | Gei  | eral System Description                     | 4   |

|   | 2.1  | System Profile                              | 4   |

|   | 2.2  | M68HC11 Evaluation Board                    | 5   |

|   | 2.3  | Introduction to Modem Interface             | 7   |

| 3 | Inti | oduction to Modem Theory                    | 9   |

|   | 3-1  | Modem Fundamentals                          | 9   |

|   |      | 3.1.1 Modulation                            | 10  |

|   |      | 3.1.2 Connection Modes                      | 12  |

|   |      | 3.1.3 Channel Usage Conventions             | 1.1 |

|   |      | 3.1.4 Frequency Modulation                  | 15  |

|   |      | 3.1.5 Phase Modulation                      | 6   |

|   |                | 3.1.6    | Two-level Phase Shift Keying                      | 17 |

|---|----------------|----------|---------------------------------------------------|----|

|   |                | 3.1.7    | Quadrature (Four-Phase) PSK                       | 18 |

|   |                | 3.1.8    | Differential Phase Shift Keying                   | 19 |

|   |                | 3.1.9    | Quadrature Amplitude Modulation                   | 20 |

|   | 3.2            | Intro    | luction to Modem Chip                             | 22 |

|   |                | 3.2.1    | Description                                       | 22 |

|   |                | 3.2.2    | QAM Modulation/Demodulation                       | 23 |

|   |                | $3.2\ 3$ | Passband Filters and Equalizers                   | 23 |

|   |                | $3\ 2.4$ | Parallel Bus Interface                            | 23 |

|   | 3.3            | Serial   | Input / Output                                    | 24 |

|   | 3 4            | Introd   | luction to Hayes modem                            | 21 |

| 1 | $\mathbf{Sys}$ | tem D    | esign                                             | 26 |

|   | 11             | Hardy    | vare Design                                       | 26 |

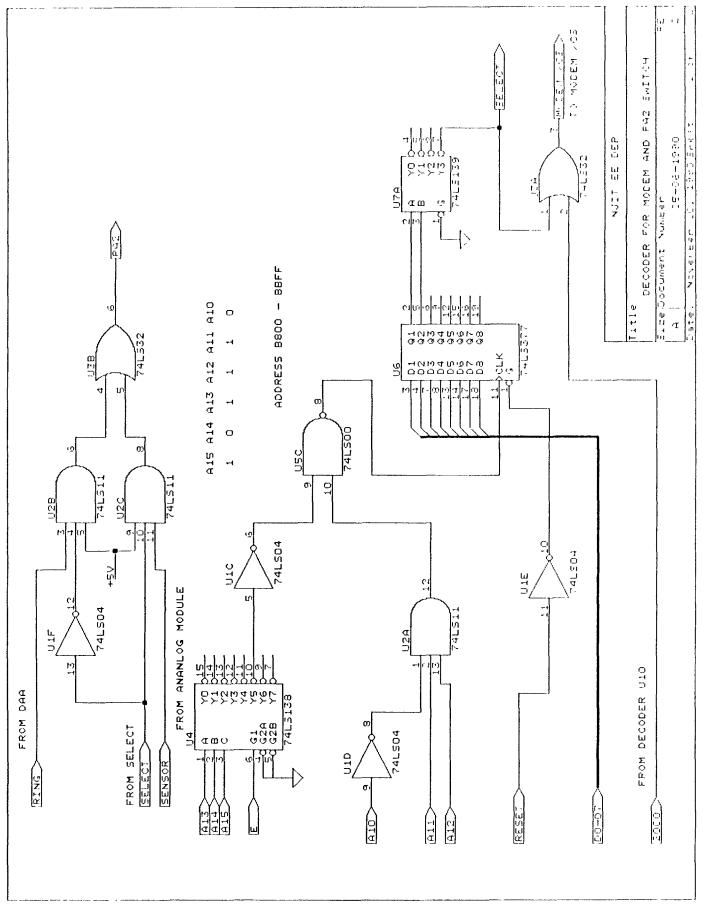

|   |                | 411      | Memory Decoder And Modem Decoder in 68HC11        | 27 |

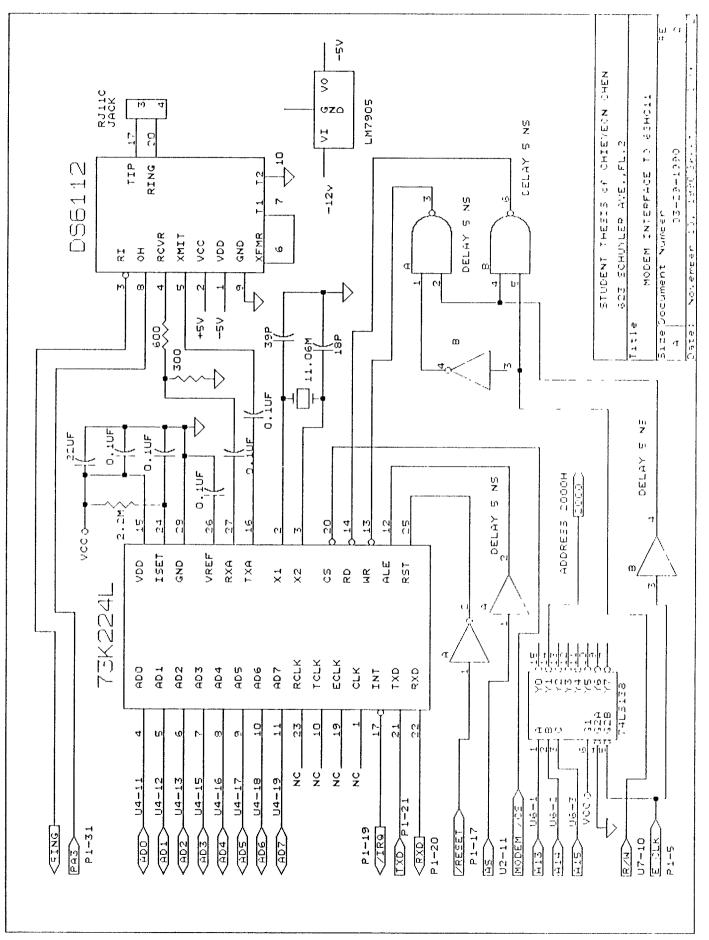

|   |                | 4 1.2    | Modem Chip Hardware Interface with 68HC11 and DAA | 29 |

|   | 4 2            | Softwa   | are Design                                        | 35 |

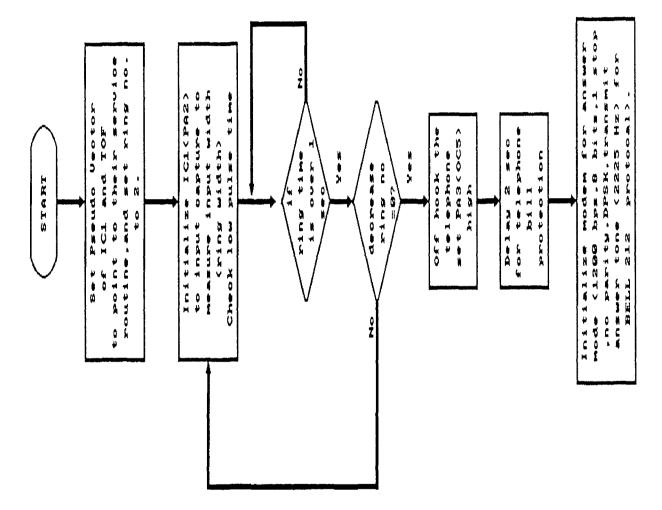

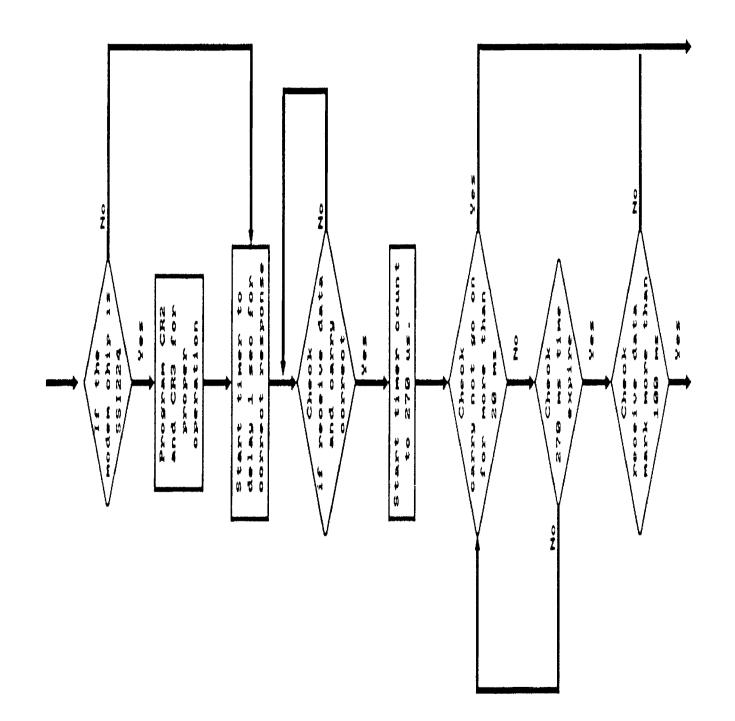

|   |                | 4.2.1    | Controller Firmware Design                        | 35 |

|   |                | 4.2.2    | PC Side Software and Firmware Design              | 41 |

|   |                | 4 2.3    | Startmodem Command used in the thesis             | 19 |

| 5 | Sys            | tem A    | nalysis of Limits and Performance                 | 52 |

|   | 5.1            | Image    | transmission                                      | 52 |

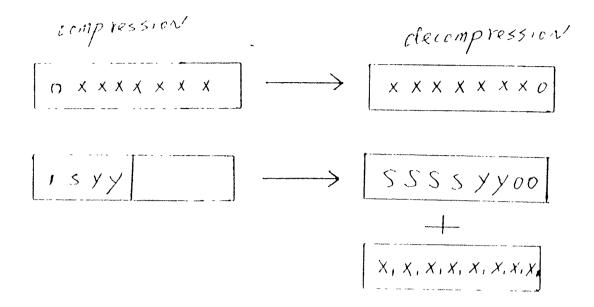

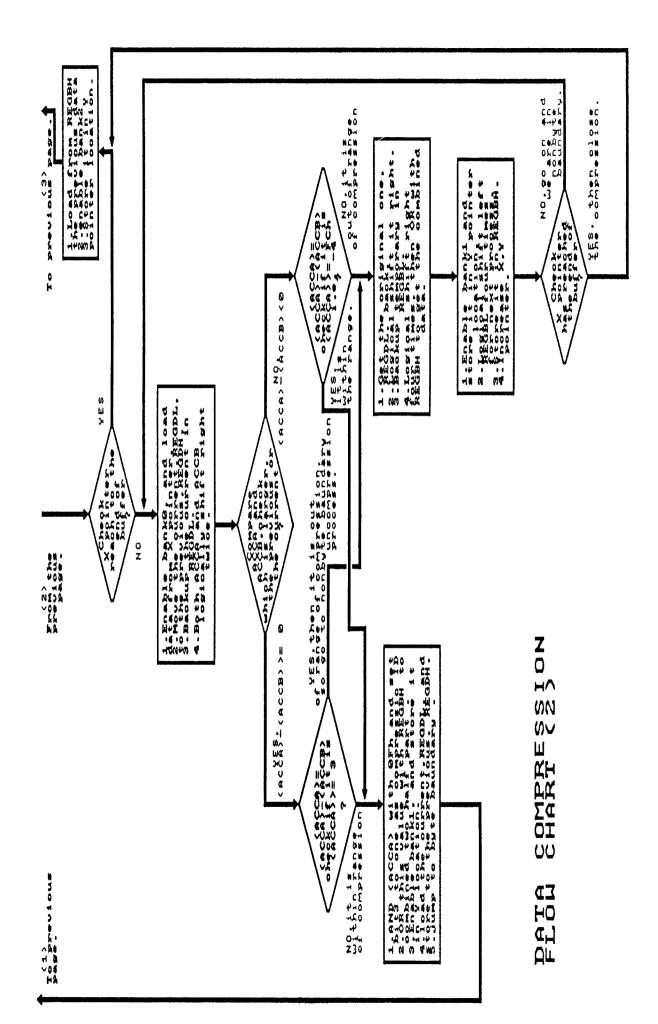

|   | 5.2            | Data e   | compression                                       | 53 |

|   |                | 5.2.1    | Introduction to Data Compression Algorithm        | 53 |

|   |                |          |                                                   |    |

| 0 | 1 |     |    | •   |     |

|---|---|-----|----|-----|-----|

| 6 | C | 'on | ci | USI | ons |

|   | 6.1  | Conclusion                  | · | •  | • • | •   | •  | · | • | • | • | · | • | • | • | · | • | · | • | • | 57 |

|---|------|-----------------------------|---|----|-----|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

|   | 6.2  | Suggestions for future work | • | •  | • • | •   |    | • | • | • | • |   | • | • | • | • | • | • | • | • | 58 |

| A | Circ | mit Diagrams                |   |    |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |   | 60 |

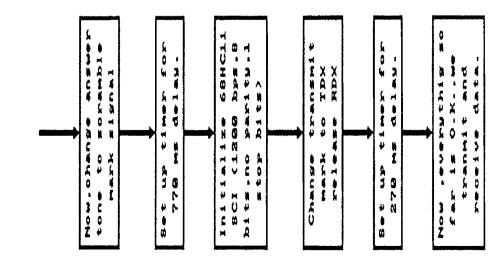

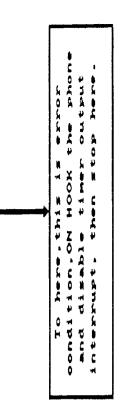

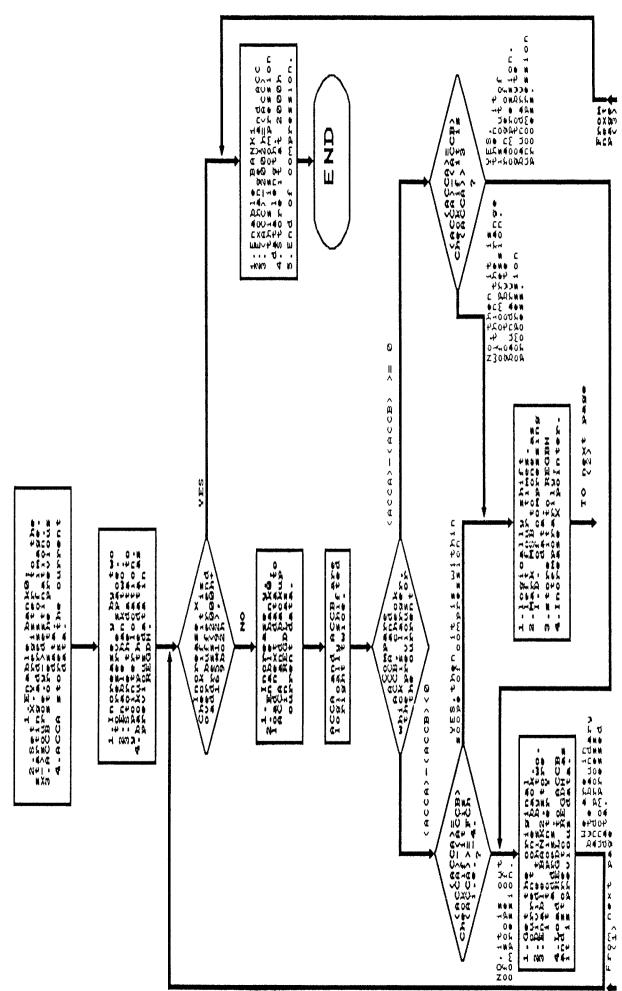

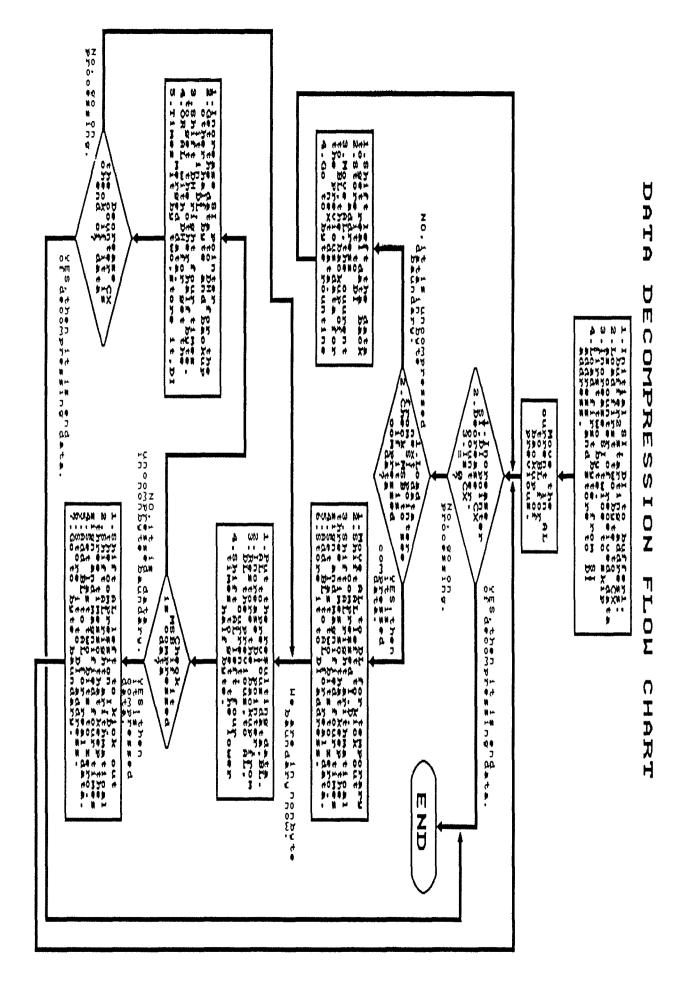

| в | Flov | vchart for Microcontroller  | S | of | tw  | /a) | re |   |   |   |   |   |   |   |   |   |   |   |   |   | 63 |

# List of Figures

,

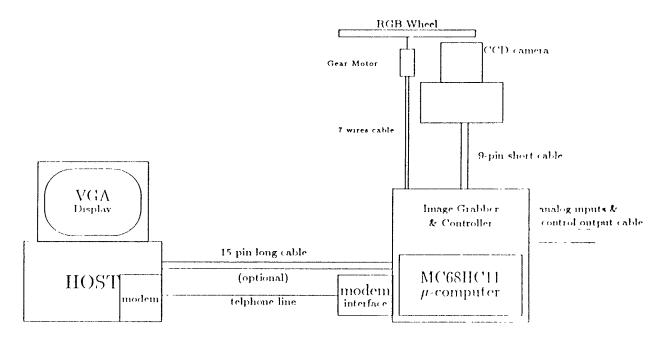

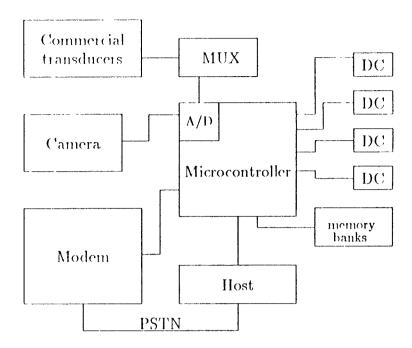

| 21   | System Hardware Block Diagram                                     | 5   |

|------|-------------------------------------------------------------------|-----|

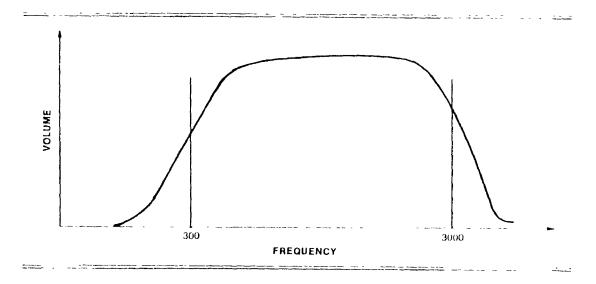

| 3.1  | The Bandwidth of a Public Telephone Line                          | 10  |

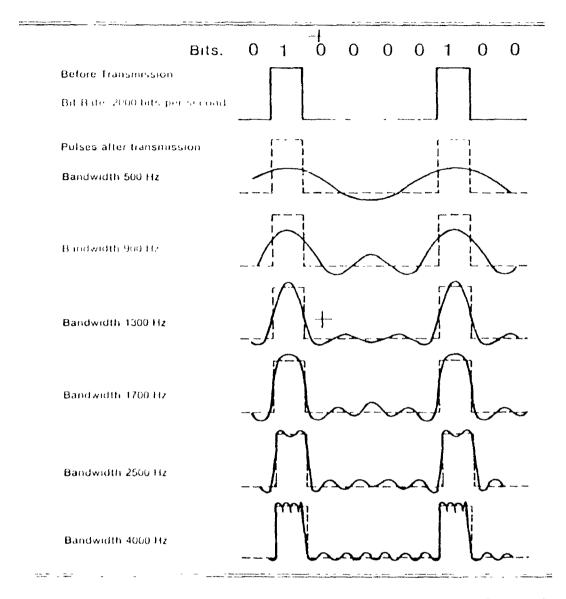

| 3.2  | The Effects of Bandwidth on Square Digital Signals                | 11  |

| 3.3  | Amplitude Modulation                                              | 12  |

| 3.4  | The Simplex Connection                                            | 13  |

| 3 5  | The Half-Duplex Connection                                        | 1.1 |

| 3.6  | The Full Duplex Connection                                        | 15  |

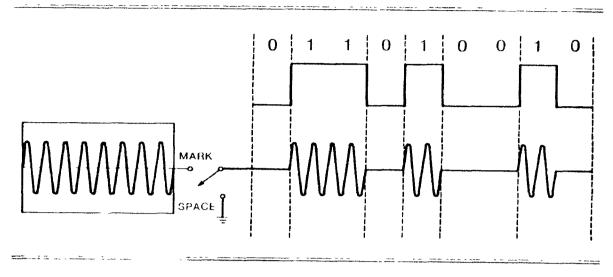

| 3.7  | FSK Modulation                                                    | 16  |

| 3.8  | Tone Assignments for Bell 202 Half-duplex, FSK 1200 bps           |     |

|      | Modem                                                             | 17  |

| 3.9  | Two-level Phase Shift Keying                                      | 18  |

| 3.10 | Quadrature Phase Shift Keying                                     | 19  |

| 3.11 | CCITT-style QAM Modulation for 4800 bps at 600 Baud. $\therefore$ | 21  |

| 1.1  | Block Diagram                                                     | 27  |

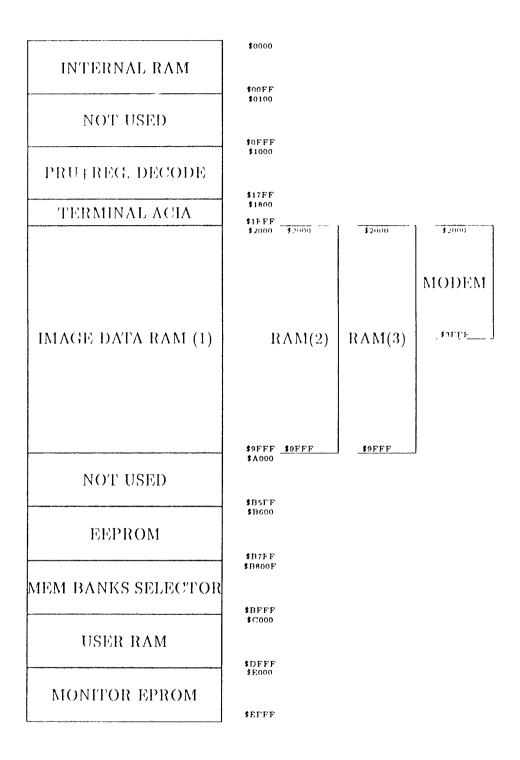

| 1.2  | EVB New Memory Map Diagram                                        | 30  |

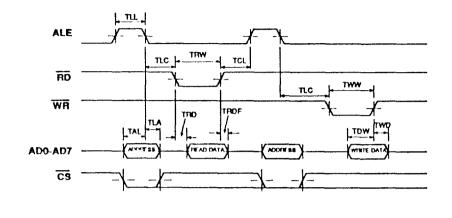

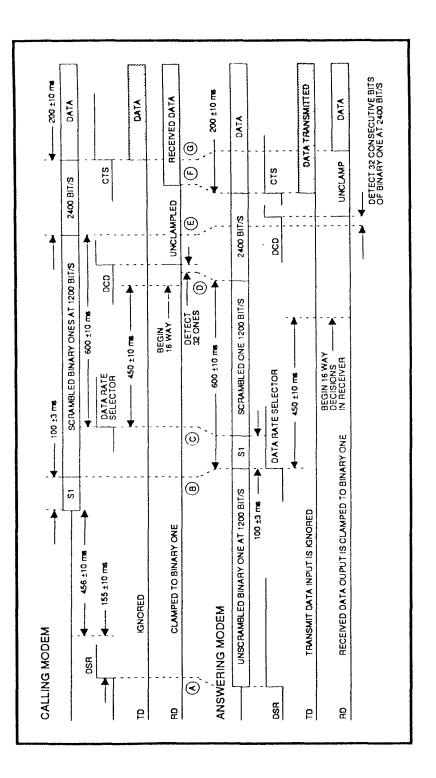

| 43   | Modem Timing Diagram                                              | 31  |

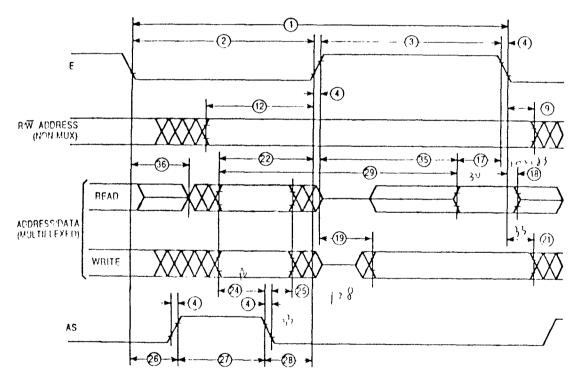

| 1.1  | 68HC11 Expansion Bus Timing Diagram                               | 31  |

| 15   | SSI73K224 Pin Description                                         | 33  |

| 4.6 | DAA Pin Description                            |

|-----|------------------------------------------------|

| 1.7 | CCITT V.22 Connect Handshake Sequence          |

| 5.1 | A picture transmitted without data compression |

| 5.2 | A picture transmitted with data compression    |

| 5.3 | data compression formats                       |

| A I | Modem circuit diagram 1 / 2                    |

| Α.2 | Modem circuit diagram 2 / 2                    |

| ΒI  | Flowchart for Microcontroller Software         |

# List of Tables

| 3-1 | Bell 103 vs CCITT V.21 300 bps, Full-duplex Tone Assignment | 17 |

|-----|-------------------------------------------------------------|----|

| 3.2 | Tone Assignment for the Bell 212A                           | 20 |

.

# Chapter 1 Introduction

# 1.1 Role of the Modem in Machine Vision Systems

With the frequent usage of computers and especially PCs, data communications are of importance. Communication between the various computer systems and terminals is frequently accomplished by means of the Public Switched Telephone Network (PSTN). The essential element for data communication is the modern, which connects computer systems and terminals by means of the telephone network. The modern modulates the serial binary digital data into an analog form that can be transmitted across a telephone line, and it also demodulates the analog signal from the telephone line into the binary digital data.

In last few years the charged-coupled device (CCD) has become an important image sensor in real world industrial applications and commercial markets. In this design, these two elements are combined with some peripheral hardware, firmware and software so that images, analog data and commands can be transmitted between the vision system and a host computer wherever a telephone line is installed. The 2400 baud modern is currently a popular, cheap, and high speed modern. Because of the speed limit, it takes several minutes to transfer an image of modest resolution. With the help of software data compression, we may shrink the transmission time.

## **1.2** Machine Vision System Developed at NJIT

This thesis continues the work set forth in three previous theses. M1. Li first implemented a low-cost intelligent CCD, with the M68HC11 microcomputer TC211 CCD chip [1]. Mr. Feng developed a high speed local transmission interface (2 M bits synchronous transmission) and wrote software for a host computer so that an image could be displayed and manipulated on a monochrone monitor the NMVS system [2]. Mr. Qi expanded the camera memory to three banks of 32K bytes each, modified and improved M1. Li's hardware and software so that the CCD could take pictures [3]. Mr. Qi also added a RGB color wheel in front of the camera to capture the filtered images and added 9 channel analog input and four on/off switch controls to the system. This thesis describes mainly the modem part of the system. This system will be utilized by the biotechnology research group at the New Jersey Institute of Technology.

# **1.3** Thesis Description

There are many modem applications in today's market. Combined with the carlier machine vision system, the modem provides an extra-long distance remote control. This system has a controller side and a PC side. On the controller side, the low cost 68HC11 evulation board (EVB) is used to control a medium resolution CCD image sensor and a 2400 baud modem chip. On the PC side, a personal computer PC XT/AT with a VGA monitior and a 2400 baud modem card is used. The EVB has an M68HC11 single chip microcontroller from Motorola. The CCD sensor (TC211) is a 165×192-pixel monochrome image sensor from Texas Instruments and the 2400 baud single chip modem (SSI224L) is from Silicon Systems. This design provides information about using a 68HC11 to control modem and CCD chips. In addition, the modem part can work with existing hardware and software without conflict. This system can be locally controlled by a high speed synchronous port or by lower speed, but distant, remote control through a modem, or by both means

# Chapter 2 General System Description

# 2.1 System Profile

In this chapter, we introduce the overall system operation briefly, emphasizing the parts developed in this thesis. The complete vision control system with a data logger discussed in this thesis has the following basic capabilities: image grabbing and storage, analog signal input channels, digital control outputs, local high speed communication and long distance remote communication with a host computer. Figure 2.1 shows the overall system hardware configuration.

The camera and the image grabber are connected by a 9-pin short cable, which conducts the level shifted pulse trains to shift out the image data and return the analog pixel signals down to the grabber. The host PC can generate a color image from three filtered images derived by a rotating RGB filter. The system has three infra-red sensors so that it can determine the angular position of the RGB wheel.

The optional 2 M bit per sec local connection between the image controller

Figure 2.1: System Hardware Block Diagram

and the PC add-on card is a 15 pin long cable, which provides a digital, serial channel for transmitting image data from the controler to the PC add-on card and receiving commands from the PC add-on card. Also, the system supplies a long distance communication capability through a modern interface so that the host PC and image controller can be placed anywhere as long as there is a telephone line installed. The two communication modules can work together. Depending on the controller software and the related software on the PC, the system can be in a local high speed mode or remote long distance mode. In this thesis, we concentrate on modem interface design

# 2.2 M68HC11 Evaluation Board

The image controller of Figure 2.1 is based upon the M68HC11 Evaluation Board [9]. The information in this section describes that part of the evaluation board related to the modem interface design. The M68HC11 is a low-cost MCU (microcomputer unit) made by Motorola Corp [11] [12] It can have 512 bytes EEPROM, and 512 bytes RAM on chip, plus several I/O peripherals. In an expanded mode, it can access up to 61K external memory It is one of the Motorola microcontroller product series and can execute not only all of the M6800 and M6801 instructions but also 91 new opcodes [10]. It is a memory mapped I/O processor. All of the on-chip peripheral I/O addresses are reserved from  $1000^1$  to 103F. The system interrupt vector jump table is from C4 to FF.

This MCU supplies several I/O peripheral functions. It makes an ideal chip for low-cost and small application controller. It has the following I/O functions on chip:

- one asychronous serial communication interface (SCI),

- one synchronous serial peripheral interface (SPI),

- three timer input captures,

- five timer output compares,

- six channel multiplexed A/D converter,

- every pin of port A, port B, port C, port D (all 8 bits) can be parallel I/O or some specific function.

In this design, we use SCI for the modem and SPI for local high speed synchronous communications. The  $\Lambda/D$  converter converts the analog image signals into an 8 bit data digital form so that an image can be transmitted.

<sup>&</sup>lt;sup>1</sup>8 is Motorola symbol for hexadecimal notation

The 68IIC11 supplies several independent parallel I/O pins when not used for a dedicated functions. In Qi's design, PA6, PA5, PA4 generate the required timing for the CCD. PA2, PA1, PA0 are used for the three infra-red sensor inputs. PB0 is used to control the DC motor and PB1, PB2, PB3 are used to control four switch outputs. In my design, PA3 output is used to control the on/off hook of the DAA, and PA2 input is shared between the infra-red sensor and the the measurment of ringing width from the telephone interface.

# 2.3 Introduction to Modem Interface

A device that can modulate binary digital data into analog form for transmission across the telephone line and also demodulate the analog signal from telephone line into digital binary data is called a modern. A serial port that converts parallel data into serial form, and vice versa, can work with a modern interface so that it is possible for computers to talk with one another through the telephone line. Figure shows the block diagram of modern interface. In this design, we chose SSI 73K224L single chip modern from Silicon Systems and the DS6112 DAA (data access arrangement) from Dallas Semiconductor to to perform the PSTN interface [4] [5].

The DAA is a communication component that provides a "direct connect" telephone line interface. The chip provides high voltage isolation, independent ON/OFF HOOK control, ring detection circuity, and a 2 to 4 wire converter hybrid for use in a modern application. With this integrated DAA, the PSTN interface is simple and reliable.

8

**、**

\_

# Chapter 3 Introduction to Modem Theory

This chapter explores the topic of how computer data are transferred across ordinary telephone lines. First, we will describe some of the technical aspects of a modern. Having stated the principles involved, we will discuss how computer and related peripherals interact with a modern to control its behavior

# 3.1 Modem Fundamentals

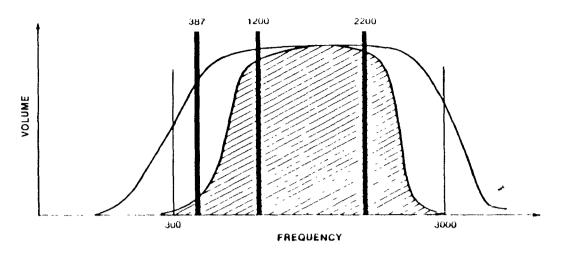

Digital signals from devices such as teleprinters cannot be transmitted directly over telephone lines. Because a telephone line is intended to carry human speech, which contains frequencies in the range of 200 - 8000 Hz, its frequency response (bandwidth) is rather limited. As a matter of fact, since the goal of telephone networks is not fidelity, but intelligibility, the telephone does not even reproduce voices particularly well. Figure 3.1 shows the bandwidth of the public telephone system.

Now, a square wave can be mathematically analyzed as if it were a com-

Figure 3.1. The Bandwidth of a Public Telephone Line

posite of sine waves at odd multiples of its frequency. A square wave of 200 Hz, for example, has progressively smaller amounts of 600 Hz, 1000 Hz, and 1400 Hz, and so on. To transmit an acceptable square digital signal the communications medium must have a significantly wider bandwidth than the base frequency of the square wave itself. If the bandwidth is too narrow, then the resulting waves are not recognizable. At the receiver, the logic level of the digital signal becomes ambigious and communication fails.

## 3.1.1 Modulation

The problem depicted in Figure 3.2 would occur if we attempted to transmit a computer's square waves over the voice-grade lines of the public telephone network. Clearly, a method is needed to convert data from square waves to a form that can pass unscathed over the telephone network. Sine waves are the best candidate because they can be easily created in a harmonically "pure"

Figure 3.2: The Effects of Bandwidth on Square Digital Signals

form that is less radically affected by the frequency roll off inherent in the telephone line.

The process of encoding one signal with a carrier is modulation and the recovery of the original signal is demodulation. A device that performs both modulation and demodulation on a communication line is known as a *modern*. The simplest form of modulation is amplitude shift keying or ASK modu

Figure 3.3: Amplitude Modulation

lation, as depicted in Figure 3.3. During transmission, modulation occurs when a single sine wave tone is switched between two amplitudes (volume levels) to represent binary 1 and 0.

#### 3.1.2 Connection Modes

Before we examine more sophisticated modulation techniques, we may review the terminology describing the various ways of utilizing the available bandwidth of a communication line.

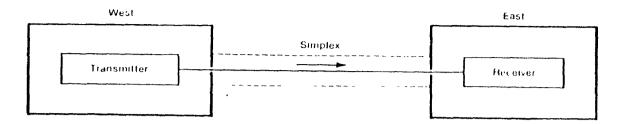

#### The Simplex Connection

A transmitter (such as the simple ASK modulator just described) at one end of the telephone line and a receiver at the other end form a simplex connection — that is, a connection in which data traffic moves in only one direction. This arrangement is illustrated in Figure 3.1. Because they are inherently non-interactive, simplex installations have limited applications.

Figure 3.4. The Simplex Connection

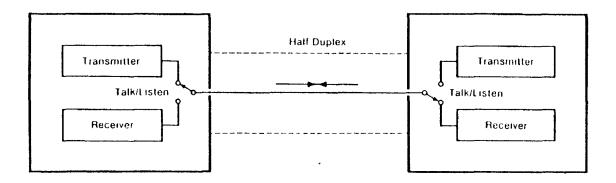

#### The Half-Duplex Connection

A limited kind of two-way system can be built from two simplex connections. As illustrated in Figure 3.5, each modern contains a transmitter and a receiver, one of which is connected to the communications line through a "talk/listen" switch. For West-to-East traffic, modern W connects its transinitter to the line and modern E connects its receiver. This arrangement is reversed for East-to-West traffic. Changing the position of the "talk/hsten" switch is called "turing the line around.". The "talk/hsten" switch is, of course, not a physical switch but an electronic one controlled by software The two ends convey the need to turn the line around through half duplex protocols such as the ETX/ACK protocal.

#### The Full-Duplex Connection

Although the half-duplex arrangement is considerably more flexible than the simplex, it is nevertheless inefficient. The time required to switch the circuitry from transmit to receive mode is commonly on the order of 200 mil-

Figure 3.5: The Half Duplex Connection

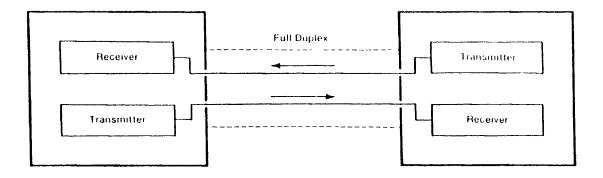

hiseconds. A delay of such duration is intolerable in time sensitive, interactive applications such as remote instrumentation monitoring and control systems. The shortcomings of half-duplex communications can be avoided simply by taking the idea of channel-sharing one step further. Instead of alternately sharing receiver and transmitter, each end of the connection contains both a transmitter and a receiver — one pair for communicating East-to West and another for West to East. The full-duplex connection is shown in Figure 3.6. To prevent interference, a separate distinct tone is assigned to traffic in each direction. The general idea of dividing a communications channel into smaller frequency bands is called frequency division multiplexing or 1.DM

## 3.1.3 Channel Usage Conventions

Since a full-duplex connection consists of two simplex channels in use simultaneously, modems operating in full-duplex mode must agree upon how they will allocate the signals. For example, the modem might agree beforehand that the modem that uses the higher-frequency channel should be called a Girl modem, while those that use the lower are Boy modems. The problem

Figure 3.6: The Full Duplex Connection

with this approach is that when the telephone rings there is no way to know whether the caller is a Boy or Girl. Instead of using fixed definitions such as Boy and Girl, channel assignments are determined by the point of origin of the call. The modern placing the call is expected to use the originate channel and the modern receiving the call is expected to use the answer channel

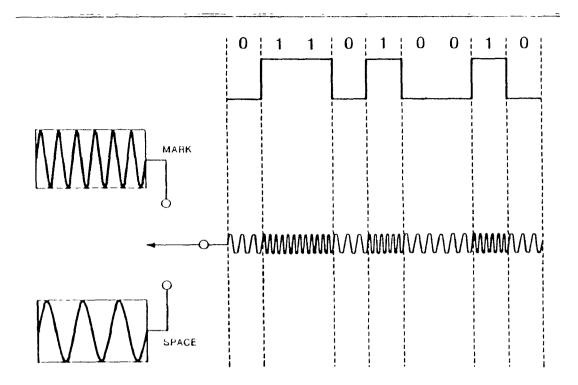

## 3.1.4 Frequency Modulation

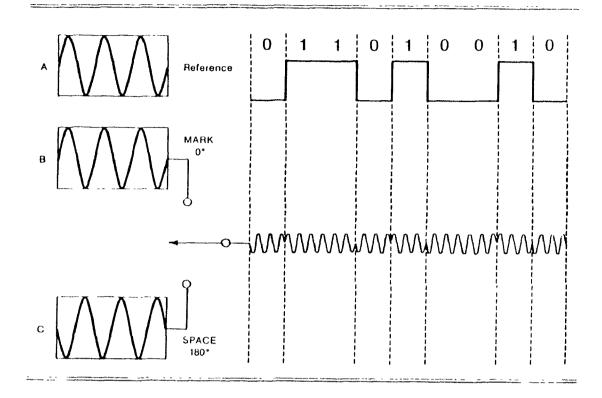

ASK modulation's greatest weakness is its susceptibility to noise because it uses amplitude variation to encode digital logic levels. Since no known natural phenomenom changes a signal's frequency, much more reliable encoding can be attained by frequency modulation. Since a modern need only transmit 1s and 0s, data can be represented by switching between two different frequencies. Mark/Space is defined to represent 1/0. Figure 3.7 depicts FSK modulation, but the frequency difference between the two tones is exagger ated for clarity. Figure 3.8, however, shows how the dual tones are actually assigned in the Bell Model 202, a half duplex 1200 bps modern using FSK modulation. This modern uses two tones 1000 Hz apart, centered about 1700

Figure 3.7: FSK Modulation

IIz. The 1200 Hz tone represents a MARK and the 2200 Hz tone a SPACE. Table 3.1 shows the FSK tone assignment for a Bell model 103, a full duplex, 110-300 bps FSK modem. The originate modem uses two tones, 100 Hz apart, centered about the frequency 1170; a SPACE is 1070 and a MARK is 1270. The answer modem tone also 100 Hz apart, but centered about 2125 Hz; here, a SPACE is 2025 and a MARK is 2225. Notice that the frequencies are chosen so that there is very little overlap between their spectra and consequently little interference between the two.

## 3.1.5 Phase Modulation

A periodic waveform has three properties : amplitude, frequency, and phase. We have already examined modulation techniques that encode digital data

Figure 3.8. Tone Assignments for Bell 202 Half duplex, FSK 1200 bps Modem

|               | Orig        | inate        | Ans          | wer          |  |

|---------------|-------------|--------------|--------------|--------------|--|

|               | MARK        | SPACE        | MARK         | SPACE        |  |

| Bell<br>CCHTT | 1270<br>980 | 1070<br>1180 | 2225<br>1650 | 2025<br>1850 |  |

Table 3.1: Bell 103 vs CCITT V.21 300 bps, Full duplex Tone Assignment

into amplitude (ASK) and frequency (FSK). We will now briefly examine phase modulation, where information is encoded in the temporal relationship between two otherwise identical waveforms. In particular, we will examine the technique known as phase shift keying (PSK).

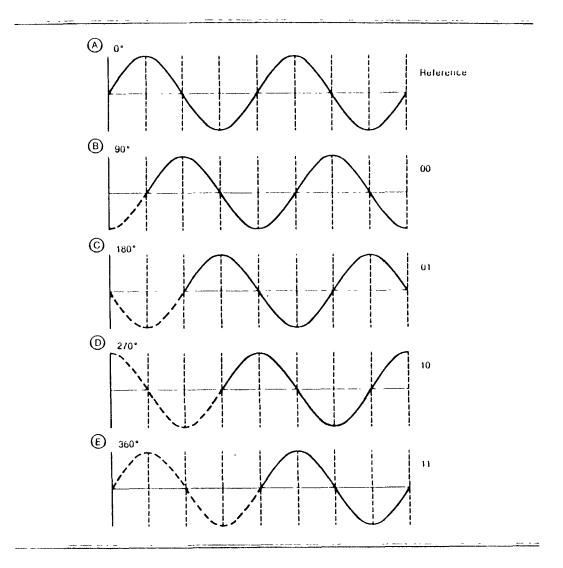

## 3.1.6 Two-level Phase Shift Keying

Figure 3.9 shows three waveforms, all exactly the same amplitude and frequency, but differing in phase. One complete cycle of any period waveform is expressed as  $360^{\circ}$ . With respect to waveform A, waveform B is said to be in phase or, stated differently, its phase angle is  $0^{\circ}$ . Waveform C, however, lagbehind waveform A by  $180^{\circ}$  and its phase angle is  $-180^{\circ}$ . Modulation consists of sending waveform C for a SPACE, and waveform B for a MARK (We

Figure 3.9: Two level Phase Shift Keying

assume that both sender and receiver already have local copies of waveform A which act as references. It need not be transmitted.)

### 3.1.7 Quadrature (Four-Phase) PSK

The encoding process known as *quadrature* phase shift keying (QPSK) is identical to the previous example except instead of encoding bits in two phase angles ( $0^{0}$  and  $-180^{0}$ ), four phase angles are used  $-0^{0}$ ,  $90^{0}$ ,  $180^{0}$ ,  $270^{0}$ . To understand how a modern attains a bit rate of, say, 1200 bps from a modulation rate of 600 band, we have to understand that in asynchronous 1/O, a byte is broken up into dibits. The new basic unit of data is no longer the bit, but the 2-bit pair, or dibit. Figure 3.10 shows how a dibit is encoded as

Figure 3.10: Quadrature Phase Shift Keying

one of four phase angles

## 3.1.8 Differential Phase Shift Keying

Our earlier examples assume that both sender and receiver have local copies of the reference waveform. If this is so, what keeps the sender's and receiver's reference waveform synchronized? The solution, called *differential* phase shift key (DPSK), abandons altogether the idea of deriving phase differences from a quiescent reference signal (i.e. a sync pulse). Instead, the

| Órigi    | inate   | Ans      | wer     |

|----------|---------|----------|---------|

| Transmit | Receive | Transmit | Receive |

| 1200     | 2400    | 2400     | 1200    |

Table 3.2: Tone Assignment for the Bell 212A

phase angle for each cycle is calculated relative to the *premous* cycle. A modulation rate of 600 band using four-level PSK provides a data rate of 2400 bps. This can be used in its entirety as a single 2400 bps half duplex channel as in the Bell 201 modern, or divided into two full duplex 1200 bps channels. The latter is the configuration of the popular Bell 212A modern whose frequency assignments are shown in Table 3.2.

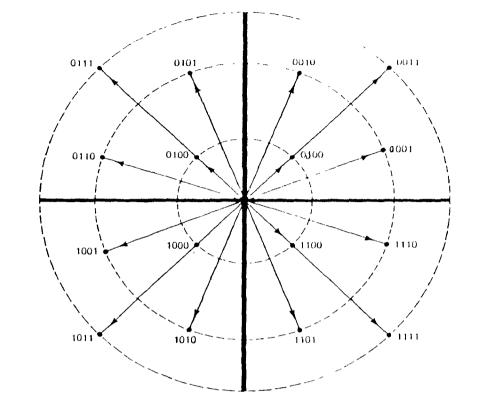

#### 3.1.9 Quadrature Amplitude Modulation

We have seen how data can be encoded into a signal's amplitude (ASK) and its phase (PSK). Aspects of both of these forms of modulation are combined to produce yet another modulation technique known as Quadrature Amplitude Modulation, or QAM. This technique results in a total data rate of 4800 bps with 600 baud modulation. QAM is specified by the CCITT V.22 bisfull-duplex standard and has been adopted by the Hayes Smartmodem 2400 and others.

Just as the basic data unit for PSK is the dibit, QAM uses the *quabit*, or nibble. The CCITT version of QAM employs twelve phase angles in conjuction with three amplitudes. Of the resulting thirty-two unique phase/amplitude combination, only sixteen are used to encode a quadbit. The remaining six

Figure 3.11: CCITT style QAM Modulation for 1800 bps at 600 Baud teen combinations will be used in the future to attain a data rate of 9600 bps (1800 bps in full duplex). These are depicted in the phase "constellation" in Figure 3.11.

One of the chief benefits of frequency and phase modulation techniques such as FSK and PSK is their immunity to noise. By adding amplitude modulation to PSK, QAM sacrifices some noise immunity to achieve increased data rate. Indeed, in a noisy environment where a 1200 baud full duplex modem operates flawlessly, the 2400 full duplex QAM modern may be unusable

# 3.2 Introduction to Modem Chip

#### 3.2.1 Description

In this design, The SSI 73K224L single-chip modem from Silicon Systems, Inc is used [4]. It is a highly integrated single-chip modem IC which provides the functions needed to construct a V.22bis compatible modem, capable of 2400 bit/s full-duplex operation over dial-up lines. The SSI 73K224L offers excellent performance and a high level of functional integration in a 28 pin DIP. This device supports all V.22bis, V.22, V.21, Bell 212A and Bell 103 modes of operation, allowing both synchronous and asynchronous communication

The chip is designed to appear to the system designer as a microprocessor peripheral. It will easily interface with popular single-chip microprocessors for control of modem functions through its 8-bit multiplexed address/data bus or via an optional serial command bus. An ALE control pin simplifies address demultiplexing. Data communications normally occur through a seperate serial port. The SSI 73K224L is pin and software compatible with the SSI 73K212L, which just supports the BELL 212A (1200 bps) and BELL 103 (300 bps) standards. It can operate from a single +5 volt supply for low power consumption. It is ideal for use in either free-standing or integral system modem products where full-duplex 2400 bit/s data communication over the 2-wire telephone network is desired. A complete modem requires only the addition of the phone line interface or data access arrangement (DAA), a control microprocessor, and RS-232 level converters. In this design, RS-232 level converters are not needed.

# 3.2.2 QAM Modulation/Demodulation

The SSI modem encodes incoming data into quadbits represented by 16 possible signal points with specific phase and amplitude levels. The baseband signal is then filtered to reduce intersymbol interference on the bandlimited telephone network. The demodulator, although more complex, essentially reverses this procedure while also recovering the data clock from the incoming signal. Adaptive equalization corrects for varying line conditions by automatically changing filter parameters to compensate for line characteristics.

# 3.2.3 Passband Filters and Equalizers

High and low band filters are included to shape the amplitude and phase response of the transmit and receive signals and provide compromise delay equalization and rejection of out-of-band signals. Amplitude and phase equalization are necessary to compensate for distortion of the transmission line and to reduce intersymbol interference in the bandlimited receive signal

## 3.2.4 Parallel Bus Interface

Seven 8-bit registers are provided for control, option select, and status monitoring. These registers are addressed with the AD0, AD1, and AD2 multiplexed address lines (latched by ALE) and appear to a control microprocessor as seven consecutive memory locations. Five control registers are read/write The status detect and ID register are read only and cannot be modified except by modem response to monitored parameters.

# 3.3 Serial Input / Output

For most personal computers, serial input and output peripherals are used to reduce the number of connections to the outside world and are important and very popular I/O peripherals. SIO is a serial I/O that converts parallel data into serial data and vice versa. In this system an SIO port interfaces to a modem at the host PC and another, the SCI port of the 68HC11, interfaces to the modem chip at the image grabber.

# 3.4 Introduction to Hayes modem

Before micros, the Bell 212A or 103A modems were unchallenged standards, at least in America. But in the micro word and increasingly in the rest of computerdom as well, the Hayes Smartmodem product family has come to be the standard in the same fashion as the IBM line of micros has become the standard microcomputer. So dominant is the Hayes influence that market analysts estimate that upwards of 90 percent of all modems manufactured for the microcomputer market are compatible (or claim to be) with the Hayes Smartmodem.

#### Smartmodem States

Whenever the Smartmodem is engaged in a carrier link with another modem (called its online state), it behaves as a conventional modem, passing all RS-232 input directly to its transmitter. When not online, however, the Smartmodem is said to be in the command state, and RS-232 data is treated as potential commands. It is possible to switch the Smartmodem from the online to the command state and back again - without breaking the carrier link.

#### Startmodem Command State

In command state, the Smartmodern monitors the byes incoming from the RS-232 port in search of a particular sequence of bytes referred to as the Command Sequence Introducer, or CSI. After the CSI is encountered, the Smartmodern places subsequent character in its internal 40-character buffer, until the buffer becomes full or it encounters the Command terminator character. The Smartmodem's command terminator is nll, so by default, Carnage Return. The Smartmodem's CSI is AT, supposedly an abbreviation for "ATTENTION." AT also provides the modern with the transmission speed, character length, and parity set by your terminal or computer, and must appear at the start of every command line except for A/. AT also clear the last executed command line that stored in the command buffer. See chap4 for specific use of Hayes commands for this application.

# Chapter 4 System Design

In this chapter, the system design related to modem will be described in detail. The system consists of two sides, the Motorola 68HC11-based contoller side and the PC side. The controller side has the following capabilities: grabbing the images from the CCD, accepting the 9 channel analog input, controlling 4 digital switches, controlling SPI for high speed local communication, or controlling SCI and modem chip for long distance communicatiom through public telephone system. The controller hardware block diagram is sketched in Figure 4.1. The PC side should have a VGA interface card and a VGA monitor to display the image in 64 gray levels. The high speed synchronizing card can interface SPI. The 2400 bps modem card can interface to the telephone system.

# 4.1 Hardware Design

The hardware design in the thesis is the modern interface on the controller side. Because the modern interface must work with the rest of the previously designed hardware module, it is designed to do so.

Figure 4.1: Block Diagram

## 4.1.1 Memory Decoder And Modem Decoder in 68HC11

Three banks of memory has been added to the EVB so that we can store an image in each. Since the original EVB did not support continuous memory with size more than 32K ( $\$000^{-1}$ ), the hardware and firmware were modified [3]. The bank memory starts from \$2000 to \$9FFF, totally 32 K, and the bank switch selector is at \$B800 (not fully decoded). The new memory map is shown in Figure 4.2. In the thesis, modem addresses are from \$2000 to \$3FFF but in bank four. Every time the firware program wants to access a register of the modem, it enables bank four first. The following program segment is an example of selecting bank four memory.

<sup>&</sup>lt;sup>1</sup>\$ means this is hexadecimal

|      | :      |                  |

|------|--------|------------------|

|      | :      |                  |

| LDAA | #\$04  |                  |

| STAA | \$B800 | ; enable bank 4. |

|      | :      |                  |

|      | :      |                  |

The first bank of memory is normally used to store image data that is gotten from the A/D converter with no compression. The second bank is chosen to store compressed data. The data compression program must enable the respective banks before accessing them. The following program is an example of part of data compression program.

|      | :      |                                       |

|------|--------|---------------------------------------|

|      | :      | · · · · · · · · · · · · · · · · · · · |

| LDAA | #\$00  | ;enable bank 0.                       |

| STAA | \$B800 |                                       |

|      | :      | ;then fetch uncomoressed data.        |

|      | :      | ;process it into compressed data.     |

|      | :      |                                       |

| LDAA | #\$01  | ;enable bank 1.                       |

| STAA | \$B800 |                                       |

|      | :      | ;then store compressed data           |

|      | :      |                                       |

The decoder (74LS138) in EVB can't be used to be a modem decoder because timing of both sides do not match each other. We need to build a new modem decoder. The modem timing diagram is shown in Figure 4.3. The modem circuit diagram is shown in Appendix A. The 68HC11 expanding mode bus timing diagram is shown in Figure 4.4. The AS (address strobe) of 68HC11 is connected to ALE (address latch enable) of modem chip. When the chip is selected and AD0-AD7 carry the internal register address, the  $\overline{CS}$  (chip select, active low) of SSi 73K224L should be active and the falling edge of ALE latches the address on AD0-AD2. The decoded  $\overline{CS}$  should be active at first phase of every instruction. Connecting E clock to  $\overline{G2B}$  (pin 5 of LS138) enables decoding at the first phase.

# 4.1.2 Modem Chip Hardware Interface with 68HC11 and DAA

This section describes general hardware connection. The 68HC11 pin description is shown in Figure 4.5. AD0-AD7 of the modem chip is an address/data bus whose bidirectional tri-state multiplexed lines carry information to and from the modem registers. AD0-AD7 of the modem chip are connected with AD0 AD7 of the 68HC11. Reset pin of the modem which is active high will put the chip into an inactive state. This RESET pin is connected with a inverted  $\overline{RESET}$ , an active low 68HC11 signal generated from external reset button.  $\overline{RD}$  pin of the modem chip is active low signal which requestes a read of the SSI 73K224 internal registers. Because  $\overline{RD}$  is active in second phase of each intruction, this signal is generated by NAND of E clock and R/W of 68HC11.  $\overline{WR}$  pin of the modem chip is an active low signal which

Figure 4.2: EVB New Memory Map Diagram

ł

Figure 13: Modem Timing Diagram

Figure 4.4: 68IIC11 Expansion Bus Timing Diagram

informs the SSI73K224 that data is available on AD0-AD7 for writing into an internal register. This signal is also gated with E clock.

At this point we know how to interface the modern chip with the 68HC11 for command and status interchange. The chip modulates a serial digital signal into an analog signal or demodulates the analog into a digital signal. The serial data appear on RXD and TXD, RXD is Received Digital Data and TXD is a Transmitted Digital Data. We just connect the respective RXD and TXD pins of the modern chip to RXD and TXD of the 68HC11.

The DAA was described before as a communications component that provides a direct connect telephone line interface. The pin description is shown in Figure 4.6. It needs +/-5 volt power supplies. LM7905 is a very good voltage regulator which input is -12 voltage and output is -5 voltage. The TIP and RING pin ( pin 17 and 18 ) of DAA are telephone line inputs, which connect to the telephone line via a standard RJ11C jack. The RI (pin 3) of the DAA is a active low input ring detect, which indicates when ring voltage is present at TIP and RING. The RI (ring detect) is connected to PA2, shared with optical sensor 2 input. When we enable bank four, PA2 pin is connected to RING pin , but when bank one is enabled, PA2 is connected to pAA. The OH pin is connected to the PA3 pin (configured as ouput) of the 68HC11 which can be software controlled to high ("receiver" picked up) or low ("receiver" hung up).

| NAME | 28-P1N | 44-PIN | ТҮРЕ | DESCRIPTION                                                                                                                                                                                   |

|------|--------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND  | 28     | 44     | I    | System Ground                                                                                                                                                                                 |

| VDD  | 15     | 23     | I    | Power supply input, 12V +10%, -20% (or 5V $\pm 10\%$ ) Bypass with 1 and 22 $\mu F$ capacitors to ground                                                                                      |

| Vref | 26     | 42     | 0    | An internally generated reference voltage Bypass with 1 $\mu F$ capacitor to Ground                                                                                                           |

| lset | 24     | 36     | I    | Chip current reference. Sets bias current for op amps. The chip current is set by connecting this pin to VDD through a 2 MΩ resistor. Is et should be by passed to GND with a 1 µF capacitor. |

| ALE     | 12   | 20     | l   | Address latch enable. The falling edge of ALE latches the address on AD0 AD2 and the chip select on CS                                                                                                                                                                                                                  |

|---------|------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0-AD7 | 4-11 | 4,9-15 | I/O | Address/data bus These bidirectional tri-state multi-<br>plexed lines carry information to and from the internal<br>registers                                                                                                                                                                                           |

| CŠ      | 20   | 32     | 1   | Chip select A low on this pin allows a read cycle or a write cycle to occur AD0-AD7 will not be driven and no registers will be written if $\overline{CS}$ (latched) is not active $\overline{CS}$ is latched on the falling edge of ALE                                                                                |

| CLK     | 1    | 1      | 0   | Output clock This pin is selectable under processor<br>control to be either the crystal frequency (for use as a<br>processor clock) or 16 x the data rate for use as a baud rate<br>clock in QAM/DPSK modes only. The pin defaults to the<br>crystal frequency on reset                                                 |

| INT     | 17   | 25     | Ο   | Interrupt This open drain weak pullup, output signal is used to inform the processor that a detect flag has oc-<br>curred. The processor must then read the detect register to determine which detect triggered the interrupt. INT will stay active until the processor reads the detect register or does a full reset. |

| НŬ      | 14   | 22     |     | Read A "low" requests a read of the SSI 73K224 internal registers. Data cannot be output unless both RD and the latched CS are active or "low "                                                                                                                                                                         |

| RESET   | 25   | 37     | 1   | Reset An active signal "high" on this pin will put the chip<br>into an inactive state All control register bits (CR0, CR1,<br>CR2, CR3, Tone) will be reset. The output of the CLK pin<br>will be set to the crystal frequency. An internal pull down<br>resistor permits power on reset using a capacitor to VDD       |

| NAME | 28-PIN                          | 44-PIN                  | TYPE                         | DESCRIPTION                                                                                                                                                                                                                                     |

|------|---------------------------------|-------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ŴŔ   | 13                              | 21                      | I                            | Write A "low" on this informs the SSI 73K224 that data is<br>available on AD0-AD7 for writing into an internal register<br>Data is latched on the rising edge of WR. No data is written<br>unless both WR and the latched CS are active ("low") |

| Note | The serial cor<br>configuration | ntrol mode<br>AD7 becon | is provided i<br>nes DATA ai | in the 28 pin version by tying ALE high and CS low In this hid AD0, AD1 and AD2 become A0, A1 and A2, respectively                                                                                                                              |

Figure 4.5. SSI73K224 Pin Description

|                |          | vinit .   | 1 20 1910                                                                                                                        |  |  |

|----------------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

|                |          | Vric I    | 2                                                                                                                                |  |  |

|                |          | PI [      | 3 17 J HP                                                                                                                        |  |  |

|                |          | bendo (   | 1                                                                                                                                |  |  |

|                |          | YHIT [    |                                                                                                                                  |  |  |

|                |          | лир (<br> | 7 14 7 11/C                                                                                                                      |  |  |

|                |          |           | $\begin{bmatrix} 7 \\ 12 \\ 13 \end{bmatrix} = \begin{bmatrix} 14 \\ - \end{bmatrix} \begin{bmatrix} 1/C \\ 1/C \end{bmatrix}$   |  |  |

|                |          | (+10)     |                                                                                                                                  |  |  |

|                |          | Τ, [      |                                                                                                                                  |  |  |

| 17311          | STREET.  | init [    | DESCRIPTION                                                                                                                      |  |  |

| 1              | · / · /· | -         | Nogative Supply50 volts                                                                                                          |  |  |

| 2              | \/<br>   | -         | Positivo Supply. 45 9 volts.                                                                                                     |  |  |

| 3              | R        | ()        | Ring Detect Active low output; indicates when ring voltage is present at TIP and NING. >                                         |  |  |

| 4              | ROVR     | ()        | Receive. Extracted receive signal                                                                                                |  |  |

| 5              | 2111     | 1         | Promit. Transmit signal Input.                                                                                                   |  |  |

| 0              |          | 0         | Transfermen - Commetto I tastinu e log telematic to<br>Sylia converter; leave open when using external 2<br>to 4 wire converter. |  |  |

| 7              | T1       | 1         | Tep 1. Connect to XMER for Internal 2 to 4 wire<br>converter; to XMER for external 2 to 4 converter.                             |  |  |

| 8              | OH       | 1         | Off Hook. Controls telephone line hook status; when<br>low line is "on hook".                                                    |  |  |

| <u>0</u>       | GLID     |           | Signal Ground 0.0 volts.                                                                                                         |  |  |

| 10             | T2       | -         | Tap 2. Tie to GND for proper operation.                                                                                          |  |  |

| 11,12<br>13,14 | N'C      | -         | No Connect. Leave those pins open for proper<br>operation.                                                                       |  |  |

| 17,18          |          | 1         | Telephone Line Inputs. Connect to telephone line                                                                                 |  |  |

Figure 4.6: DAA Pin Description

# 4.2 Software Design

As the system design is divided into two parts, a controller side and a PC side, so is the firmware design. The design of the firmware described here is modem related. The modem and data compression portion will be in detail but the whole system will be generally described.

## 4.2.1 Controller Firmware Design

The whole idea to add modem into the local transmission system and replace it is very easy knowing of modem connecting sequence, data compression firmware and whole system.

#### Initialization of Serial Communication Interface

The modem modulates serial data into analog form and demodulates the analog signal into serial form. Before description of modem, we will discuss serial port first. The three SCI control registers in the 68HC11 are initialized and its TXD pin is routed on the EVB. In this design, 2400 baud, 8 bits data, no parity and one stop bit asynchronizing transmission is the standard format for both side. To get 2400 baud, write #%00110010<sup>2</sup> binary data to the baud rate register (\$102B). Store #0 to SCCR1 (SCI Control Register 1, \$102C ) to select one start bit, eight data bits, one stop bit and idle line. Write #%00001100 to SCCR2 (SCI Control Register 2) to select TDRE interrupts disabled (software polling), TC interrupts disabled (software polling)

$<sup>\</sup>frac{1}{2}$ # represent this is immediate data and % means binary data for Motorola serial

mode), RDRF and OR interrupts disabled (software polling mode), IDLE interrupts disabled (software polling mode), SCI transmitter enabled, SCI receiver enabled, normal SCI receiver operation, and normal transmitter operation. In 68HC11 evaluation board hardware design, write #0 to \$1000 to select PD0 on P1 connector to PD0 (TXD) of 68HC11 chip, not from host computer I/O port connector. The following program segment is an example of initialization of SCI.

Initialize the SCI .....

.

|      | :                  |                       |

|------|--------------------|-----------------------|

| LDAA | <b>#%</b> 00110010 | ;initialize 2400 baud |

| STAA | BAUD               |                       |

| LDAA | <b>#</b> 0         | ;                     |

| STAA | SCCR1              | ;sci mode             |

| LDAA | <b>#%</b> 00001100 | ;                     |

| STAA | SCCR2              | ;interrupt control    |

| LDAA | <b>#</b> 0         | ;enable flip flop     |

| STAA | \$4000             | ;route TXD            |

|      | :                  |                       |

#### Polling of the Serial Communication Interface

Because a polling system is easier for firmware design and the whole system is insensitive to real time response, polling is chosen for both transmitter and receiver in the 68HC11 communication design. Every kind of interrupt caused by the serial communication is disabled, and the status register is polled every time the system wants to transmit or receive data. There are two registers used in the communication polling firmare. The SCI status register is used to check if the transmit buffer is empty or the receiver buffer has a datum so serial buffer then can be loaded or stored a dataum. for more detailed information, please refer to appendix A. The following program segment is an example of SCI polling :

|    |      | :                  |                                          |

|----|------|--------------------|------------------------------------------|

| ТΧ | LDAA | SCSR               | ;load status register.                   |

|    | BITA | <b>#%</b> 10000000 | ;check Transmit Data Register Empty bit. |

|    | BEQ  | ТХ                 | ; if it is not empty then poll again.    |

|    | STAB | SCDR               | ;store data to serial data register.     |

|    |      | :                  |                                          |

| RX | LDAA | SCSR               | ;load status register.                   |

|    | BITA | <b>#%</b> 00100000 | ;check Receiver Data register full bit.  |

|    | BEQ  | RX                 | ; if it is not full then poll again.     |

|    | LDAA | SCSR               | ;load data from serial data register.    |

|    |      | :                  |                                          |

#### The Ring Input Pulse Width Measuring

The ringing input is connected to PA2 of 68IIC11. The inputs PA0-PA2 of the 68IIC11 have an input-capture function which can be used to measure pulse width. Each input-capture function includes a 16-bit latch, input edge-detection, and interrupt generation logic. The 16-bit latch captures the

current value of the free running counter when a selected edge is detected at the corresponding timer input pin. The edge-detection logic includes control bits so that user software can select the edge polarity that will be recognized. Each of the three input-capture functions can be independently configured to detect rising edges only, falling edges only, or any edge (rising or falling). The interrupt generation logic includes a status flag, which indicates that an edge has been detected, and a local interrupt enable bit, which determines whether or not the corresponding input-capture function will generate a hardware interrupt request.

The central element of each input-capture function is the input-capture latch, which can be read by software as a pair of 8-bit registers. When an edge has been detected and synchronized, the 16-bit free-running counter value is transferred into the input-capture register pair as a single 16-bit parallel transfer.

To measure pulse width, the input-capture edge sensitivity must be reconfigured between the capture of the first edge and the second edge. Since this ringing detect program measures the period of a low-going pulse, the input capture is first configured to capture on a falling edge at PA2. After detecting the first edge, the input capture is reconfigured to detect a rising edge.

Since this pulse width measure program is interrupt driven, it must have an interrupt service routine, which is automatically called as a result of an interrupt, an initialization portion, and a mainline program portion. The following program segment is an example of initialization of TOF and IC1 service routine. TOF is Timer Overflow service routine and IC1 is Input Capture 1 service routine.

Initialization of TOF and IC1 service routine jump table...

|      | :       |                                          |

|------|---------|------------------------------------------|

| LDAA | #\$7E   | ;Jump (extended) Opcode.                 |

| STAA | PVTOF   | ;Pseudo vector.                          |

| STAA | PVIC1   | ;IC1 pseudo vector.                      |

| LDX  | #SV3TOF | ;address of TOF service routine.         |

| STX  | PVTOF+1 | ;finish jump instruction to TOF routine. |

| LDX  | #SV3IC1 | ;address of IC1 service routine.         |

| STX  | PVIC1+1 | ;finish jump instruction to IC1 routine. |

|      | :       |                                          |

SV3TOF-timer Overflow service routine ...

| SV3TOF | TST  | IC1MOD         | ;if 0 or 1 IC1 active_count TOFs |

|--------|------|----------------|----------------------------------|

|        | BMI  | OUT3TOF        | ; if neg, IC1 not active         |

|        | INC  | OVCNT1         | ;increment IC1 overflow count    |

| OU3TOF | LDAA | #\$80          | ;                                |

|        | STAA | REGBAS+TFLG2   | ;clear overflow flag             |

|        | RTI  | ;return from T | DF service                       |

|        |      | :              |                                  |

-

39

SV2IC1-Input Capture 1 service routine ...

| SV3IC1 | LDX  | #REGBAS      | ;point to top of register block         |

|--------|------|--------------|-----------------------------------------|

|        | INC  | IC1MOD       | ;\$FF $\rightarrow$ at 1st edge         |

|        |      |              | ;0 $\rightarrow$ at 2nd edge            |

|        | BNE  | N01ST3       | ; if not 0, this is not second edge     |

|        | CLR  | OVCNT1       | ;Zero the overflow count                |

|        | BCLR | TCTL2,X \$30 | ; EDG1B: EDG1A $\rightarrow$ 0:0        |

|        | BSET | TCTL2,X \$10 | ; EDG1B: EDG1A $\rightarrow$ 0:1 rising |

|        | LDD  | TIC1,X       | ;Read time of first edge                |

|        | STD  | RES1         | ;Save till next capture                 |

|        | BMI  | OU3IC1       | ;Done if IC was before any TOF          |

|        | LDAA | TFLG2,X      | ;Check for TOF IN MSB                   |

|        | BPL  | OU3IC1       | ;If no overflow ,you're done            |

|        | DEC  | OVCNT1       | ;This TOF shouldn't count               |

|        | BRA  | OU3IC1       | ;Done processing first edge             |

| NO1ST3 | LDD  | TIC1,X       | ;Get time of second edge                |

|        | BMI  | ARNOV1       | ;If MSB=1, skip TOF check               |

|        | TST  | TFLG2,X      | ;Check for overflow                     |

|        | BPL  | ARNOV1       | ; If no TOF, skip increment             |

|        | INC  | OVCNT1       | ;TOF was before edge so count it        |

| ARNOV1 | SUBD | RES1         | ;Time of last minus time of 1st         |

|        | STD  | RES1         | ;Update result                          |

|        | BCC  | RES10K       | ;Check for borrow                       |

|        | DEC  | OVCNT1       | ; If borrow, fix overflow count         |

| RES10K | BCLR | TCTL2,X \$30 | ;Disable IC1             |

|--------|------|--------------|--------------------------|

|        | BCLR | TMSK1,X \$04 | ;disable IC1             |

|        | BCLR | TMSK2,X \$80 | ;disable TOF             |

|        | LDAA | #1           |                          |

|        | STAA | IC1DUN       | ;Signal period measured  |

| OU3IC1 | BCLR | TFLG1,X \$FB | ;Clear IC1F              |

|        | RTI  |              | ;return from IC1 service |

#### The Connect Handshake for CCITT V.22bis Modems

The modem chip is programed for answering mode only. When we enter Figure 4.7 at the left, the calling modem has placed a call, heard ringback end (if it was listening) and is waiting to hear unscrambled binary ones from the answering modem. The answering modem went off hook when it detected ringing. The answering modem must be silent for two seconds after going off hook for billing protection. There are many places in the firmware needing time delay. The following program segment is an example of delaying two seconds.

Time Delay 2 sec routine ...

| LDAA | #\$7E   | ;Jump (extended) Opcode         |

|------|---------|---------------------------------|

| STAA | PVOC2   | ;Pseudo vector see manual text  |

| LDX  | #SV50C2 | ;address of OC2 service routine |

| STX  | PVOC2+1 | ;finish jump instruc to TOF svc |

| LDAA | #64     | ; value for delay 2 sec         |

| STAA | COUNT   |                                 |

41

Figure 4.7 CCITT V.22 Connect Handshake Sequence

|        | LDD  | #1         |                                |

|--------|------|------------|--------------------------------|

|        | STD  | DELAY      |                                |

|        | LDX  | #REGBAS    |                                |

|        | LDAA | <b>#</b> 0 |                                |

|        | STAA | TCTL1,X    | ;no change when compare ocurrs |

|        | LDD  | TCNT,X     | ;load current counter value    |

|        | STD  | TOC2,X     | ;store to compare register     |

|        | LDAA | #\$40      |                                |

|        | STAA | TFLG1,X    | ;clear any pending OC2F        |

|        | STAA | TMSK1,X    | ;enable OC2 interrupts         |

|        | CLI  |            |                                |

| WAIT1M | LDAA | COUNT      | ; wait here for 2 sec          |

|        | BNE  | WAIT1M     |                                |

## SV5OC2-Output Compare 2 service routine ...

| SV50C2 | LDD  | DELAY  | ;get delay time for 1/2 cycle |

|--------|------|--------|-------------------------------|

|        | ADDD | RTOC2  | ;add to last compare value    |

|        | STD  | RTOC2  | ;update OC2                   |

|        | LDAA | #\$40  | ;clear OC2f                   |

|        | STAA | RTFLG1 |                               |

|        | DEC  | COUNT  |                               |

|        | BNE  | EXIT   |                               |

|        | CLR  | RTMSK1 |                               |

| EXIT   | RTI  |        | ;return from OC2 service      |

This portion is main modem firmware program. For more information about the detail please refer to K-series Modem Design Manual [5].

#### 4.2.2 PC Side Software and Firmware Design

The image controller with data logger program running for modem is called IMAGEX. The operation and function of the IMAGEX is similar to IMAGE described by Mr. Qi [3]. The IMAGE program can run only for the local high speed add-on card designed by Mr. Feng [2]. To run with the modem, the only thing needed to do is to modify the driver. Because data compression is used on the controller side, the PC side includes a decompression program in IMAGEX.

#### Assembly language interface with C language

To interface assembly language subroutines with C, you must follow a few general guidelines. First, you must give a specific segment name to the code segment of your assembly language subroutine. For example, Microsoft C requires the segment name \_TEXT.

Second, your C compiler may require specific names for data segments (if the data is being referenced outside the code segment). Microsoft C require that the segment be named \_DATA.

Third, you must realize how variables are passed to assembly language subroutines through the stack. In the function-calling syntax of

#### function\_name(arg1,arg2,arg3,...,argn);

the values of each argument are pushed on the stack in reverse order. Thus, argument n (argn) is pushed on the stack first, and argument 1 (arg1) is pushed last. An actual value, or a pointer to a variable, can be passed on the stack although most values and pointer are passed as word-length stack elements, the longer data elements such as long or unsigned long-type variables require 32 bits (2 words) of stack space. If the memory model being used is compact, large, or huge, or if the data item has a segment override, data pointers also require 32 bits of stack space.

Fourth, in the assembly language source file, the assembly language routines to be called from Microsoft C must begin with an underline. However, the underline is not included when the routines are invoked in C.

Fifth, remember to save any special-purpose registers (such as CS, DS, SS, BP, SI, and DI) that your assembly language subroutine may disturb. Failure to save them may have undesired consequences when control is returned to the C program. You do not have to save the contents of AX, BX, CX, or DX because these registers are considered to be volatile by C; that is, the language assumes that you will change them and even requires you to do so in order to return a value.

The following program segment is an example of assembly subroutine interfacing with Microsoft C. assembly routine interfacing with C ...

```

.sıofil

proc

push

bp

bp,sp

mov

push

ds

push

es

push

di

push

si

ax,[bp+6]

;bx:buffer

mov

bx,ax

mov

ax,[bp+8]

;cx:165*192

mov

mov

cx,ax

;driver routine here.

:

:

si

pop

pop

di

pop

es

pop

ds

bp

pop

\operatorname{ret}

```

#### Initialization of 8250 UART

The 8250 UART is a serial interafec chip which convert parallel data into asynchronous serial data with programmable stop bit, parity bit, data bit, and one fix start bit. The basic asynchronous serial I/O functions and many others are built into the Universal Asynchronous Receiver/Transmitter, or UART. The idea behind a UART is to relieve programmer and processor of the toil associated with asynchronous serial I/O. To receiver and send data, the program simply reads and writes bytes to UART, which appears to the processor as one or more ordinary memory locations or I/O ports. The UART supplies the following four kinds of I/O ports to program: Input Status Port, Output Control Port, Output Data Port and Input Data port. The following program segment is to initialize the 8250 as 2400 baud, 8 bits, one stop bit, no parity bits, and internupt enable state. For more information about each register, please reference to "C Programmer's Guide to Serial Communications" [6].

#### INITIALIZE THE 8250 UART ...

| add | dx,3   | ;ADDRESS OF LINE CONTROL REGISTER       |

|-----|--------|-----------------------------------------|

| mov | al,80h |                                         |

| out | dx,al  | ;TO ADDRESS BAUD RATE DIVISOR REGISTERS |

| mov | dx,bx  | ;ADDRESS OF BAUD RATE DIVISOR LSB       |

| mov | al,30h | ;LSB VALUE FOR 2400 BAUD                |

| out | dx,al  |                                         |

| mov | dx,bx  | ;ADDRESS OF BAUD RATE DIVISOR MSB       |

| add | dx,1   |                                         |

47

| mov                      | al,0                             | ;MSB VALUE FOR 2400 BAUD                                                           |

|--------------------------|----------------------------------|------------------------------------------------------------------------------------|

| out                      | dx,al                            |                                                                                    |

|                          |                                  | ;THE BAUD RATE HAS NOW BEEN INITIALIZED                                            |

|                          |                                  | ;NOW INITIALIZE THE LINE CONTROL REGISTER                                          |

| mov                      | dx,bx                            | ;ADDRESS OF LINE CONTROL REGISTER                                                  |

| add                      | dx,3                             |                                                                                    |

| mov                      | al,03h                           | ;no PARITY, 1 STOP BIT, 8 DATA BITS                                                |

| out                      | dx,al                            |                                                                                    |

|                          |                                  | ;NOW INITIALIZE THE MODEM CONTROL REGISTER                                         |

|                          |                                  |                                                                                    |

|                          |                                  | ;FOR REQUEST TO SENT AND DATA TERMINAL READY                                       |

| mov                      | dx,bx                            | ;FOR REQUEST TO SENT AND DATA TERMINAL READY<br>;ADDRESS OF MODEM CONTROL REGISTER |

| mov<br>add               | dx,bx<br>dx,4                    |                                                                                    |

|                          |                                  | ;ADDRESS OF MODEM CONTROL REGISTER                                                 |

| add                      | dx,4                             | ;ADDRESS OF MODEM CONTROL REGISTER                                                 |

| add<br>mov               | dx,4<br>a1,03h                   | ;ADDRESS OF MODEM CONTROL REGISTER<br>;SET MODEM CONTROL SIGNALS                   |

| add<br>mov<br>out        | dx,4<br>al,03h<br>dx,al          | ;ADDRESS OF MODEM CONTROL REGISTER<br>;SET MODEM CONTROL SIGNALS                   |

| add<br>mov<br>out<br>mov | dx,4<br>al,03h<br>dx,al<br>dx,bx | ;ADDRESS OF MODEM CONTROL REGISTER<br>;SET MODEM CONTROL SIGNALS                   |

3F8H-3FFH are I/O addresses of COM1. In the thesis design, we choose COM1 as the 8250 address and reserved the flexibility to change it to any address. It is very easy to change the 8250 I/O address in software and hardware. In software design, simply modify 3F8H to 2F8H (COM2), 3E8H (COM3), or 2E8H (COM4). In hardware, adjust the modem card dip switch or serial card jumper to the selected I/O port. The following program segment is part of C showing easy change to different I/O address and the modern driver.

```

modem driver and I/O address ...

```

#define SIO1 0x3f8

```

int extern mexpo1( int sio, int time );

int extern inisio1( int sio );

int extern hayes( int sio, char *dial, char responce[] );

int extern siofil( unsigned char *a, int count );

int extern digital( int sio, int switches );

int extern analog( int sio, unsigned char *status );

```

#### 4.2.3 Startmodem Command used in the thesis

ATDn is the only command used in the thesis. The "D" command causes a telephone number to be dialed. N represents an ASCII string composed of dial digits and dial modifiers. For pulse dialing, the dial digits include the decimal value 0 through 9 and for Touch-Tone dialing, the digits 0 through 9 plus the symbols A, B, C, D, #, and \*. The D command also can combine with other dial modifiers such as T, P, R,; , .... which will be discussed later. Example: ATD 5965814

After the command ATD 5965814 is entered, your modem will auto-dial the telephone number 5965814. The P command causes your modem to pulse dial the numbers that follow. The T command causes your modem to touch-tone dial the numbers that follow. You can use the P command in combination with the T command when both pulse touch-tone dialing are required. The following program is a part of dialing-out driver written in 8088 assembly language.

Hayes Command driver ...

|         | mov  | ax,[bp+6] ;bx:sio address                            |

|---------|------|------------------------------------------------------|

|         | mov  | bx,ax                                                |

|         | mov  | <pre>si,[bp+8] ;si:hayes command string adress</pre> |

|         | mov  | di,[bp+10];di:modem response string adress           |

|         | cli  |                                                      |

| start:  | mov  | dx,bx                                                |

|         | add  | dx,5                                                 |

| ready?: | in   | al,dx                                                |

|         | test | al,20h                                               |

|         | jz   | ready?                                               |

|         | mov  | dx,bx                                                |

|         | mov  | al,[si]                                              |

|         | or   | al,al                                                |

|         | jz   | null                                                 |

|         | out  | dx,al                                                |

|         | inc  | si                                                   |

|         | jmp  | start                                                |

| null:   | mov  | si,di                                                |

| rec:    | add  | dx,5                                                 |

| ready2: | in   | al,dx                                                |

.

|        | test | al,01   |

|--------|------|---------|

|        | jz   | ready2  |

|        | mov  | dx,bx   |

|        | in   | al,dx   |

|        | mov  | [si],al |

|        | inc  | si      |

|        | cmp  | al,Odh  |