#### New Jersey Institute of Technology

## Digital Commons @ NJIT

**Theses**

**Electronic Theses and Dissertations**

5-31-1993

## Modeling and analysis of semiconductor manufacturing processes using petri nets

Xinyao Wang New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Wang, Xinyao, "Modeling and analysis of semiconductor manufacturing processes using petri nets" (1993). Theses. 2200.

https://digitalcommons.njit.edu/theses/2200

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

### Modeling and Analysis of Semiconductor Manufacturing Processes Using Petri Nets

#### by

#### Xinyao Wang

This thesis addresses the issues in modeling and analysis of multichip module (MCM) manufacturing processes using Petri nets. Building such graphical and mathematical models is a crucial step to understand MCM technologies and to enhance their application scope.

In this thesis, the application of Petri nets is presented with top-down and bottom-up approaches. The theory of Petri nets is summarized with its basic notations and properties at first. After that, the capability of calculating and analyzing Petri nets with deterministic timing information is extended to meet the requirements of the MCM models. Then, using top-down refining and system decomposition, MCM models are built from an abstract point to concrete systems with timing information. In this process, reduction theory based on a multiple-input-single-output modules for deterministic Petri nets is applied to analyze the cycle time of Petri net models. Besides, this thesis is of significance in its use of the reduction theory which is derived for timed marked graphs - an important class of Petri nets.

# MODELING AND ANALYSIS OF SEMICONDUCTOR MANUFACTURING PROCESSES USING PETRI NETS

by Xinyao Wang

A Thesis

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering

May 1993

## APPROVAL PAGE

## Modeling and Analysis of Semiconductor Manufacturing Processes using Petri Nets

Xinyao Wang

| ,                                                                                                           |

|-------------------------------------------------------------------------------------------------------------|

| 5/13/93                                                                                                     |

| Dr. Mengcha Zhou, Thesis Advisor Assistant Professor of Electrical and Computer Engineering, NJIT           |

| 5/12/93                                                                                                     |

| Dr. Anthony Robbi, Committee Member (date) Associate Professor of Electrical and Computer Engineering, NJIT |

| 5/12/93                                                                                                     |

| Dr. David Wang, Committee Member Assistant Professor of Computer and Information Science, NJIT  (date)      |

#### **BIOGRAPHICAL SKETCH**

Author: Xinyao Wang

Degree: Master of Science in Electrical Engineering

**Date:** May 1993

Date of Birth:

Place of Birth:

#### Undergraduate and Graduate Education:

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 1993

- Bachelor of Science in Electrical Engineering, Jiaotong University, Shanghai, P. R. China, 1991

Major: Electrical Engineering

To my family

#### **ACKNOWLEDGMENT**

I take this opportunity to express my deep gratitude to Dr. Mengchu Zhou, my thesis advisor for his invaluable support and guidance throughout the research and development of this thesis. I thank him for his patience and for all of his suggestions to refine and improve this research work as well as manuscript.

My sincere appreciation goes to Drs. Anthony Robbi and David Wang, who agree to work on the thesis committee, given the very short notice.

I would like to thank to all my friends for their support and encouragement during my studies.

## TABLE OF CONTENTS

| C! | hapter |                             | Page |

|----|--------|-----------------------------|------|

| 1  | INTR   | ODUCTION                    | 1    |

|    | 1.1    | Background                  | 1    |

|    | 1.2    | Motivation                  | 3    |

|    | 1.3    | Methodology                 | 4    |

|    | 1.4    | Objective                   | 5    |

| 2  | MUL    | TICHIP MODULE TECHNOLOGY    | 7    |

|    | 2.1    | Introduction                | 7    |

|    | 2.2    | Process Overview            | 10   |

|    | 2.3    | Technical Terminologies     | . 13 |

|    |        | 2.3.1 Preparation           | . 13 |

|    |        | 2.3.2 Patterning            | . 13 |

|    |        | 2.3.3 Etching               | . 14 |

|    |        | 2.3.4 Metallization         | 16   |

|    |        | 2.3.5 Dielectrics           | . 16 |

|    |        | 2.3.6 Joining processes     | . 17 |

|    |        | 2.3.7 Testing and packaging | . 18 |

|    | 2.4    | Challenge of MCMs           | . 18 |

| 3  | PETR   | I NET THEORY                | . 21 |

|    | 3.1    | Historical Review           | . 21 |

|    | 3.2    | Fundamentals                | . 22 |

|    | 3.3    | Basic Definitions           | . 24 |

|    | 3.4    | Properties of Petri Nets    | . 27 |

|    | 3.5    | Timed Petri Nets            | . 29 |

|    | 3.6    | Patri Nat Design Method     | . 29 |

| C | hapter | •                                               | Page |

|---|--------|-------------------------------------------------|------|

| 4 | REDU   | JCTION OF DETERMINISTIC TIMED PETRI NETS        | 32   |

|   | 4.1    | Fundamentals                                    | 32   |

|   | 4.2    | Calculations of Cycle Time                      | 34   |

|   |        | 4.2.1 A simple circuit                          | 34   |

|   |        | 4.2.2 Marked graphs                             | 34   |

|   |        | 4.2.3 Nets with multiple-weighted arcs          | 36   |

|   | 4.3    | Reduction of Timed Petri Nets                   | 40   |

|   |        | 4.3.1 Reduction approaches in marked graphs     | 40   |

|   |        | 4.3.2 Reduction example for an FMS cell         | 43   |

| 5 | MOD    | ELING AND ANALYSIS OF MCM PROCESSES             | 48   |

|   | 5.1    | Overview                                        | 48   |

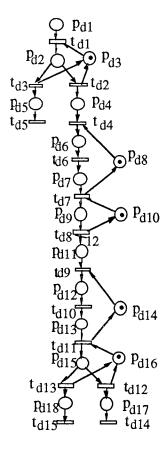

|   | 5.2    | System Description                              | 50   |

|   | 5.3    | Jobshops in processes                           | 50   |

|   | 5.4    | Augmentation with Time                          | 61   |

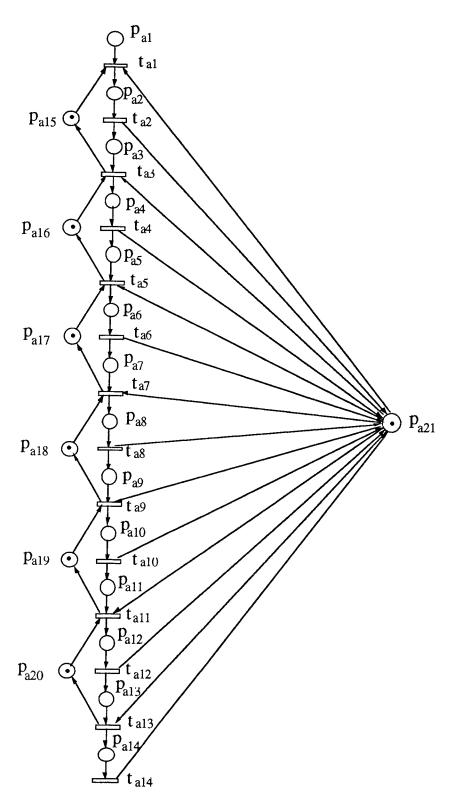

|   | 5.5    | Reduction Approaches                            | 63   |

|   |        | 5.5.1 Models of substrate processes             | 64   |

|   |        | 5.5.2 Models of 2-chip test process             | 66   |

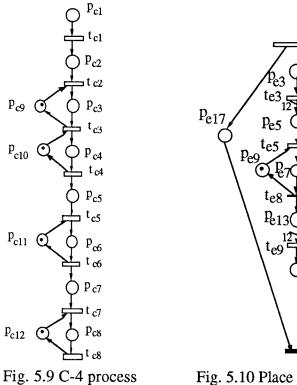

|   |        | 5.5.3 Models of C-4 process                     | 67   |

|   |        | 5.5.4 Models of testing and packaging processes | 68   |

|   | 5.6    | Overall Reduction                               | 68   |

| 6 | CON    | CLUSIONS                                        | 71   |

|   | 6.1    | Summary                                         | 71   |

|   | 6.2    | Suggestions                                     | 72   |

| R | REFER  | ENCES                                           | 74   |

## LIST OF FIGURES

| Figu | ure Pa                                                              | age |

|------|---------------------------------------------------------------------|-----|

| 1.1  | A control system for manufacturing processes                        | 3   |

| 2.1  | "Silicon circuit board" packaging for high density multichip module | 8   |

| 2.2  | Processes of IC fabrication                                         | 10  |

| 3.1  | An example of Petri net                                             | 23  |

| 3.2  | An example of State Machine                                         | 25  |

| 3.3  | An example of Marked Graph                                          | 25  |

| 3.4  | An example of Free Choice                                           | 26  |

| 3.5  | The relations of Petri nets                                         | 27  |

| 4.1  | A simple circuit                                                    | 34  |

| 4.2  | A marked graph with parallel paths                                  | 35  |

| 4.3  | Sequence with multiple-weighted arcs                                | 36  |

| 4.4  | A multiple-weighted circuit of n=4 and one of its reduced circuit   | 37  |

| 4.5  | A model of multiple-weighted marked graph                           | 38  |

| 4.6  | One-step reduction of a WMG model                                   | 39  |

| 4.7  | Reduction of a net with concurrent paths                            | 40  |

| 4.8  | Three-step reduction of subnet with concurrent paths                | 41  |

| 4.9  | Reduction of a net with loops in subnets                            | 41  |

| 4.10 | Reduction of subnets with tiokens in elementary paths               | 43  |

| 4.11 | Flexible manufacturing system cell                                  | 43  |

| 4.12 | The model of material handling system and the reduction processes   | 45  |

| 5.1  | A layout of a multichip module                                      | 48  |

| 5.2  | Overview of MCM processes (1)                                       | 49  |

| 5.3  | Overview of MCM processes (2)                                       | 51  |

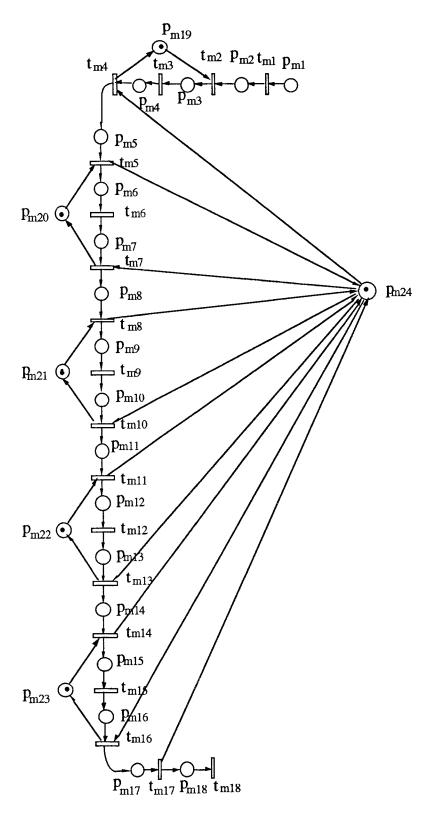

| 5.4  | Substrate processes                                                 | 53  |

| Fig  | ure P.                                          | age |

|------|-------------------------------------------------|-----|

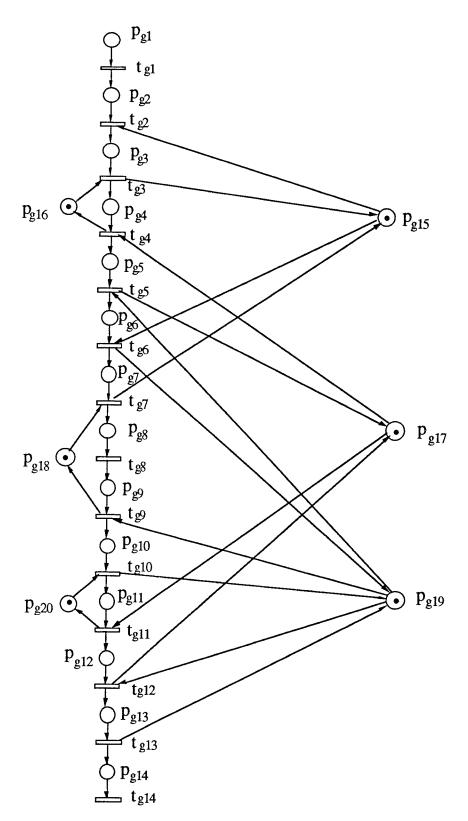

| 5.5  | CMOS process                                    | 55  |

| 5.6  | Ground and circuit process                      | 56  |

| 5.7  | Drill and coat solder process                   | 58  |

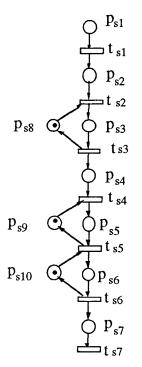

| 5.8  | Two-chip testing process                        | 58  |

| 5.9  | C-4 process                                     | 59  |

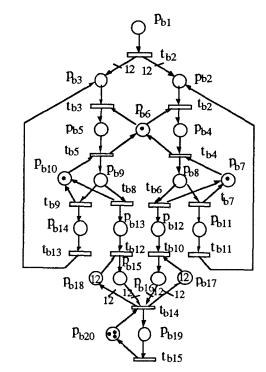

| 5.10 | Place chips on board process                    | 59  |

| 5.11 | Final package and test process                  | 60  |

| 5.12 | A p-t subnet                                    | 64  |

| 5.13 | Substrate fabrication and test process          | 65  |

| 5.14 | Equivalent graph of two-chip testing process    | 66  |

| 5.15 | Reduction process for place-chip-on-board model | 67  |

| 5.16 | Overview of MCM processes (3)                   | 69  |

| 5.17 | An MISO model of MCM processes                  | 70  |

## LIST OF TABLES

| Table Page                                                      |

|-----------------------------------------------------------------|

| 4.1 Description and time table for FMS cell                     |

| 4.2 Results of stepwise reduction for an FMS cell               |

| 5.1 Overview of MCM processes (1)                               |

| 5.2 Overview of MCM processes (2)                               |

| 5.3 Substrate process                                           |

| 5.4 CMOS process                                                |

| 5.5 Ground and circuit process                                  |

| 5.6 Drill and coat solder process                               |

| 5.7 Two-chip test process                                       |

| 5.8 C-4 process                                                 |

| 5.9 Place chips on board process                                |

| 5.10 Final package and test process 61                          |

| 5.11 Time information for CMOS process                          |

| 5.12 Time information for ground and circuit level 1 process 62 |

| 5.13 Time information for ground and circuit level 2 process 62 |

| 5.14 Time information for ground and circuit level 3 process 62 |

| 5.15 Time information for drill and coat solder process 62      |

| 5.16 Time information for place chips on board process 62       |

| 5.17 Time information for substrate process                     |

| 5.18 Time information for 2-chip test process 63                |

| 5.19 Time information for C-4 process 63                        |

| 5.20 Time information for Final package and test process 63     |

| 5.21 Delay time of subnets in the substrate process             |

| 5.22 Results of substrate fabrication and test                  |

| Table                                                        | Page |

|--------------------------------------------------------------|------|

| 5.23 Results of 2-chip test process                          | 67   |

| 5.24 Stepwise reduction in final testing and packaging model | . 68 |

| 5.25 Overview of MCM processes (3)                           | . 69 |

| 5.26 Conclusion of MCM processes                             | . 70 |

#### CHAPTER 1

#### INTRODUCTION

Being the case with the most advanced technologies, the drive towards high performance multichip packaging has given rise to a number of engineering challenges. These challenges can be grouped into three major categories [13]:

- 1. Design and fabrication of the thin film interconnections

- 2. Integrated circuited substrate compatibility

- 3. Module assembly and reliability

This thesis will discuss the basic processes required for fabricating thin film multilayer interconnection and multichip mounting, with the application of Petri nets to modeling and analysis of such manufacturing processes. Petri nets are a powerful tool for studying systems involving concurrency, synchronization and choices [44]. They can be used to analyze and evaluate important industry management indices, such as cycle time, firing rate, and sequence.

#### 1.1 Background

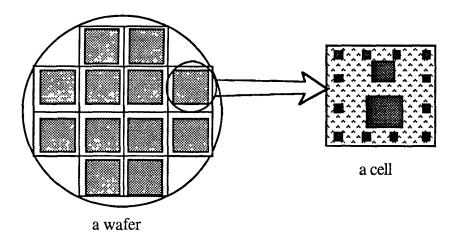

The term "multichip module" (MCM) may yield some confusion for those who are not intimately familiar with that technology. Simply stated, it is a new technology for integrated-circuit (IC) processing, which emerged in the late 1980s [18], and is considered as the most challenging technology in semiconductor industries in the 1990s [12, 26]. The distinguishing feature of multichip modules is that one or more pre-tested chips are mounted onto the circuited silicon wafer board, instead of the traditional IC fabricating

methods. This new technology addresses packaging problems in a manner that emulates a wafer scale while relaxing the limits imposed by having to repair defective cells [10]. It is being aggressively developed by several commercial firms and is also likely to find applications within the next couple of years [5]. In addition, the silicon wafer substrate provides a solid foundation for introduction of the advanced interconnection technologies.

A MCM manufacturing process can be described as a discrete event system (DES). As defined by Ramdgae and Wonham [28], "A DES is a dynamic system with a discrete state space and piecewise constant state trajectories, the time instant at which state transition occur, as well as the actual transitions, will in general be unpredictable."

The state transitions of a DES are called events and may be associated with the physical phenomenon that causes the change in state. For example, in a manufacturing environment, a typical event could be "machine A is working on part A". The purpose of modeling such a system is the design of a control structure to drive its state space trajectories, and a model should then provide a guide to constructing a controller. Once a model of the system has been constructed, the analysis and computation of the model turn ahead. Petri nets may be one of the efficient solutions to such a problem [7].

Petri nets are a graphical and mathematical modeling tool applicable to many DES's, such as manufacturing, control and information processes. As a graphical tool, Petri net can be used as a visual-communication aid similar to flow charts, block diagrams and networks. As a mathematical tool, it is possible to set up state equations, algebraic equations, and other mathematical models governing the behavior of systems. In a word, Petri nets can be used by both practitioners and theoreticians [26].

#### 1.2 Motivation

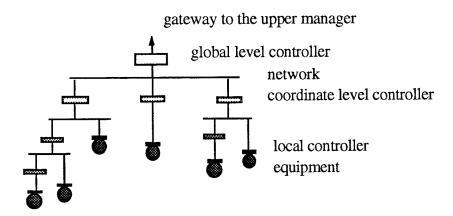

The real-time control of manufacturing systems for processing integrated circuit (IC) is a complex task including the real-time management of factory operation as well as its integration with the direct control of machines or robots. Generally, such systems are decomposed into various levels, each in charge of a certain class of decisions [24]. Basically, these levels are: local control of machines, coordinate level control, and global level control.

Fig. 1.1 A control system for manufacturing processes

To set up a control system like the example in Figure 1.1 is the real purpose of computer aid manufacturing processes. It realizes the real-time control in a manufacturing process. To a complex system, it is hard to expound the IC manufacturing processes in a word. Hence, modeling is a base for setting up control systems. For a large system, the modeling processes usually deal with several discrete sub-systems, and then mingle them together. Petri nets are an ideal tool for such work. Simulation is the critical step toward control systems, as it provides some useful parameters and detailed performance information. Programmed control is the way to convert the simulation model into a real-time system.

-

#### 1.3 Methodology

There are several requirements for good methodologies: the need to model from a global viewpoint through a top-down approach and in details through a bottom-up approach; the need to study not only the static but also the dynamic behavior, particularly when disruption occurs (this places an emphasis on simulation); and the need for a compatible model for the transition between construction, simulation, and implementation [41, 42]. In short, all of them bring to light the most important problem which is encountered with FMS (flexible manufacturing system) design: modeling.

We need models to describe and formalize manufacturing systems in the design process. These models can be used as a reference and a guide all through the design. To describe reality and to find specification errors during the design (rather than during implementation), we need powerful design tools. Such tools must be supported by computers, and so the requirement of formality. Finally, some methods are needed in order to organize the data acquisition in a structured way during the analysis and design process. In all, a methodology should be less sensitive to specification anomalies, rigorous enough to verify designs, and flexible enough to be implemented on a computer. Such a methodology will impart many desirable properties in a design such as ease of understanding and management, efficient implementation, and ease of debugging and maintaining the system. At last, this division will result in prototypes and in a system which has "distributed control" [11, 31].

Petri nets are a graphical and mathematical tool developed dozens of years, and verified that they are a powerful tool in modeling and simulation processes. Application of Petri nets to various fields in manufacturing systems have resulted in many successes [42,44]. In Petri nets, places represent availability of resources, operation processes, or

conditions, transitions model the events, start, or termination of operations, arcs indicate the relationship between places and transitions, and tokens in places present the dynamics to Petri nets with their flowing graphs. Thus, marked Petri nets can be used to study the dynamic behavior of the modeled DES.

#### 1.4 Objective

This research will apply Petri nets standard to the problem of modeling a control system for integrated circuit (IC) fabrication for multichip modules (MCMs). The literature, however, does not pay sufficient attention to the reduction theory for deterministic timed Petri nets (TPNs) so that setting up the foundation to this area is necessary before modeling, and more, it gives significant sight to the TPN systems. Modeling the IC manufacturing processes yields an architectural framework for the control system, which can be directly implemented via their conversion to computer code later. An analysis of the resultant designs will give insight to the system on the different levels. Along with a greater understanding of the particular automation needs of this industry, possible extensions and further avenues of exploration will be offered to the designers.

Chapter 1 presents an overview of the thesis while skimming through the MCM technology and fabrication, Petri net analysis, performance and challenges, and finally focusing on the purpose of the research.

Chapter 2 contains a summary of MCM technology, such as its challenges, processes and the comparison with other relative technologies - PCB and VLSI.

Chapter 3 is concerned with a Petri net methodology. An overview of its development, definitions and characteristics is given while focusing on the fundamental theories of Petri nets.

Chapter 4 provides the reduction theory of Petri nets. It is really mathematical and logical analysis. Importantly, it can ease up the problem of net-complexity in analyzing DPN systems.

Chapter 5 deals with the highlight in the whole report. Petri nets are applied to a fabricating system, which concerns the MCM technology. A critical evaluation will be offered in an attempt to set up the model of MCM manufacturing processes and data acquisition into different levels. This evaluation will be based on a variety of perspectives, from the theoreticians' view to operators'.

Finally, Chapter 6 summarizes the results and conclusions of the research. Along with the analysis and results in this research, avenues of the future research are suggested and discussed.

#### **CHAPTER 2**

#### MULTICHIP MODULE TECHNOLOGY

With the rapid advances in wafer fabrication technology, IC designers always attempt to increase wiring density and executing speed [37, 39]. Among the alternative new technologies, wafer scale integration (WSI) has the best opportunity to become a mainstream electronics technology, as it has quite high densities, large area monolithic circuits and hybrid substrate. Being a branch of WSI, multichip module (MCM) is rapidly being developed as an advanced packaging system expected to relieve the chip-to-chip interconnection limits imposed by the conventional packaging of individual ICs [3, 32, 33]. It appears that a significant opportunity now exists for development of MCM commercial product — large scale integrated circuits [21]. Hence, MCM technologies are considered as an important and longer term evolutionary direction for silicon ICs.

#### 2.1 Introduction

WSI has endured several infant and notorious commercial failures [1, 15]. But with the researches to develop the fundamental principles, which are needed as the underlying foundation for WSI components, WSI has received increasing attention as a major evolutionary direction in IC fabrication when the advantages of WSI become compelling over other advanced technologies [5, 16]. Multichip module (MCM), sometimes called as "hybrid WSI" or "pseudo-WSI" [15, 18], is the development of WSI, i.e., mounting the ready-made chips onto the silicon wafer circuited board. MCMs relieve the limitation of chip-to-chip interconnection imposed by the traditional IC packaging. Such an advanced

technique is essential to match the performance requirements (density and speed) of today's IC industry and more importantly the emerging VLSI (very large scale integration) technologies of silicon IC fabrications.

By using thin film technologies on large area substrates, the fabrication of MCMs draws out the techniques typically used for IC fabrication, as MCMs implement the passive interconnections in a MCM substrate. The similarity to IC technologies and resulting tight spacing of unpacked ICs promises higher density and higher speed "circuit boards". While an extensive set of references is provided to avoid repeating excessively detailed discussions available in the cited literature, this thesis provides a board overview of the objectives and motivations of the considerable work on the wafer level system components.

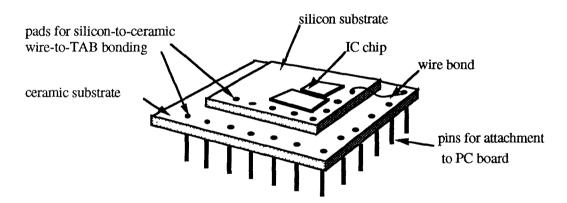

Fig. 2.1 "Silicon circuit board" packaging for high density multichip module

MCM technology provides the advantages of implementing conventional chip-to-chip interconnections with the more benign environment of "on-chip" interconnections [2, 39]. However, the use of thin film technologies does not eliminate several of traditional capabilities provided by conventional printed circuit board (PCB). Providing these PCB capabilities within the thin film technologies of MCMs is a major challenge. As a part of wafer scale integration, MCMs have had to confront similar requirements and have been unable to achieve commercial success. MCMs significantly relax the difficulty of achieving

higher yields through selective detection and repair of fault-producing defects since MCMs use passive interconnections (avoiding the need to consider defects within active devices) and have larger feature sizes than that of wafer scale ICs [29].

IC fabrication requires the use of mechanical and optical equipment and materials capable of precisely maintaining close tolerances and small geometry. As any high-technology field, a large amount of technical jargon has involved. It should be mastered by anyone wishing to be conversant with those working in the area [6, 8, 9, 30].

An *integrated circuit* (IC) is a combination of interconnected circuit elements inseparably associated on or within a continuous substrate.

A *monolithic IC* is an IC whose elements are formed in place upon or within a semiconductor substrate with at least one of the elements formed within the substrate.

A hybrid IC is a combination of two or more IC types or an IC with some discrete elements.

A wafer is a basic physical unit used in the process. It generally contains a large number of identical ICs.

A *substrate* is the supporting material upon or within which an IC is fabricated or attached.

A *test plug* is a special chip that is repeated only a few times on each wafer. It is used to monitor the process parameters of the technology. If the measurements of key parameters at the plug level are not acceptable, the wafer will be discarded.

A *test cell* is a special cell on each wafer. It differs from the test plug in that circuit designers include this cell specifically to monitor the performance of elementary subcircuits or subcomponents.

Considerable effort has been expended in the WSI field, toward using the entire wafer as a single IC, but this approach is challenged by defects in processing and associated decline in yield and by inherent delay in signals that must transverse the wafer. However, it is still a big challenge [36].

#### 2.2 Process Overview

The fabrication of ICs requires the execution of a large number of individual and general complex interactive operations. To provide an overview of the IC fabrication process, this section outlines these steps in approximately the same order in which they occur [13, 14, 26]. As mentioned in many papers, MCMs avoid repeating excessively detailed logic designs, but provide the interconnection system on the silicon circuited board, so that it saves much detailed work in the design.

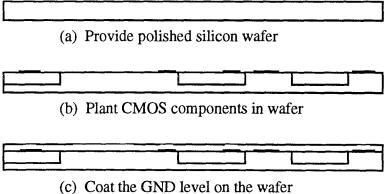

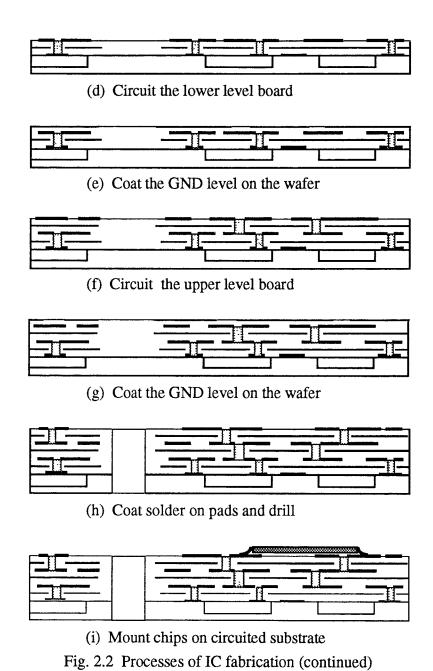

Fig. 2.2 Processes of IC fabrication (to be continued)

Figure 2.2(a), it shows a polished silicon wafer to the fabrication work-stations.

Figure 2.2(b) shows the process of planting CMOS switches and other simple transistors in the polished substrate. In most papers on multichip modules [6, 10, 26], this step is ignored, as the authors always emphasize on the advantages of silicon circuited

board. But in some cases, this step is valuable, as it can reduce the errors of assembly in chip-to-chip interconnections. Needless to say, the reliability of VLSI CMOS technologies is higher than that of chip-to-chip interconnections [40], so that planting CMOS devices on the raw substrate is the first step in such a system.

In Figure 2.2(c), there are two steps: plating dielectric and metallizing the first GND level. First, silicon dioxide is planted as the interlevel dielectric. Metallization is the next step to the dielectric. GND layer is used to avoid the electrical-magnetic impact between two circuited layers.

Figure 2.2(d) includes two steps: dielectric and metallization. Polyimide is applied as interlevel dielectric. The goal of metallization is to settle the lower level circuits and interconnecting with CMOS devices. It is done in the same way as that of Figure 2.2(c). Obviously, the metallization process here is much more difficult than that of GND level.

The processes from Figure 2.2(e)  $\sim$  2.2(g) are similar to that of Figure 2.2(c) or Figure 2.2(d). In these processes, the upper level of the circuit is patterned and there are GND levels between two neighboring circuited levels. Polyimide is planted as dielectric between any different metal levels.

As shown in Figure 2.2(h), the upper level circuit is provided to the silicon circuited board, and I/O pads for chip-to-chip interconnections and bonding pads for packaging are planted in this process. Solder is supplied on the I/O pads finally.

Finally in Figure 2.2(i), the joining process for chip-to-substrate interconnections is realized. The ready-made chips are mounted onto the substrate under the C-4 (controlled collapse chip connection) technology.

#### 2.3 Technical Terminologies

The IC fabrication processes have many special terminologies, which relate to the detailed work in fabrication of MCMs. It should be made clear during the research [6, 8, 17, 22, 30, 35, 36, 38].

#### 2.3.1 Preparation

Once wafers have properly prepared, they should be pretreated before any fabrication processes.

The wafers are chemically and mechanically cleaned to remove dust and other forms of airbone and human contamination. They are then forced dried and given a short bake to remove residual surface moisture permitting good resist adhesion. The wafer is coated immediately after prime.

#### 2.3.2 Patterning

Patterning is the essential process in the IC fabrication processes which is an imaging process for metallization and interconnections. This complicated process can be divided into several steps.

Coating: coating is always performed in the environment with solvent exhaust. The overall objective of this step is to provide a uniform and defect-free layer of a photo- or electro- sensitive masking material. Spin coating is a widely used technique for applying photoresist to wafers.

Softbaking: softbaking is used to remove the solvents present in the spin-coating film of photoresist and is usually performed immediately down stream from the coater in a track-type wafer handling system.

Exposure: the goal of exposure is to transmit a latent image of a desired pattern into the photoresist film. The role of photomask is obviously paramount, since the mask is a passive tool that gives the photoresist its latent image. It must therefore be as clean and defect-free as the coated and softbaked wafer is hopefully.

Development: in-line wafer developing is widely used now. It carries each wafer alone a track, where it is placed under a stream or spray of developer for a predetermined time. Rinsing and drying follow the developer step, the parts are agitated, to provide uniform developing action. The development process is one in which the developer selectively attacks and removes either exposed regions (positive resist) or unexposed region (negative resist) leaving behind image to serve as the mask for etching, or, in some case, metallization.

*Postbaking*: postbaking provides "insurance" that the resist is bonded well to the underlying oxide. But it is not always used. And the process is the same as that of softbaking.

#### 2.3.3 Etching

Wet- and dry-etching techniques are widely used in developing, batch, and in-line processing. The goal is to precisely remove the semiconductor layer exposed by the developing process. Complete removal of developed resists essential and any residues left on the semiconductor layer may prevent or inhibit an etching action, a phenomenon called "blocking".

Silicon dioxide etching: The most common etching application in IC fabrication is etching undoped SiO<sub>2</sub>. Removing selective areas of the initial undoped oxide is done by imaging the oxide with photoresist to protect those areas on which the oxide will not be etched. Since most resists bond ready to undoped SiO<sub>2</sub> and the etchant is not corrosive to the resists commonly used, the etching application is relatively easy to perform and simple to control. Etching doped silicon dioxide is more difficult than that of the undoped. Phosphorous-doped SiO<sub>2</sub> is the most common application in this category, where openings are made in the doped layer to provide for aluminum ohmic contacts. After etching the phosphorus-doped contact holes, aluminum is evaporated over the wafer and flows into these holes to make electric contact with the silicon.

Polyimide etching: Polyimide layers are etched in aqueous solvent solutions or reactive-ion etched using very thick coatings of resist as a sacrificial mask layer. "Sacrificial" etching involves the application of the photoresist coating that is thicker than the layer to be etched. After imaging the resist, the wafer is placed in the reactive-ion etch chamber and both polyimide and photoresist are removed or etched at the approximately same rate. Since the photoresist is thicker than the underlying polyimide, the polyimide layer is etched through first and the etching is terminated, leaving a thin layer of photoresist that was not sacrificed in the etching to protect the polyimide layer needed for insulation or protection of the ICs.

Aluminum etching: Since aluminum metallization serves as the interconnection layer for all the devices on the chip. Aluminum is imaged with positive photoresist mostly. Aluminum etching is accomplished with both wet and dry etchants, and both approaches are capable of meeting IC fabrication.

*Removal*: Photoresist removal is typically done in a batch mode, by immersing wafers in a heated resist-stripping solution or placing them in a batch plasma-stripping chamber, when an oxygen plasma removes the resist. The goal is to leave behind a surface defects in doping or metallization processes.

#### 2.3.4 Metallization

Metallization is used in the interconnection layer on the ICs, making ohmic contact to the devices formed in the silicon and connecting these to the bonding pads on the chip's edge. The choice of metal in a multilevel interconnection structure is based on its resistivity, cost, adhesion properties to the dielectric layer, deposition technique, and resistance to long-term corrosion. The three metals of choice are gold, aluminum and copper for their superior conductivity and ease of deposition. Aluminum is used here because it adheres well to both silicon and dielectric, it can be easily vacuum deposited, and it has high conductivity. In addition, small amount of copper is added to reduce the potential for electromagnet effects, where current applied to the device induces mass transport of the metal. Small amount of silicon is also added to aluminum metallization to reduce the formation of metal "spikes" that occur over the contact holes. In some cases, titanium is added for the same reason.

Aluminum sputtering is commonly used in IC metallization processes, and is popular because the adhesion of deposited metal is excellent. It is done by ionizing inert-gas particles in an electric field (producing a gas plasma) and then directing them toward the source or target, where the energy of these gas particles physically dislodges, or "sputters off", atoms of the aluminum or other source materials.

#### 2.3.5 Dielectrics

Dielectric materials are planted to isolate any metal layers. The purpose of coating dielectric is not only to isolate any two metal layers, but to protect the ready-made layers. Oxidation

of silicon is perhaps the most fundamental of all processes used in IC fabrication. Silicon dioxide (SiO<sub>2</sub>) is a very stable material and is almost universally used as the surface for resist-imaging operation. Silicon interacts with oxygen. High-pressure oxidation, operating at up to 25 atmosphere (atm), permits better product.

Polyimide is also used as insulating layers, most notably between two metal layers. Polyimide tends to smooth abrupt underlying irregularities, thus reducing the effects of sharp boundaries of underlying metal layers. Spin coating is widely used in this process.

Diffusion: "Diffusion", in a classical sense, is the uniform distribution of particles within a fixed volume of space according to a physical mechanism that begins with the same particles in a concentrated state in the same fixed volume. The IC analog of this physical behavior is the thermally induced distribution of impurity atoms throughout the silicon crystal-lattice structure.

#### 2.3.6 Joining processes

The controlled collapse chip connection (C-4) technology [32, 36] is applied for chip-to-substrate interconnections. As a two-dimensional interconnection by nature, C-4 has the small inductance and capacitance of the solder joints compared with bonding wires or TAB (tape automated bonding) leads. The key feature of the C-4 technology is the deposition of a thin film structure and solder on the I/O pads. The thin film structure, usually termed ball-limiting metallurgy (BLM) or under-bump metallurgy (UBM), serves the purpose of an adhesion layer, a diffusion barrier, and a solderable base of controlled wetting area. The solder pads are aligned and tacked onto the matching footprint on the substrate, and connection to the substrate is made during the reflow of the deposited solder. The surface tension of the molten solder prevents the chip from collapsing during reflowing.

Evaporation through metal masks and electroplating is known as the method of solder deposition. In a solder evaporation process, mechanical fixtures are necessary to align and clamp the metal mask to the wafer or to the substrate.

Reflow of deposited solder pads in  $N_2$  is successful because it avoids reflowing the bumped dies before they are tacked for joining.

Implementation of this process could be simpler if the chips are specially designed for the C-4 process, namely having small circular via openings of uniform size in an area array format located near the center of the die.

#### 2.3.7 Testing and packaging

After being processed, ICs are tested and packaged. The first step in a testing process generally involves a process verification to make certain that the process parameters are within the tolerances acceptable for the product, and test plugs are specially designed for this purpose. Then a wafer prober is used to make mechanical contact with the test plugs so that electrical measurements can be made. After being probed, the wafer is scribed both horizontally and vertically between adjacent dies, and the dies are separated. Following the separation, the individual dies are die attached, or die bonded, to a carrier or to the IC package itself. Wire bonds, typically gold, are subsequently made from the pins of the package to the appropriate locations on the die. After wire bonding, the packages are closed, and a final electrical test is completed.

#### 2.4 MCMs vs PCBs and VLSIs

Multichip modules reflect physical characteristics which are shown partially in two distinct technologies — printed circuit boards (PCBs) and VLSI integrated circuits. Experiences within these technologies provide a foundation for development of MCM techniques, and are briefly summarized below.

PCBs, developed over many years, provide a very flexible platform on which complex systems comprised of large number of components can be assembled. The advantages of PCBs are:

- a. Usage of pretested components

- b. Inspectability

- c. Repairability and adaptability

- d. Ease of assembly

The disadvantages of PCBs are:

- a. Large components

- b. Large size

- c. Exposure to the air

Compared with PCBs, MCMs are also assembled with a lot of components, and inspectable and repairable, but more difficult than PCBs, as MCMs are of mini-size. MCMs integrate the circuits and components. Furthermore, they are sealed in a LCC (leadless chip carrier) package [29].

The VLSI technology has been developed for more than ten years. And it is still the mainstream in IC fabrication industries. The advantages are:

- a. Small size but large scale integration

- b. Inspectability (but more difficult than that of PCBs)

- c. Isolation of the air

The disadvantages are:

- a. Unrepairability

- b. Repeatedly detailed work

Compared with VLSI, MCM technology provides an environment for designers to use ready-made components without repeating the detail, and for operators to repair the defect components or the defect areas on substrates. It provides the flexibility of design and operation in IC fabrications. Furthermore, MCMs preserve the advantages of VLSI technology [40].

Multichip modules have qualitative similarities to the technologies discussed above, and it is the technology in relation to both PCB and VLSI technologies. But it is also clear that MCMs have unique characteristics which will make direct use of manufacturability techniques difficult from those other technologies.

Multichip modules represent the extension of the microfabrication and thin film techniques from the arena of the device structures into the arena of the system-level interconnections. MCMs address the high density, chip-to-chip interconnections using VLSI technologies. For such reasons, MCMs are presently evolving rapidly towards a commercial, generic packaging of IC components.

## CHAPTER 3

### PETRI NET THEORY

Modeling and analyzing large scale discrete event systems (DES's) present a big challenge. As a graphical and mathematical modeling tool, Petri nets provide strong reliability and computability for the study of DES. As a graphical tool, they can be used as a visual-communication aid, similar to flow charts, block diagrams and networks. In addition, tokens are used in these nets to simulate the dynamic and concurrent activities of systems. As a mathematical tool, they make it possible to set up state equations, algebraic equations, and other mathematical models governing the behavior of systems. Shortly, Petri nets are flexible and powerful so that they could be used not only by practitioners, but also by theoreticians [25, 31]. To some extent, for large scale systems, Petri net could be so complicated that they would lead to the problem of state space explosion. Out of question, simplification and reduction methods for the Petri net system become more important than that of any previous time [19, 20]. This research also faces to this complexity problem, and thus the reduction theories are applied to the analysis of MCM manufacturing processes.

#### 3.1 Historical Review

Historically speaking, the concept of "Petri net" has its origin in Carl Adam Petri's dissertation, University of Darmstadt, West Germany, 1962 — "Kommunikation mit Automaten" (Communication with Automata). In the early development of Petri nets (in the late 1960's and early 1970's), the pioneers used it in some control systems. Because of

the original Petri nets lack some conditions (such as firing rate, firing time), the applications were confined to a narrow area. Since 1979, the Europeans have been very active in organizing workshops and publish conference proceedings on Petri nets. More than four tutorials were brought out. Year by year, Petri nets became more and more noticeable and popular for describing and studying the information processing systems that are characterized as being concurrent, asynchronous, distributed and/or parallel. From 1985, another series of international workshops were initiated. These series place emphasis on time and stochastic nets and their applications to performance evaluations. They are called timed-Petri net and stochastic-Petri net, respectively [25]. Petri nets become a practical tool for real-time control systems. Nowadays, Petri nets are widely applied in manufacturing control systems, discrete event systems, data-flow computing systems, fault-tolerant systems, asynchronous circuits and structures, compiler and operating systems, and so on. There are many kinds of Petri nets. Generally, they are classified into ordinary Petri nets, deterministic timed Petri nets, stochastic Petri nets and colored Petri nets, and they can also be trans-sorted to two or more classes. For different systems, different Petri nets are created and applied. The theories of Petri nets are developing so quickly that they become one of the most powerful tools to study discrete event systems [28]. This chapter indicates the essential elements of Petri nets.

#### 3.2 Fundamentals

A Petri net is a directed graph consisting of two types of nodes, places and transitions. Places always follow transitions and vice versa. Places and transitions are connected by directed arcs.

Formally, an ordinary Petri net is defined as

$$Z = (P, T, I, O, m)$$

where P: a set of places represented by circles,

T: a set of transitions represented by bars,

I:  $P \times T \rightarrow N$ ; the number of arcs from p to t, where  $N=\{0, 1, 2, \dots\}$

O:  $P \times T \rightarrow N$ ; the number of arcs from t to p, and

m: a vector whose ith component represents the number of tokens in ith place.

I, O are two functions connecting transitions with places: I is the input function, and O, the output. They are both represented as matrices. These four items: set of places, set of transitions, input function and output function, define the structure of the Petri net.

Fig. 3.1 An example of Petri net

A Petri net graphically consists of

- 1. *Circles* (called places) represent conditions or availability of resources, e.g., "machine 1 available", "parts on machine 1".

- 2. Bars (called transitions) represent the initiation or termination of an event. There are two kinds of bars, vacant bars stand for deterministic timed transitions, i.e., there is timedelay when firing such a transition, and solid bars stand for immediate transitions i.e., zero time-delay.

- 3. *Black dots* (called tokens) in resource places, represent the availability of the corresponding resources.

- 4. Arcs represent the direction of the operating resource flow.

A transition  $t \in T$  is enabled by a marking m if  $\forall p \in P$

$$m(p) \ge I(p,t)$$

The firing of transition t generates a new marking m' with:

$$m'(p) = m(p) + O(p,t) - I(p,t).$$

#### 3.3 Basic Definitions

First, denote preset and postset as follows:

preset of place p

$$p = \{t: t \in T \& O(p,t) \neq 0\},\$$

postset of place p

$$p' = \{t: t \in T \& I(p,t) \neq 0\},\$$

preset of transition t

$$t = \{p: p \in P \& I(p, t) \neq 0\},\$$

postset of transition t

$$t' = \{p: p \in P \& O(p, t) \neq 0\},\$$

## Reachability set is:

A marking m' is immediately reachable from m if firing an enabled transition in m yields m'. Given the initial marking m<sub>0</sub> of the Petri net, it is called reachability set or forward marking class (denoted by  $R(m_0)$ ) — the set of all possible reachable markings. In

other words, a marking m belongs to  $R(m_0)$ , if there exists a firing sequence q leading from  $m_0$  to m, i.e.,

$$R(m_0)=\{m| \exists q \in T^*, q[m_0>m]\}$$

where T\* represents the set of all possible orders of the elements in T, and  $q[m_0>m]$  denotes that firing q at  $m_0$  leads to m.

Ordinary Petri nets (OPN)

$I(p,t)\le 1$ ;  $O(p,t)\le 1$  for any places and transitions.

i.e., there are not any multiple arcs in the graph.

Fig. 3.2 An example of State Machine

State machine Petri net (SM)

An ordinary Petri net with

|'t|=1; |t'|=1 for any transitions in a graph

i.e., tokens will not increase or decrease during firing any transitions.

Fig. 3.3 An example of Marked Graph

Marked graph Petri net (MG)

An ordinary Petri net with

| p|=1; |p'|=1 for any places in a graph

i.e., tokens in any cycle is constant, no matter which transition fires.

Free choice Petri net (FC)

An ordinary Petri net with

either  $|p_i| \le 1$  or  $(p_i) = \{p\}$  for any place in graph

i.e., each arc from a place is either single outgoing or unique to a transition.

Fig. 3.4 An example of Free Choice

## Extended Petri net (EPN)

A general Petri net with inhibitor arcs, probabilistic arcs or random switches, priority functions and so on.

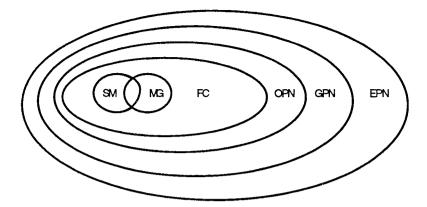

The relationship among these graphs are shown in Figure 3.5.

Once a model of Petri net is set up, analysis is desirable to determine which properties the net possesses.

Fig. 3.5 The relations of Petri nets

### 3.4 Properties of Petri Nets

### 1) Boundedness

A place is K-bounded if there exists an upper bound to the number of tokens that can be simultaneously held in the place. A Petri net is K-bounded, if each place in the net is bounded and the maximum bound is K. A 1-bounded net is said to be safe.

In manufacturing environments, the boundedness of a system indicates the absence of overflows. In other words, if a system is not bounded, i.e., at least a place is not bounded, it will become a trap to absorb tokens, and then the further steps become meaningless. Therefore, a model of real systems should be bounded for any initial markings.

### 2) Liveness

A transition is live if there exists a sequence g for any marking m in the system, firing g at m will lead to a marking that enables t. A Petri net is live if all of its transitions are live.

Liveness implies no deadlock. If a transition cannot fire, it is a redundant transition and can be eliminated from the net. However, it needs to be identified since it may represent an error in the model or an inconsistency in the modeling system.

In manufacturing environments, the liveness of a system indicates the system can run well, without causing the system deadlocked. Thus, the liveness is a most important property in the system analysis. In a live net, not only a transition is firable in any given marking at least, but also it keeps the firing potent in all marking reachable from any initial marking.

### 3) *Reversibility*

A Petri net is reversible if for any marking, it can go forward and reach the initial marking, i.e., the initial marking is reachable from any reachable markings.

In manufacturing environments, the reversibility means the system will be restarted. Generally, when a part is finished in the process, it will input a new part automatically.

#### 4) Conservation

A Petri net is conservative if the number of tokens in the net keeps constant. It implies that each transition in such a net is conservative, in the sense that the number of inputs of each firable transition is equal to that of outputs. More generally, weights can be defined for each place allowing the number of tokens to change as long as the weighted sum is constant. It guarantees the system resources are neither destroyed nor created.

### 5) Persistency

A Petri net is persistent if for any two enabled transitions firing one does not disable the other. In other word, a transition in a persistent net, once it is enabled, will stay enabled until it fires.

#### 3.5 Timed Petri Nets

The concept of time is not given in the original definitions of Petri nets. However, for performance evaluation and scheduling problems of dynamic systems, it is at present necessary to introduce time delays associated with transitions and/or places.

It is interesting in finding how fast each transition can initiate firing in a periodically operated timed Petri net. An important parameter is cycle time, which is defined as the time to complete a firing sequence leading back to the starting marking after firing each transition at least once.

In a deterministic timed marked graph, one can assign the delay-time  $\tau_i$  to each transition. The total delay in a directed cycle is the sum of the delay-time of all transitions in that cycle. Compared with that of other cycles, a maximum delay time can be obtained and is the cycle time of such a net, i.e.,

$\pi_{\min} = \max\{\text{the total delay in } C_k / m_0(C_k)\}$

where  $m_0(C_k)$  denotes the number of tokens in cycle  $C_k$  at  $M_0$ .

As defined, the number of tokens in a cycle remains unchanged in an MG during firing sequences.

### 3.6 Petri Net Design Method

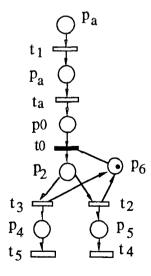

Since in a moderately sized manufacturing system, the complement level of detail may be unreasonable, there exist two paths — top-down method and bottom-up method. Top-down method sets up an aggregate model and neglects the low-level details initially, then refines the system by expanding places and/or transitions to incorporate details into the models. In contrast, bottom-up method first classifies them into subnets, models each subnet, then merges them together by sharing nodes in the system [41, 42, 44].

## Top-down techniques

Transitions and places in a net can be replaced by a more detailed sub-net step by step. This method is very attractive from the design point of view because details are introduced step by step, thereby, reducing the complexity to be dealt with at any phase in the process. Using this method, it is easy to analyze the properties of the net, such as liveness, boundedness, reversibility and others.

A Petri net model can be derived for a manufacturing system given a list of operations and their relations. The procedure is outlined as follows:

- Step 1. Set up an aggregated model of the system with properties of boundedness, liveness and reversibility.

- Step 2. Perform decomposition and refinement

- Step 3. Appropriately add the places to represent the availability of resources.

This top-down approach method is a natural decomposition of a manufacturing system.

### Bottom-up techniques

In the bottom-up method, synthesis can start with a very simple separated net, then at each synthesis step, these subnets can be merged into new nets, with sharing places and/or transitions. The procedure is:

- Step 1. Separate the objective into some separate operations and set up simple subnets corresponding to the detailed operations.

- Step 2. Add the resource places to the subnets

- Step 3. Merge the subnets by sharing the common places, transitions or paths.

The bottom-up method is very natural from the view of the operators, as it goes from the detailed activities to the top-level outlines.

Being a graphic and mathematic tool, Petri net applies a strict theory for modeling and analysis. Facing a big system, we can separate it into several small-sized subsystems, using the top-down or bottom-up method. Then the system will be made clear and analyzed through the subnets, and finally synthesized.

## **CHAPTER 4**

## REDUCTION OF DETERMINISTIC TIMED PETRI NETS

Development of Petri nets brings light to the discrete event system (DES) analysis. However, one faces the exponential growth of the state space with net size and the number of jobs and resources. The net becomes more and more complicated and unreadable. To challenge such a problem, we resort to a general methodology — reduction. This chapter investigates reduction theory for the deterministic timed Petri net (TPN).

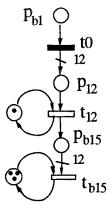

#### 4.1 Fundamentals

A timed Petri net is a six-tuple set

$$Z=(P, T, I, O, m_0, \tau)$$

where P, T, I, O, m<sub>0</sub> are defined in the last chapter, and

$\tau$ : the set of firing time functions and  $\tau_i$  is used to denote the time delay associated with the i<sup>th</sup> transition.

All delays are deterministic. Denote these timed Petri nets by TPNs in this thesis.

An elementary path is a sequence of nodes:  $x_1x_2...x_n$ ,  $n\ge 1$ , such that  $\exists$  an arc  $(x_i, x_{i+1})$ ,  $1\le i< n$  if n>1, and  $x_i=x_j$  implies that i=j,  $1\le i$ ,  $j\le n$ . An elementary circuit is  $x_1x_2...x_n$ , n>1 such that  $x_i=x_j$ ,  $1\le i< j\le n$ , implies that i=1 and j=n. A PN is strongly connected if for every pair of vertices  $v_i$ ,  $v_j\in P\cup T$ , there exists an elementary path from  $v_i$  to  $v_j$ , i.e., vertices in the net can definitely connected with directed paths from each other.

As discussed in Chapter 1, the analysis of deterministic timed Petri nets faces the complexity problem. Therefore, reduction techniques need to be used to mitigate the effort of checking Petri net properties. The reduction steps should not lose important properties about the net.

First, introduce the following some definitions about subnets [19].

**Definition 1.** Z'=(P', T', I', O') is a subnet of Z=(P, T, I, O) if  $P' \in P$ ,  $T' \in T$ , and if there exist I'(p, t)=I(p, t), O'(p, t)=O(p, t) for any  $p \in P'$  and  $t \in T'$ . It is also written as

$$Z\supset Z'$$

.

Then the input place set of Z' is

$$P_{in} = \{ p \in P' : \exists t \in p \& t \notin T' \}$$

the output place set of Z' is

$$P_{out} = \{ p \in P' : \exists t \in p' \& t \notin T' \}$$

the input transition set of Z' is

$$T_{in} = \{t \in T': \exists p \in t \& p \notin P'\}$$

the output transition set of Z' is

$$T_{out} = \{t \in T': \exists p \in t' \& p \notin P'\}$$

**Definition 2.** Given  $Z \supset Z'$ , Z' is a place subnet/block iff  $P_{in} \ne 0$ ,  $P_{out} \ne 0$ ,  $T_{in} = 0$  and  $T_{out} = 0$ ; Z' is a transition subnet/block iff  $P_{in} = 0$ ,  $P_{out} = 0$ ,  $T_{in} \ne 0$  and  $T_{out} \ne 0$ ; Z' is a p-t subnet/block iff  $P_{in} = 0$ ,  $P_{out} \ne 0$ ,  $T_{in} \ne 0$  and  $T_{out} \ne 0$  and  $T_{out} \ne 0$  and  $T_{out} \ne 0$ .

**Definition 3.** A TPN Z" is called an equivalent subnet of a marked graph Z', iff under the same markings, 1) the delay time from any input node to any output node in Z" equals to that of Z'; and 2) the number of nodes in Z" is less than that of Z'.

## 4.2 Calculations of Cycle Time

We are always interested in how fast each transition can initiate firing in a periodically operated TPN. As stated earlier, cycle time is the time to complete a firing sequence leading back to the starting marking after firing each transition at least once. On reducing deterministic Petri nets the delay time calculation is critical.

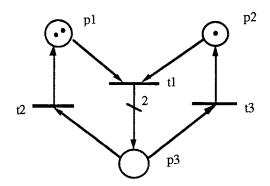

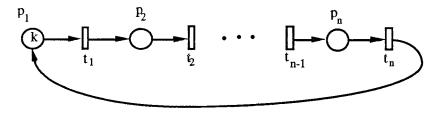

### 4.2.1 A simple circuit

The cycle time for the simple circuit as shown in Fig. 4.2, is

$$\pi = \frac{\sum \tau_i}{m_C}$$

where  $\tau_i$  is the delay time of i<sup>th</sup> transitions associated to the circuit,

m<sub>C</sub> is the total number of tokens in the cycle

Fig. 4.1 A single circuit

One should notice that the cycle is associated with the number of tokens in the cycle as well as the total delay time of the cycle. In Fig. 4.1, transitions  $t_1$ ,  $t_2$ ,  $t_3$ , ...,  $t_n$  can be concurrent iff they are all enabled, and furthermore, transition  $t_i$  can pass any number of tokens simultaneously. Under such conditions, the formula above is obtained.

### 4.2.2 Marked graphs

In a marked graph, its cycle time is

$$\pi_{\rm C} = \max(\pi_1, \, \pi_2, \, ..., \, \pi_{\rm D})$$

where  $\pi_i$  (1 $\leq i \leq n$ ): the cycle time of  $i^{th}$  circuit.

Furthermore, this formula can be applied to many other deterministic timed Petri nets to compute the deterministic time delay and search critical cycles which bound the system performance.

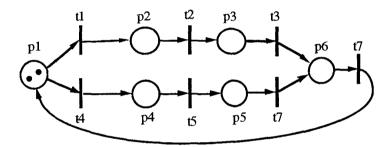

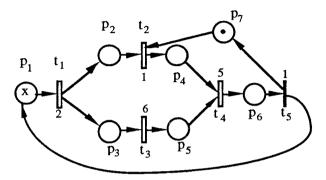

Fig. 4.2 A marked graph with parallel paths

There are three loops in Fig. 4.2, and

$$\pi = \max(\frac{14}{x}, \frac{9}{x}, 7)$$

Definitely,  $\frac{14}{x} > \frac{9}{x}$  for x is a positive integer. If x=1, the cycle time  $\pi$  depends on the big loop  $p_1t_1p_3t_3p_5t_4p_6t_5p_1$ , i.e.,  $\pi=14$ ; and the idle time in loop  $p_7$  is 14-7=7, i.e., the efficiency of control loop  $p_7t_2p_4t_4p_6t_5p_7$  is 50%. But if x>2,  $\pi=7$ , which is independent of the big loop and the initial tokens in place  $p_1$ . When x=2, both delay times in these loops are 7. It means there is no waiting time either loop, and at this time the efficiency of the system and the utility is the highest. In conclusion, the assignment of tokens in resource  $p_1$  and control place  $p_7$  can affect the system optimum, and here  $m(p_1)=2\times m(p_7)$  is the best assignment of tokens for the net in Fig. 4.2.

The calculation of cycle time for marked graph is the foundation of deterministic timed Petri nets. In other words, the calculation of other types of Petri nets follows after their conversion to marked graphs.

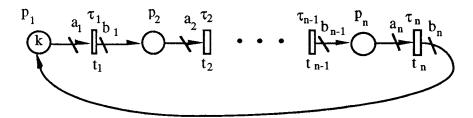

## 4.2.3 Nets with multiple-weighted arcs

First of all, the net should be bounded, live and reversible. Here is a model of a circuit with multiple-weighted arcs, as shown in Fig. 4.3.

where  $a_i$  stands for the weight of input arc  $I(p_i, t_i)$  and  $b_i$ , output arc  $O(p_{i+1}, t_i)$   $(1 \le j \le n)$ .

Fig. 4.3 A circuit with multiple-weighted arcs

There exist two conclusions:

1.

$$\Pi a_j = \Pi b_j \quad (j=1,2,..., n) \quad [4]$$

2.  $m_0(p_1) \ge \max(\prod_{j=1}^k \frac{a_j}{b_{j-1}}, k=1, 2, ..., n)$

where  $b_0=1$ .

The first point guarantees that tokens in net are bounded during processing. The second is a necessary condition for the live net, but not sufficient. For instance, n=4 with  $a_1=3$ ;  $b_1=2$ ;  $a_2=5$ ;  $b_2=3$ ;  $a_3=2$ ;  $b_3=5$ ;  $a_4=4$  and  $b_4=4$ , the value from the equation in the second condition is 7.5, actually the minimum tokens in  $p_1$  without deadlock is 13. Only if the factor of  $a_j^i/b_{j-1}^i$  or  $b_{j-1}^i/a_j^i$  is a positive integer for applicable 1 and j in the net and all of its reduced nets, Condition is necessary and sufficient for the liveness of the net. An example follows.

Fig. 4.4 introduces a reduced circuit of a multiple-weighted one with n=4. In the original circuit, there are 4 pairs of  $a_i$  and  $a_{i-1}$ , i.e.,  $a_2$  and  $b_1$ ;  $a_3$  and  $b_2$ ;  $a_4$  and  $b_3$ ; and,  $a_1$

and b4. Reduction can be done in any subnets of the original circuit, and here, a unit transition subnet is reduced in the example of Fig. 4.4. First, mark all nodes in the original circuit with the superscript of "0" which means 0-step reduction, and after reduction, mark the reduced circuit with 1 which means 1-step reduction. In this example,  $a_2^1 = \max(a_2^0, a_2^0 a_3^0 / b_2^0)$  and  $b_2^1 = \max(b_3^0, b_2^0 b_3^0 / a_3^0)$ . The i<sup>th</sup> reduction can be done only under the condition that the factor of  $\frac{a_i}{b_{j-1}}$  or  $\frac{b_{j-1}}{a_j}$  in (i-1)<sup>th</sup> circuit is an integer. Otherwise, the reduction cannot be done, which means there may be remaining tokens in the reducing subnet, then the equation in Condition 2 in page 36 is not sufficient for this case. We can see the original circuit can be reduced to a single-place-single-transition circuit with weights of input and output arcs equal to that in Condition 2 if in any step of reduction satisfies that the factor of  $a_1^i/b_{1-1}^i$  or  $b_{1-1}^i/a_2^i$  in i<sup>th</sup> reduced circuit is an integer for all applicable i and j.

Fig. 4.4 A multiple-weighted circuit with n=4 and one of its reduced circuit

In most manufacturing processes, this limitation can be met. The following calculations are limited under this condition - there is no remaining token in places except p<sub>1</sub> in a firing loop.

Now, mark the transition  $t_i$  in Fig. 4.3 with time delay  $\tau_i$  ( $1 \le i \le n$ ), respectively, and denote m= max( $\prod_{i=1}^{a_i} \frac{a_i}{b_{j-1}}$ , k=1, 2, ..., n).

The minimum number of active tokens in a circuit is an integer which comes from the factor  $\frac{m_0(p_1)}{m}$ , denoted as m'. Then, the cycle time is

$$\pi_{C}$$

= (total delay in the circuit/minimum active tokens)

$$= \frac{\sum \tau_{i}}{m'}$$

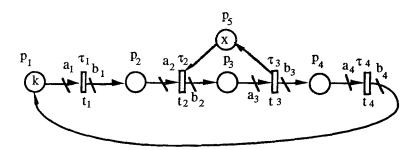

Fig. 4.5 is a model of multiple-weighted maked graph (WMG) with two circuits p<sub>1</sub>t<sub>1</sub>···t<sub>4</sub>p<sub>1</sub> and p<sub>5</sub>t<sub>2</sub>p<sub>3</sub>t<sub>3</sub>p<sub>6</sub>. That the net is bounded, live and reversible is prerequestive to the calculation. These two circuits should satisfied these three conditions:

- 1.  $\Pi a_j = \Pi b_j \ (j=1, 2, 3, 4)$

- 2.  $m_0(p_1) \ge \max(\prod_{j=1}^{a_j} \frac{a_{j}}{b_{j-1}}, k=1, 2, 3, 4)$ 3. Either  $\frac{a_j}{b_{j-1}}$  or  $\frac{b_{j-1}}{a_j}$  is a positive integer.

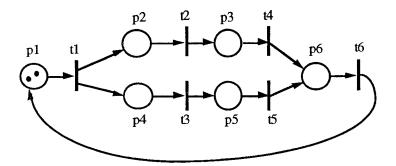

Fig. 4.5 A model of multiple-weighted marked graph

Now it is clear that b<sub>2</sub>=a<sub>3</sub> due to the loop p<sub>5</sub>t<sub>2</sub>p<sub>3</sub>t<sub>3</sub>p<sub>6</sub> and the net can be reduced to that in Fig. 4.6. m=max(a<sub>1</sub>,  $\frac{a_1a_2}{b_1}$ ,  $\frac{a_1a_2a_4}{b_1b_3}$ ) and m' is the integer part of the factor  $\frac{k}{m}$ .

Fig. 4.6 One-step reduction of a WMG model

If m=1, it means that  $a_1=1$ ,  $b_1\geq a_1a_2=a_2$  and  $b_1=Ba_1$  ( $\beta$  is a natural number) due to the conditions and formula listed above. Then if  $x\geq \beta$ ,  $\pi_c=\max(\frac{\tau_1+\tau_2+\tau_3+\tau_4}{m'},\frac{\tau_2+\tau_3}{x})$ . Otherwise,  $x<\beta$ ,  $\pi_c=\max(\frac{\tau_1+\tau_4+\frac{(\tau_2+\tau_3)\beta}{x}}{m'},\frac{(\tau_2+\tau_3)\beta}{x})$ .

If  $m \ge 2$ , then it is more difficult. From the formula associated to m, we can find that either  $a_1$ ,  $\frac{a_1a_2}{b_1}$  or  $\frac{a_1a_2a_4}{b_1b_3}$  is equal to m.

First,  $a_1=m$ . In this case,  $b_1\geq \frac{a_1a_2}{m}=a_2$  and we get  $b_1=\beta a_2$  ( $\beta$  is a natural number). If  $x\geq \beta$ ,  $\pi_c=\max(\frac{\tau_1+\tau_2+\tau_3+\tau_4}{m'},\frac{\tau_2+\tau_3}{x})$ . Otherwise,  $\pi_c=\max(\frac{\tau_1+\tau_4+\frac{(\tau_2+\tau_3)\beta}{x}}{m'},\frac{(\tau_2+\tau_3)\beta}{x})$ .

If  $a_1 < m$  and  $\frac{a_1 a_2}{b_1} = m$ , it means that  $\frac{a_2}{b_1} = \frac{m}{a_1} > 1$ . we get that  $a_2 = \beta b_1$  where  $\beta$  is a natural number and  $\beta \ge 2$ . Then the cycle time  $\pi_c = \max(\frac{\tau_1 + \tau_2 + \tau_3 + \tau_4}{m'}, \frac{\tau_2 + \tau_3}{x})$ .

The last case is that  $a_1 < m$ ,  $\frac{a_1 a_2}{b_1} < m$  and  $\frac{a_1 a_2 a_4}{b_1 b_3} = m$ . Similarly, we get  $a_4 = \beta b_3$ , i.e., the number of firing  $t_{23}$  is n times as much as that of  $t_4$ . We also get: if  $x \ge \beta$ , then the cycle time  $\pi_c = \max(\frac{\tau_1 + \tau_2 + \tau_3 + \tau_4}{m'}, \frac{\tau_2 + \tau_3}{x})$  and if  $x < \beta$ ,  $\pi_c = \max(\frac{\tau_1 + \tau_4 + \frac{(\tau_2 + \tau_3)\beta}{x}}{m'}, \frac{(\tau_2 + \tau_3)\beta}{x})$ .

#### 4.3 Reduction of Timed Petri Nets

The purpose of reduction is to simplify the nets while preserving interesting properties and thus, save the time of computation and analysis.

### 4.3.1 Reduction approaches in marked graphs

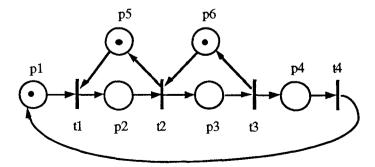

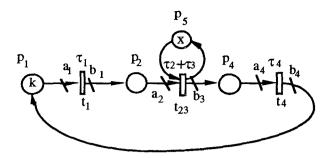

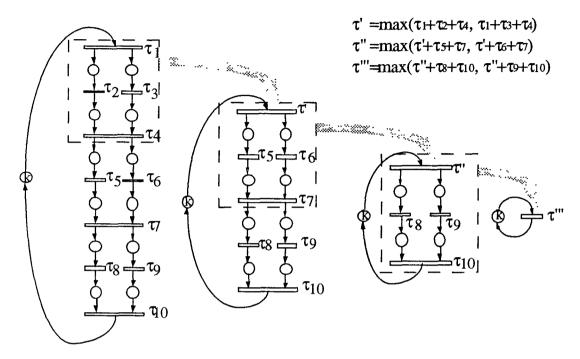

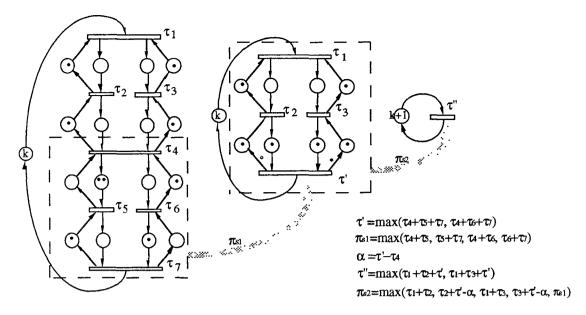

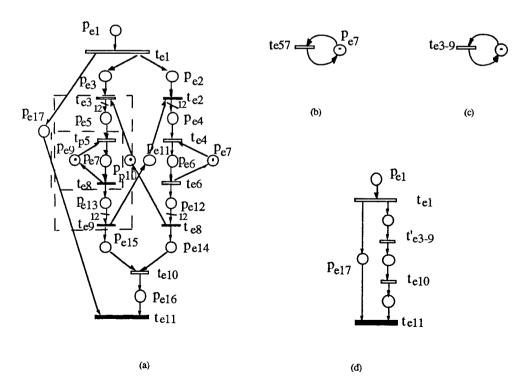

Fig. 4.7 Reduction of a net with concurrent paths

To illustrate the significance of reduction of marked graphs, sequential combination of three subnets of Fig. 4.7 is evaluated using reduction as shown in Fig. 4.8. The reduction is separated into three steps. First, the upper concurrent subnet is reduced to a macro transition subnet, whose delay time is  $\max(\tau_1+\tau_2+\tau_4, \tau_1+\tau_3+\tau_4)$ , according to the formula above. The following steps are in the same way. The reduction processes are illustrated in Fig. 4.8. In this case, the number of computation is decreased from  $2^3$  to  $2^4$ 3. As a conclusion, in a concurrent sequence, the reduction methodology saves the number of computation from  $\Pi n_i$  to  $\Sigma n_i$ , where  $n_i$  represents the number of concurrent paths in ith order.

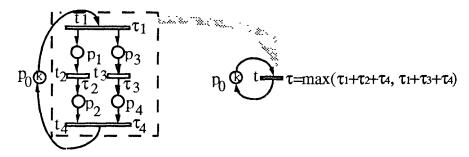

Another example shown in Fig. 4.9 is used to show the reduction of a subnet containing tokens. In this case, we need to keep the record of the maximum cycle time of the loops in the subnet, denoted by  $\pi_3$ , as the cycle time is the maximum value of total local

circuits, it saves the calculation space and time to keep the maximum cycle time instead of the whole loops in the subnet.

$\pi_s(i) = \max(\text{total local cycle time of the i}^{\text{th}} \text{ subnet}, \pi_s(i-1))$

Fig. 4.8 Three-step reduction of subnets with concurrent paths

Fig. 4.9 Reduction of a net with loops in subnets

In addition, we need to amend the equivalent net. Subnet reduction affects the circuits involving the incoming and/or outgoing arcs, as it changes the time delay information on the *macro node*, which represents the reduced subnet. The transitions t' and t" in the example are marco transitions. An *incoming arc* is an arc which goes to the output node in the subnet, and an *outgoing arc* comes from the input node in the subnet. In the example, arcs (p<sub>7</sub>, t<sub>4</sub>) and (p<sub>8</sub>, t<sub>4</sub>) are the outgoing arcs of the subnet t<sub>4</sub>-t<sub>7</sub>, and there are no incoming arcs. After reduction, they both move to the macro node t'. Now these arcs are marked with *artificial delay*  $\alpha$ , and  $\alpha$ = $\tau_{new}$ - $\tau_{old}$ , where  $\tau_{new}$  is the delay time of the macro node,  $\tau_{old}$  is that of the input or output transition. Here, the incoming arcs have the same artificial delay as each other, so do the outgoing arcs. Then, the cycle time of a circuit is

$$\pi = \frac{\sum \tau_i - \alpha_i}{\sum m_i}$$

where  $\alpha_i$  is the sum of all artifitial delays assotiated with ith circuit.

The last example in Fig. 4.10 is used to illustrate the case that elementary paths contain tokens. An *elementary path* is a path from the input node to the output node in a subnet. In this case, we need to consider the token flow. Each of concurrent paths in a subnet may contain a number of tokens. Their minimum number should be added to all of the input places to the macro transition of the subnet, where it satisfies  $\{p: p \in {}^{\bullet}t_{macro}\}$ . The other conditions remain as the preceding cases. Hence, the cycle time of i<sup>th</sup> circuit is

$$\pi = \frac{\sum \tau_i - \alpha_i}{\sum m_i - \mu_i}$$

where  $\mu_i$  represents the sum of artificial tokens in the  $i^{\text{th}}$  loop.

Fig. 4.10 Reduction of subnets with tokens in elementary paths

# 4.3.2 Reduction example for an FMS cell

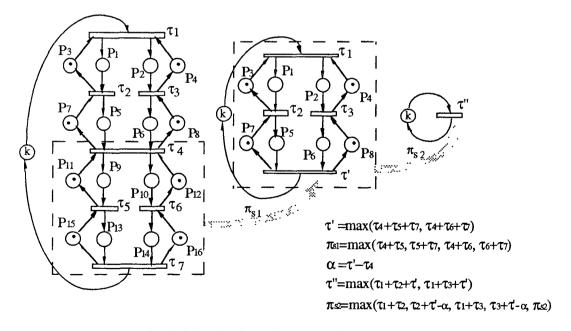

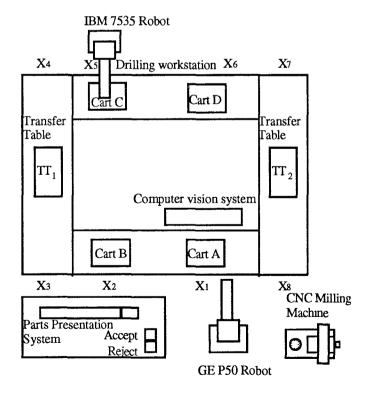

The reduction method is applied to the model of an FMS cell which is operating in the factory floor of Information Technology Center, New Jersey Institute of Technology.

Fig. 4.11 Flexible manufacturing system cell [42]

It is observed that all four carts will move from their original positions and then back to the same one during a complete cycle. Hence the conveyor system is repetitive. Since every cart can move towards only one direction and transfer tables carry a cart from one to the other and go back once it is done, the system is decision-free. The basic operations with carts and transfer tables are moving and waiting. Positions are important and can be modeled as single resources since every position cannot be occupied by two carts at any time. Four carts will be modeled then as four tokens since they are moving from a position to another [42].

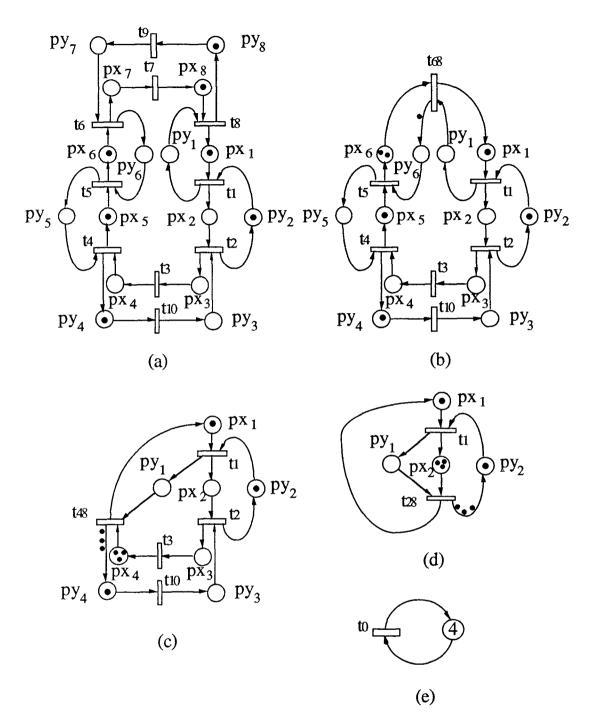

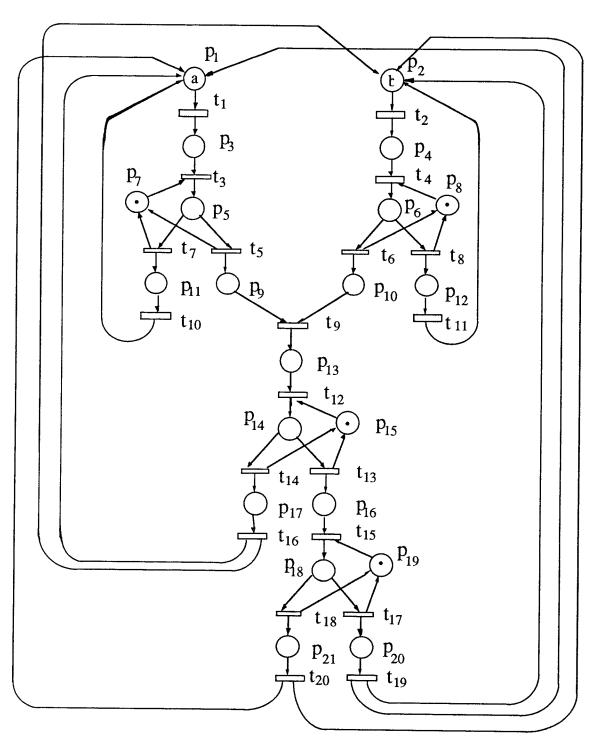

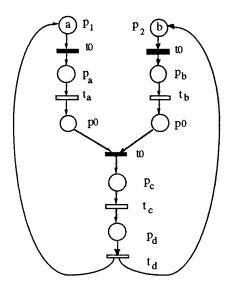

Based on the above analysis, a model of Petri net can be set up, as each moving between two positions as a transition, and each waiting as a place. Picture transitions  $t_1$ - $t_{10}$  and places  $px_1$ - $px_8$ . Then the availability of the position  $x_1$ - $x_8$  is modeled as places  $py_1$ - $py_8$ . Arcs represent the operation flows and the work-situations, referred to Fig. 4.12(a) and Table 4.1 [42].

Table 4.1 Description and time table for FMS cell [42]

| Node            | Description                                                      |    | Node            | Description                                                      | $	au_{ m i}$ |

|-----------------|------------------------------------------------------------------|----|-----------------|------------------------------------------------------------------|--------------|

| px <sub>1</sub> | Cart available at loading station at X <sub>1</sub>              | 74 | ру1             | Availability of cart halting at $X_1$                            | 0            |

| px <sub>2</sub> | Cart halting position at X <sub>2</sub>                          | 5  | ру2             | Availability of cart halting at X <sub>2</sub>                   | 0            |

| px3             | Cart loaded on TT <sub>1</sub> at X <sub>3</sub>                 | 2  | ру3             | Availability of $TT_1$ at $X_3$                                  | 0            |

| px <sub>4</sub> | Cart transported to X <sub>4</sub> by TT <sub>1</sub>            | 3  | ру4             | Availability of $TT_1$ at $X_4$                                  | 0            |

| px5             | Cart available at drilling-station at X <sub>5</sub>             | 73 | ру5             | Availability of cart halting at X <sub>5</sub>                   | 0            |

| px <sub>6</sub> | Cart halting position at X <sub>6</sub>                          | 75 | ру6             | Availability of cart halting at $X_6$                            | 0            |

| px7             | Cart loaded on TT <sub>2</sub> at X <sub>7</sub>                 | 2  | ру7             | Availability of $TT_2$ at $X_7$                                  | 0            |

| px <sub>8</sub> | Cart transported to X <sub>8</sub> by TT <sub>2</sub>            | 68 | ру8             | Availability of $TT_2$ at $X_8$                                  | 0            |

| $t_1$           | Cart moves from X <sub>1</sub> to X <sub>2</sub>                 | 3  | t <sub>2</sub>  | Cart loaded on TT <sub>1</sub>                                   | 3            |

| t3              | TT <sub>1</sub> & loaded cart move to X <sub>4</sub>             | 3  | <b>t</b> 4      | Cart unloads from TT <sub>1</sub> to X <sub>5</sub>              | 4            |

| t <sub>5</sub>  | Cart moves from X <sub>5</sub> to X <sub>6</sub>                 | 3  | t <sub>6</sub>  | Cart loaded on TT <sub>2</sub>                                   | 3            |

| t <sub>7</sub>  | TT <sub>1</sub> & loaded cart move to X <sub>8</sub>             | 3  | t <sub>8</sub>  | Cart unloads from TT <sub>2</sub> to X <sub>1</sub>              | 5            |

| t9              | TT <sub>2</sub> moves back from X <sub>8</sub> to X <sub>7</sub> | 3  | t <sub>10</sub> | TT <sub>1</sub> moves back from X <sub>4</sub> to X <sub>3</sub> | 3            |

Fig. 4.12 The model of material handling system and the reduction processes

The first reduction is based on the transition subnet with px7,  $t_6$ ,  $t_7$ , px8,  $t_8$ , py7,  $t_9$ , and py8. The transition  $t_6$  is the input transition and  $t_8$  the output transition. The elementary path is  $t_6$ px7 $t_7$ px8 $t_8$  and there is a loop in the subnet. This subnet can be