New Jersey Institute of Technology Digital Commons @ NJIT

#### Dissertations

**Electronic Theses and Dissertations**

Spring 5-31-1992

# Investigation of epitaxial lift-off GaAs and langmuir-blodgett films for optoelectronic device applications

Divyang M. Shah New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Shah, Divyang M., "Investigation of epitaxial lift-off GaAs and langmuir-blodgett films for optoelectronic device applications" (1992). *Dissertations*. 1164. https://digitalcommons.njit.edu/dissertations/1164

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

# U·M·I

University Microfilms International A Beil & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313:761-4700 800:521-0600

Order Number 9235736

## Investigation of epitaxial lift-off GaAs and Langmuir-Blodgett films for optoelectronic device applications

Shah, Divyang Manharlal, Ph.D.

.

New Jersey Institute of Technology, 1992

## INVESTIGATION OF EPITAXIAL LIFT-OFF GaAs AND LANGMUIR-BLODGETT FILMS FOR OPTOELECTRONIC DEVICE APPLICATIONS

BY DIVYANG M. SHAH

A Dissertation Submitted to the Faculty of the Graduate Division of the New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy Electrical and Computer Engineering Department May 1992

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## APPROVAL PAGE

#### Investigation of Epitaxial Lift-off GaAs and Langmuir-Blodgett Films For Optoelectronic Device Applications

by

Divyang M. Shah

Dr. Winston K. Chan, Thesis Advisor Member of Technical Staff Electronics Science and Technology Research Laboratory, Bellcore

Dr. N. M. Ravindra, Thesis Advisor Associate Professor of Physics, NJIT

Dr. William N. Carr, Committee Member Chairman for Microelectronics Center and Professor of Electrical and Computer Engineering, NJIT

Dr. Walter F. Kosonocky, Committee Member Chairman for Optoelectronics and Professor of Electrical and Computer Engineering, NJIT

Dr. Rey H. Cornely, Committee Member Professor of Electrical and Computer Engineering, NJIT

Dr. G. -K. Chang, Committee Member Member of Technical Staff Electronics Science and Technology Research Laboratory, Bellcore

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### Abstract

## Investigation of Epitaxial Lift-off GaAs and Langmuir-Blodgett Films for Optoelectronic Device Applications

Epitaxial lift-off (ELO), a technique of removing an epitaxially grown GaAs layer from its growth substrate by selective etching of an AlAs sacrificial layer, is described for field-effect transistor fabrication independent of the GaAs growth substrate. Metal Semiconductor Field-Effect Transistors (MESFETs) and High Electron Mobility Transistors (HEMTs) fabricated on silicon and sapphire substrates using ELO are investigated. A 0.1  $\mu$ m gate length depletion mode MESFET made on silicon exhibited a unity current gain frequency  $f_t = 34$  GHz. Excellent device isolation with subpicoampere leakage currents is obtained. A high input impedance amplifier has been implemented on silicon substrate using ELO GaAs MESFETs. The amplifier had an input RC time constant limited bandwidth of 500 MHz.

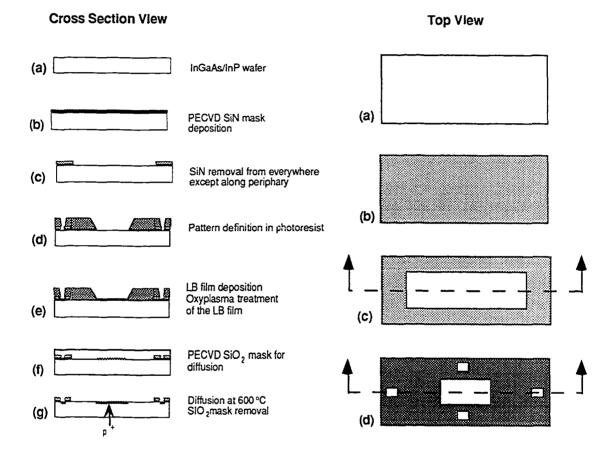

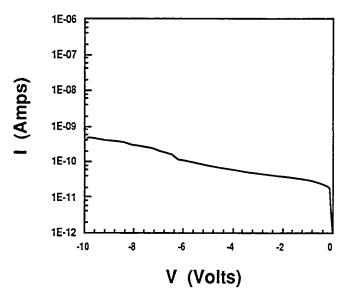

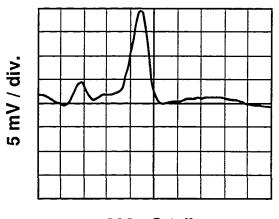

Results of investigation of a novel source of cadmium and zinc diffusion for shallow p<sup>+</sup>-n junction fabrication in In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP are also presented. Langmuir-Blodgett (LB) deposited monolayers of Cadmium and Zinc arachidate have been used as a source of Cd and Zn dopants in InGaAs/InP. This new source provides precise control of the dopant dose through the number of LB film monolayers deposited and it is also a safer method of handling toxic Cd. The LB film can be patterned by lift-off for a patterned diffusion without a mask. Highly doped (N<sub>a</sub>= 2 -4 x 10<sup>19</sup> cm<sup>-3</sup>), shallow (0.1-0.4 µm) p<sup>+</sup>-n junctions have been obtained. Junction field-effect transistors(JFETs) and PIN photodetector had a 100 pA dark current at -5 V DC bias and a bandwidth of 2 GHz.

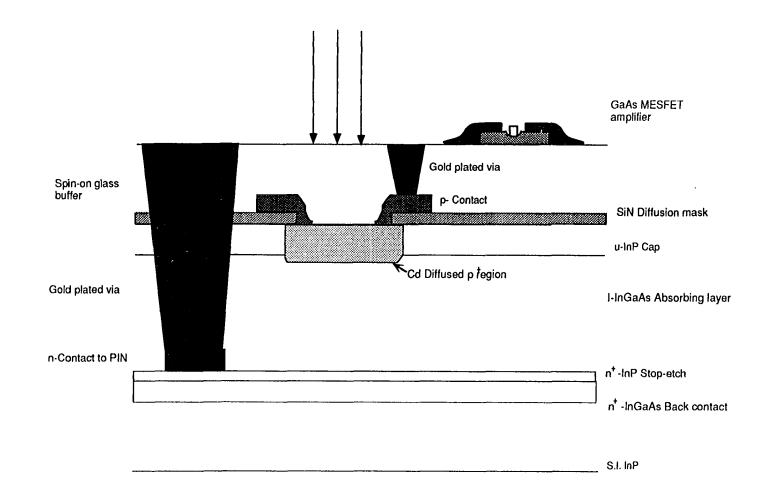

A new technique for fabricating optoelectronic integrated circuit (OEIC) photoreceivers for 1.3-1.55  $\mu$ m wavelength optical communication has also been proposed. The proposed OEIC uses ELO GaAs MESFETs and InGaAs/InP PIN photodetectors.

#### **BIOGRAPHICAL SKETCH**

Author: Divyang M. Shah Degree: Doctor of Philosophy in Electrical Engineering

Undergraduate and Graduate Education:

Doctor of Philosophy in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 1991

Master of Science in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 1988

Bachelor of Engineering in Instrumentation and Control Engineering L. D. College of Engineering, Gujarat University, Ahmedabad, India, 1984

Major: Electrical Engineering

Presentations and Publications:

1. 'Shallow junction fabrication in InGaAs using Langmuir-Blodgett film diffusion source', D. M. Shah, W. K. Chan, H. M. Cox, R. Bhat, N. E. Schlotter and C. C. Chang, Electronic Materials Conference, June '89, MIT, Cambridge, MA.

'GaAs MESFET and HEMT fabrication on silicon substrate using epitaxial lift-off as an alternative to heteroepitaxy', D. M. Shah, W. K. Chan, C. Caneau, T. Gmitter, and L. Florez, Seventh annual Sarnoff Symposium of the IEEE Princeton section, March 22, 1991.

3. 'InGaAs Shallow junction fabrication using Langmuir-Blodgett film diffusion source', D. M. Shah, W. K. Chan, H. M. Cox, R. Bhat, N. E. Schlotter, and C. C. Chang, Applied Physics Letters, Vol. 56, pp. 2132-2134, 1990.

iii

4 'GaAs MESFETs on Silicon Using Epitaxial Lift-Off', W. K. Chan,

D. M. Shah, T. Gmitter, L. T. Florez, B. P. Van der Gaag, and

J. P. Harbison, proceedings of the SOTAPOCS XII, 177<sup>th</sup> Electrochemical society meeting, May '90.

5. 'DC and RF performance of a GaAs MESFET on silicon substrate',

D. M. Shah, W. K. Chan, T. Gmitter, L. Florez, H. Schumacher, and

B. P. Van der Gaag, IEE Electronics Letters, Vol. 24, pp. 1865-66, 1990.

6. 'Epitaxial lift-off GaAs for electronics', D.M. Shah, W. K. Chan, C. Caneau, T. Gmitter, and W.-P. Hong. To be submitted for publication.

This thesis dedicated

To

My Parents and Grandparents

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### ACKNOWLEDGEMENT

I have done all of my doctoral dissertation research at the Navesink Engineering and Research Center of Bellcore, located in Red Bank, NJ. I would like to thank Dr. Bob Leheny, Dr. Eli Kapon, and Dr. Harold Craighead (now at Cornell University) for providing me with the opportunity to work at Bellcore.

I would like to thank Dr. Winston Chan for introducing me to the exciting world of III-V semiconductors and optoelectronics. I would not have been able to complete this work without his guidance and support. I also wish to thank Prof. Ravindra for his continuous help with the logistics of my project.

The work on Langmuir-Blodgett (LB) films and epitaxial lift-off (ELO) GaAs FETs would not have been possible without the technical help from many of the researchers from Bellcore, I gratefully acknowledge the help I received from Dr. Catherine Caneau, Dr. Raj Bhat, Dr. Herb Cox, Dr. Jim Harbison and Leigh Florez in crystal growth. For providing expert help on various aspects of the LB films, thanks go to Dr. Nick Schlotter. Thanks to Dr. C. C. Chang and Dr. Steve Schwarz for their help in the characterization of the LB films. Thanks also go to Dr. Brian Hong and Dr. Hermann Schumacher (now at University of Ulm, Germany) for high frequency measurements on FETs and to Dr. G.-K. Chang for high frequency measurements on PIN photodetectors and for his many useful suggestions throughout this work. Without the expertise of Tom Gmitter and Dr. Eli Yablanovitch on ELO GaAs, this work would not have been possible. Frank DeRosa and Dr. Mark Leadbeater made transport measurements on ELO AlGaAs/GaAs. Aid in the development of a thick interlayer dielectric was given by Dr. Steve Dzioba (Bell Northern Research, Ottawa, Canada), T. S. Ravi and Dr. Brian Bagley. The demonstration of submicron gate ELO GaAs MESFETs was made possible by Bart Van der Gaag's expert E-beam writing.

I would also like to thank Ray Martin, Larry Schiavone, Harry Gilchrist, Dr. Axel Scherer, Dr. Teresa Cheeks, Dr. Tim Sands, Chi Dang and Jim Ringo for their technical contributions in various aspects of this work. My experiments would not have been completed on time without Jim's efforts in keeping the Clean Room (including the equipment inside!) running almost all the time. Thanks are also due to Paul (Rick) Rickman for expert help in preparing most of the illustrations in this thesis. Many thanks to Dr. Henry Lee (now at University of California, Irvine) for the helpful discussions and suggestions during the course of this work. Furthermore, I may not have been able to complete this work without the continuous motivation from my friend (and philosopher!) Mitesh and his wife Soniya or, more recently, my roommate Bharat. Also, my fifteen month stay with the James family (in particular Mrs. Nancy James) helped me very much in keeping up my 'spirit' for research. Last but not least, I wish to thank my fiancée Kina for her patience and continuous encouragement.

| 1 Introduction1                                                       |    |  |  |  |

|-----------------------------------------------------------------------|----|--|--|--|

| 2 Epitaxial Lift-off GaAs for Electronics                             | 4  |  |  |  |

| 2.1 Introduction                                                      | 4  |  |  |  |

| 2.2 Background on GaAs FET Design Principles and Technology           | 6  |  |  |  |

| 2.2.1 Evaluation of FET Parasitic Resistances                         | 9  |  |  |  |

| 2.3 Review Of ELO Technology                                          | 11 |  |  |  |

| 2.4 Investigation of ELO GaAs FETs                                    | 12 |  |  |  |

| 2.4.1 ELO GaAs MESFETs                                                | 12 |  |  |  |

| 2.4.2 Problems Encountered While Processing ELO GaAs                  |    |  |  |  |

| MESFETs                                                               | 25 |  |  |  |

| 2.4.3 Development of Non-alloyed Ohmic Contacts                       | 30 |  |  |  |

| 2.4.4 Development of MESFETs and HEMTs Without                        |    |  |  |  |

| Recessed Gates                                                        | 34 |  |  |  |

| 2.5 Feasibility Study of ELO GaAs FETs for Small Scale Integrated     |    |  |  |  |

| Circuit                                                               | 43 |  |  |  |

| 2.5.1 Drain Current Distribution in ELO HEMTs and                     |    |  |  |  |

| On-wafer HEMTs                                                        | 43 |  |  |  |

| 2.5.2 Intrinsic Transconductance Distribution in ELO and              |    |  |  |  |

| On-wafer HEMTs                                                        | 44 |  |  |  |

| 2.5.3 Stability Assessment of ELO HEMTs                               |    |  |  |  |

| 2.6 Summary                                                           | 47 |  |  |  |

| 3 Langmuir-Blodgett Thin Films for Optoelectronic Device Applications | 50 |  |  |  |

| 3.1 Introduction                                                      | 50 |  |  |  |

| 3.2 Historical Background of LB Films                                 | 51 |  |  |  |

| 3.3 Cadmium and Zinc Diffusion from Conventional Sources              | 52 |  |  |  |

| 3.4 Cadmium and Zinc Diffusion in InGaAs/InP from LB Film             | 53 |  |  |  |

| 3.4.1 LB Film Deposition System and Technique                         | 53 |  |  |  |

| 3.4.2 Diffusion Procedure                                             | 57 |  |  |  |

| 3.4.3 Characterization of As-deposited and Oxyplasma                  |    |  |  |  |

| Treated LB Films                                                      | 58 |  |  |  |

## CONTENTS

|          | 3.4.4 Characterization of Cadmium and Zinc Diffused                                                                 |                   |

|----------|---------------------------------------------------------------------------------------------------------------------|-------------------|

| ~        | InGaAs Layers                                                                                                       | ••••              |

|          | .5 Example Applications of LB Film to Optoelectronic Device                                                         |                   |

| F        | abrication                                                                                                          |                   |

|          |                                                                                                                     |                   |

| 3        | 3.5.2 PIN Photodetectors                                                                                            |                   |

|          | •                                                                                                                   |                   |

| 4 ELV a  | nd LB Film Application to Optoelectronic Integrated Circuits                                                        | *******           |

| 4        | .1 Introduction                                                                                                     |                   |

| 4        | .2 Review of OEICs for 1.3-1.55 µm Wavelength Optical                                                               |                   |

| C        | Communication                                                                                                       |                   |

| 4        | .3 Proposed OEIC Photoreceiver                                                                                      | • • • • • • • • • |

|          | 4.3.1Photodetector Selection Criteria for OEIC                                                                      |                   |

|          | 4.3.2 OEIC Fabrication Process                                                                                      |                   |

|          | 4.3.3 High Input Impedance and Transimpedance Amplifiers                                                            |                   |

|          | in ELO GaAs                                                                                                         |                   |

| 4        | .4 Summary                                                                                                          | •••••             |

| 5 Conclu | ısions                                                                                                              |                   |

| 5        | .1 Epitaxial Lift-off For Substrate Independent GaAs FETs                                                           |                   |

| 5        | .2 LB Films for Optoelectronic Devices                                                                              | •••••             |

|          |                                                                                                                     |                   |

| Appendi  | ix Standard Processes for III-V Compound Semiconductors                                                             |                   |

|          | Ix Standard Processes for III-V Compound Semiconductors                                                             |                   |

|          |                                                                                                                     |                   |

|          | 1 Deposition Of Dielectrics and Contact Metallizations                                                              |                   |

| А        | 1 Deposition Of Dielectrics and Contact Metallizations<br>A1.1 Dielectric Deposition                                |                   |

| А        | Al Deposition Of Dielectrics and Contact Metallizations<br>A1.1 Dielectric Deposition<br>A1.2 Contact Metallization |                   |

## LIST OF FIGURES

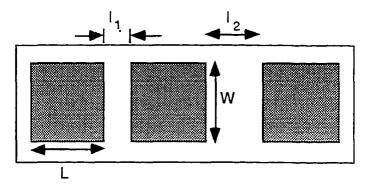

| 2.1  | (a) A transmission line pattern for ohmic contact resistance evaluation9          |

|------|-----------------------------------------------------------------------------------|

| 2.1  | (b) Contact resistance evaluation by transmission line technique10                |

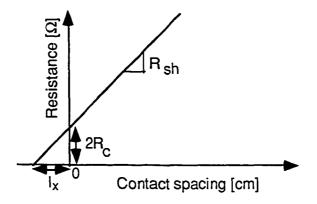

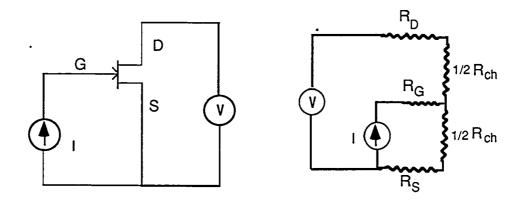

| 2.2  | (a) A schematic and equivalent circuit of a measurement setup for                 |

|      | R <sub>GS</sub> extraction                                                        |

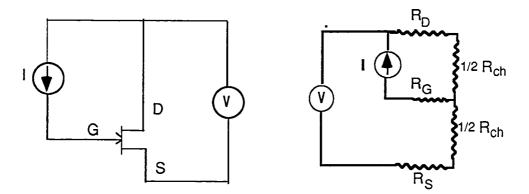

| 2.2  | (b) A schematic and equivalent circuit of a measurement setup for                 |

|      | R <sub>GD</sub> extraction                                                        |

| 2.3  | ELO process sequence                                                              |

| 2.4  | ELO GaAs FET process sequence                                                     |

| 2.5  | A photomicrogrph of a completed ELO GaAs MESFET on SiO <sub>2</sub> /Si16         |

| 2.6  | (a) DC Transfer characteristics of an on-wafer GaAs MESFET17                      |

| 2.6  | (b) RF characteristics of an on-wafer GaAs MESFET18                               |

| 2.7  | (a) Typical drain I-V characteristics and (b) DC transfer                         |

|      | characteristics of an ELO GaAs MESFET19                                           |

| 2.8  | RF characteristics of an ELO GaAs MESFET on SiO <sub>2</sub> /Si20                |

| 2.9  | (a) DC isolation and (b) Sidegating characteristics of ELO GaAs MESFET $\dots 21$ |

| 2.10 | Drain I-V characteristics of a 0.1 $\mu$ m gate length ELO GaAs                   |

|      | MESFET on 0.25 $\mu m$ thick SiN/Si $\ldots 22$                                   |

| 2.11 | RF characteristics of a 0.1 $\mu m$ gate length ELO GaAs MESFET on                |

|      | 0.25 µm thick SiN/Si                                                              |

| 2.12 | Drain I-V characteristics of an enhancement mode ELO GaAs                         |

|      | MESFET on sapphire                                                                |

| 2.13 | RF characteristics of an enhancement mode ELO GaAs MESFET                         |

|      | on sapphire                                                                       |

| 2.14 | A photomicrograph of a 4 mm x 6 mm area ELO GaAs FET sample26                     |

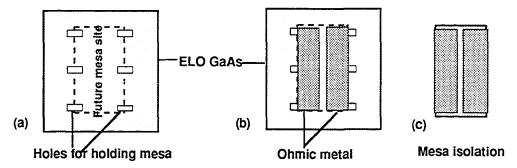

| 2.15 | Top view of altered FET process                                                   |

| 2.16 | A cross section view of the altered FET process shown in Figure 2.15        |

|------|-----------------------------------------------------------------------------|

| 2.17 | Illustration of AuGe ohmic contact alloy flow                               |

| 2.18 | New FET process with only 15-20% ohmic metal on buffer layer                |

| 2.19 | Band diagram of a non-alloyed ohmic contact scheme for n-GaAs               |

| 2.20 | (a) Epitaxial layer structure of GaAs MESFET with                           |

|      | non-alloyed ohmic contacts                                                  |

| 2.20 | (b) Contact resistance characteristics of a non-alloyed contact to n-GaAs32 |

| 2.21 | Drain I-V characteristics of an enhancement mode ELO GaAs                   |

|      | MESFET with non-alloyed ohmic contacts                                      |

| 2.22 | (a) DC transfer characteristics of an ELO GaAs MESFET with                  |

|      | non-alloyed ohmic contacts                                                  |

| 2.22 | (b) RF characteristics of an ELO GaAs MESFET with non-alloyed               |

|      | ohmic contacts                                                              |

| 2.23 | (a) DC transfer characteristics of an ELO GaAs MESFET with                  |

|      | alloyed ohmic contacts and gate without recess etch                         |

| 2.23 | (b) RF characteristics of an ELO GaAs MESFET with alloyed                   |

|      | ohmic contacts and gate without recess etch                                 |

| 2.24 | (a) Typical drain I-V characteristics of an on-wafer AlGaAs/GaAs            |

|      | HEMT with alloyed ohmic contacts and gate without recess etch               |

| 2.24 | (b) DC transfer and (c) RF characteristics of an on-wafer AlGaAs/GaAs HEMT  |

|      | with alloyed ohmic contacts and gate without recess etch                    |

| 2.25 | (a) Typical drain I-V characteristics of an ELO AlGaAs/GaAs                 |

|      | HEMT with alloyed ohmic contacts and gate without recess etch               |

| 2.25 | (b) Typical DC transfer characteristics of an ELO AlGaAs/GaAs               |

|      | HEMT with alloyed ohmic contacts and gate without recess etch               |

| 2.25 | (c) RF characteristics of an ELO AlGaAs/GaAs HEMT with                      |

|      | alloyed ohmic contacts and gate without recess etch                         |

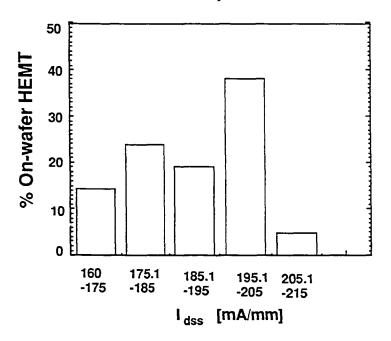

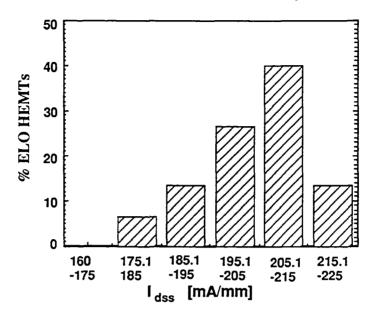

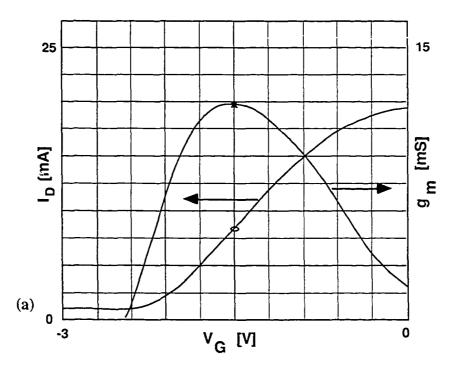

| 2.26 | (a) Saturated drain current distribution in an on-wafer HEMT sample           |

|------|-------------------------------------------------------------------------------|

| 2.26 | (b) Saturated drain current distribution in an ELO HEMT sample44              |

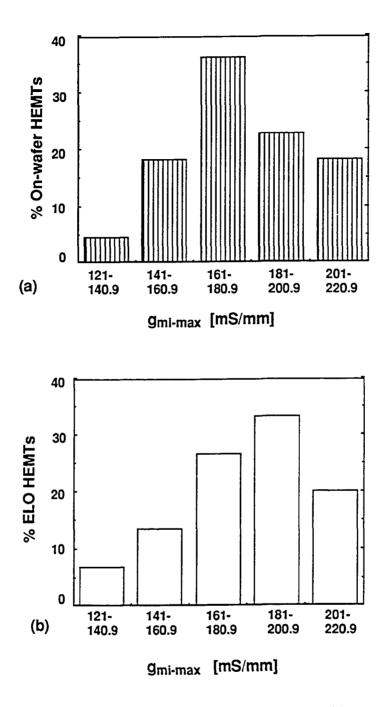

| 2.27 | Intrinsic transconductance distributions in (a) an on-wafer and (b) an        |

|      | ELO HEMT sample                                                               |

| 2.28 | (a) DC transfer characteristics of an ELO HEMT before 115 hour                |

|      | continuous operation under DC bias                                            |

| 2.28 | (b) DC transfer characteristics of an ELO HEM1 after 115 hour                 |

|      | continuous operation under DC bias                                            |

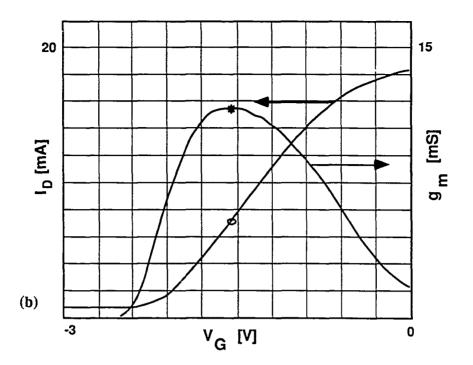

| 3.1  | Top and cross section views of an LB trough                                   |

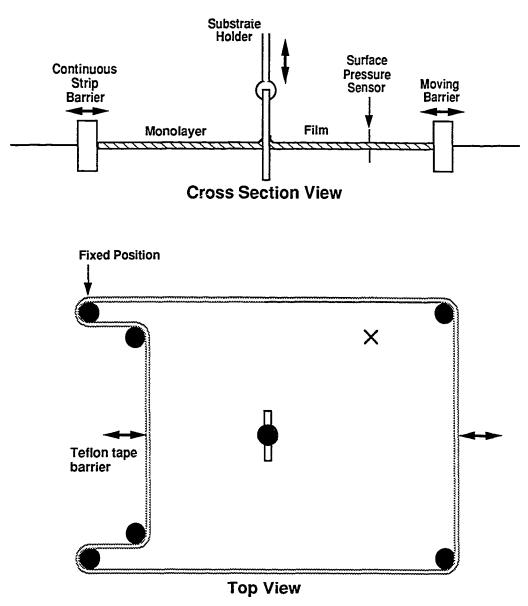

| 3.2  | (a) Arachidic acid and (b) Cadmium arachidate molecules                       |

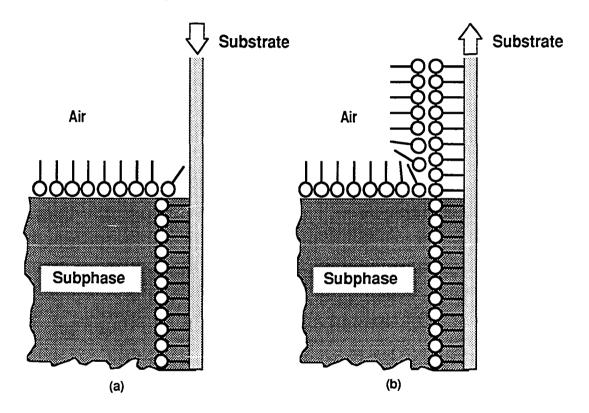

| 3.3  | LB film deposition on a hydrophilic substrate                                 |

| 3.4  | A patterned diffusion scheme without a mask using LB film diffusion source 58 |

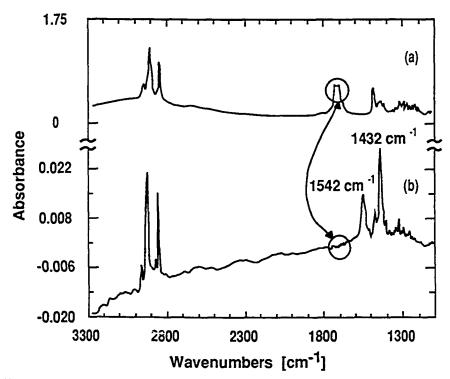

| 3.5  | GIIRs of (a) bulk arachidic acid and (b) cadmium arachidate                   |

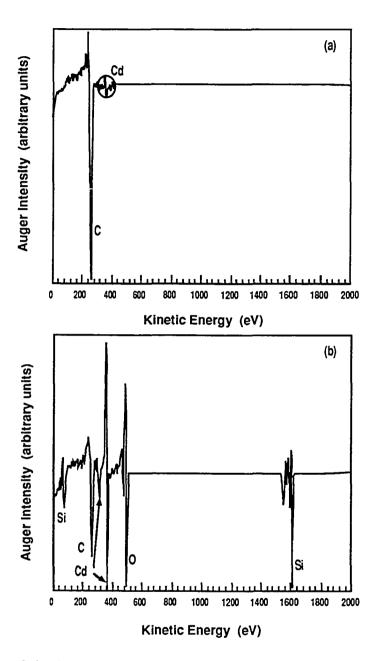

| 3.6  | Auger spectra of (a) as deposited and (b) oxyplasma processed Cd-Ar60         |

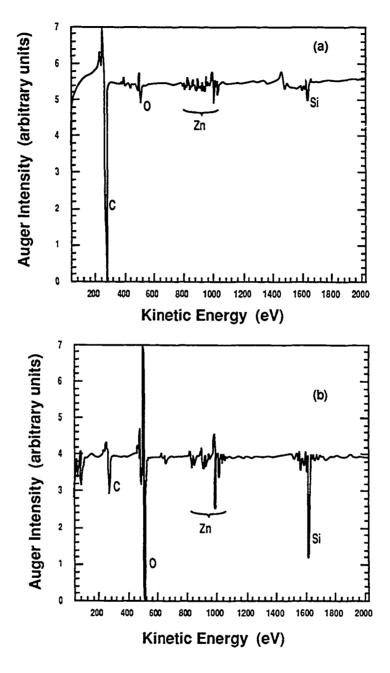

| 3.7  | Auger spectra of (a) as deposited and (b) oxyplasma processed Zn-Ar62         |

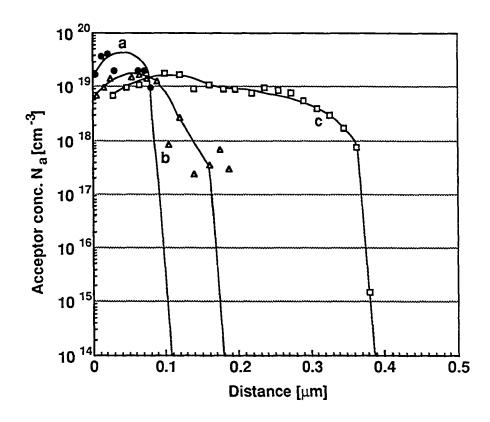

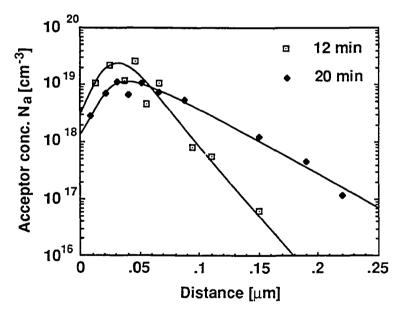

| 3.8  | Differential Hall profiles of Cd diffused InGaAs/InP63                        |

| 3.9  | Differential Hall profiles of Cd diffused InGaAs/InP showing the              |

|      | effect of dopant dose depletion                                               |

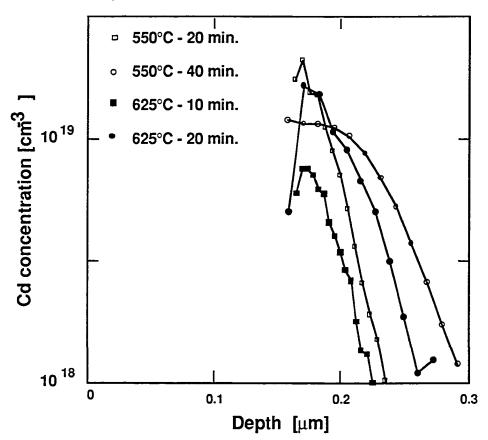

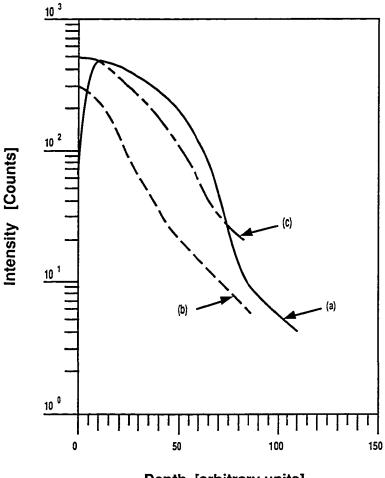

| 3.10 | SIMS profiles of Cd diffused InGaAs/InP65                                     |

| 3.11 | SIMS profiles of Zn diffused InGaAs/InP66                                     |

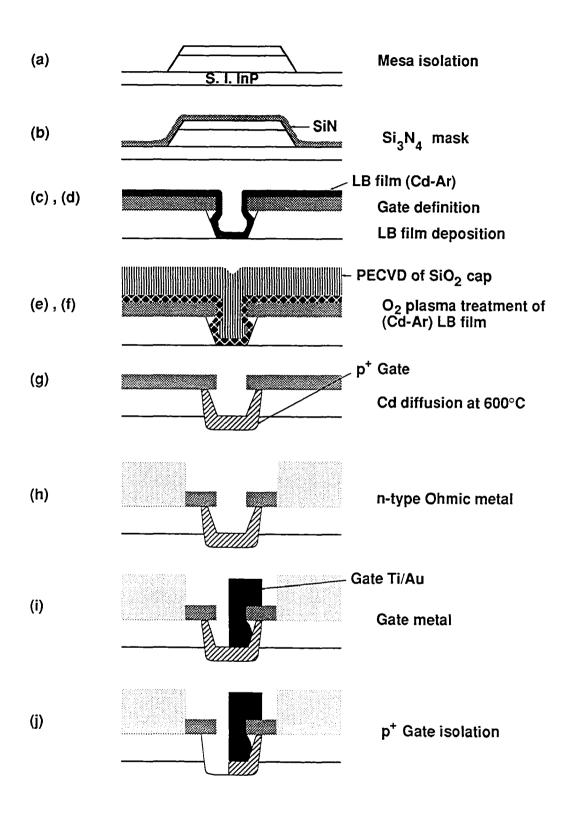

| 3.12 | JFET fabrication sequence                                                     |

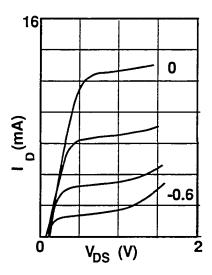

| 3.13 | Drain I-V characteristics of a JFET69                                         |

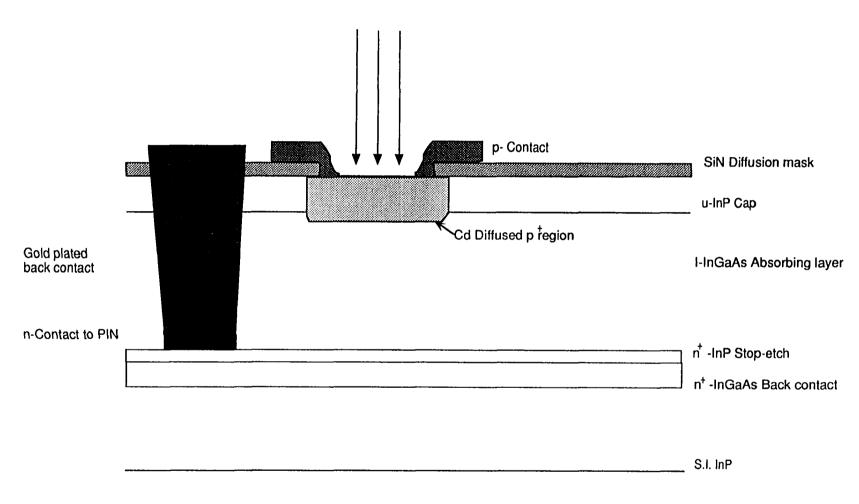

| 3.14 | Cross section view of a completed PIN photodetector72                         |

| 3.15 | PIN photodetector characteristics in dark73                                   |

| 3.16 | Pulse response of a PIN photodetector74                                       |

| 4.1  | Cross section view of an OEIC                                                 |

| 4.2  | A photomicrograph of a completed OEIC                                         |

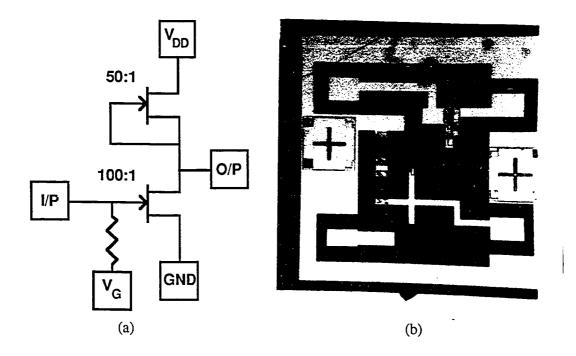

| 4.3 | A photomicrograph of an ELO GaAs transimpedance amplifier    |

|-----|--------------------------------------------------------------|

| 4.4 | An ELO GaAs high input impedance amplifier (a) schematic and |

|     | (b) photomicrograph                                          |

## LIST OF TABLES

| 2.1 | Summary | of electron | transport | measurements | on E | ELO . | AlGaAs/GaA | s 38 |

|-----|---------|-------------|-----------|--------------|------|-------|------------|------|

| 2.2 | Summary | of ELO FET  | experime  | ents         |      |       |            | 49   |

### CHAPTER 1

### Introduction

Results of investigation of epitaxial lift-off GaAs and Langmuir-Blodgett thin films for optoelectronic device application are presented in this thesis. All the experimental work for this dissertation was done at Navesink Engineering and Research Center of Bell Communications Research (Bellcore), located in Red Bank, NJ. The lightwave communication project described in the following chapters involved close cooperation of several members of technical staff of Electronics Science and Technology Research Laboratory of Applied Research Area.

Lightwave communication technology is important for very high bandwidth transmission. Optical signals can propagate over a silica fiber with very low loss (< 0.5 dB/km) and dispersion between 1.3 - 1.6  $\mu$ m. The signal attenuation is minimum at 1.55  $\mu$ m and the dispersion goes to zero at 1.3  $\mu$ m wavelength. While the signal transmission over the fibers is in lightwaves, the communication equipment at the transmitting and the receiving ends is still electronic, capable of processing only electrical signals. The need for electrical-to-optical and optical-to-electrical conversion has resulted in the development of optoelectronic transmitters and receivers. All of the transmitters and receivers in use at present are made from hybrid integration of electronic and optical components. One has to rely on hybrid integration of components because high speed transistors are made using GaAs or Si which cannot lase or detect light at 1.3-1.55  $\mu$ m, the wavelength range coinciding with the lowest signal loss and dispersion in the silica optical fibers. The lasers and the photodetectors are made in In<sub>x</sub>Ga<sub>1-x</sub>AsyP<sub>1-y</sub>/InP which can lase in the 1.3-1.55  $\mu$ m wavelength range and also can exhibit high absorption in the same range. Energy band gap of In<sub>x</sub>Ga<sub>1-x</sub>AsyP<sub>1-y</sub>/InP can easily be engineered by changing its composition.

The bandwidths of hybrid transmitters and receivers are limited by parasitics introduced by the interconnects used for integrating electronic and light emitting/detecting components. The hybrids are also expensive because of high cost of their assembly. For present day transmitters and receivers operating at several hundred megabits per second, the use of hybrid integration of electronic and optical components is permissible. However, multigigabit per second telephone networks of the future will require the use of monolithic optoelectronic components. This is the driving force behind much current interest in optoelectronic integrated circuits (OEIC). OEIC receivers in InGaAs/InP have evolved from just one transistor and one photodetector<sup>1</sup> to small and medium scale integrated circuits over a period of one decade from its inception. There is still much room for improvement in the OEIC fabrication technology as well as in their performance because the state of the art OEICs have not achieved the bandwidths and the sensitivities predicted from theory or that obtained by hybrids. This thesis is an attempt to close the gap between the two. It involves an unconventional approach for solving the problems with OEIC photoreceivers. The idea is a simple extension of the principle behind the hybrid photoreceivers presently used but with an added advantage of monolithic integration. As discussed in the Chapter 4, the fabrication of FETs in GaAs and photodetectors in InGaAs/InP would be an important achievement. It would enable manufacturers to take advantage of the mature material and device technologies of GaAs and InGaAs/InP for transistors and photodetectors, respectively.

For the proposed OEIC, fabrication of GaAs FETs independent of GaAs growth substrate is necessary. Chapter 2 is a detailed account of the comprehensive and systematic investigation of epitaxial lift-off (ELO) GaAs Metal Semiconductor Field-Effect Transistor (MESFET) and AlGaAs/GaAs High Electron Mobility Field-Effect Transistor (HEMT) fabrication independent of GaAs substrate. It is the goal of this study to investigate feasibility of using ELO GaAs as an alternative to heteroepitaxy of GaAs on crystalline or noncrystalline substrates.

The use of ELO GaAs requires that the new host be free of surface roughness on a microscopic scale. As mentioned earlier, we are planning to use InGaAs/InP PIN photodetectors for OEIC. The conventional PIN photodetectors made by epitaxial growth are mesa type having nonplanar wafer surface at the end of fabrication cycle. It is difficult to planarize such surface, especially for bonding ELO GaAs which requires almost mirror smooth surface. PIN photodetectors can be fabricated by local impurity diffusion or ion implantation of acceptors to avoid the mesa structure and the large leakage currents from the exposed p-n junction at the mesa edge. However, both of these techniques have problems associated with them. Diffusion in a closed ampoule is popular but it cannot be used for large samples required for integrated circuit fabrication. Radiation induced damage to the semiconductor crystal lattice cannot be completely removed when ion implantation is used for introducing dopants. Unavailability of a satisfactory dopant source for making large area, highly doped p<sup>+</sup>-n junctions in InGaAs/InP was a reason for investigating Langmuir-Blodgett (LB) films. It is the purpose of LB film study to investigate feasibility of using

LB deposited cadmium arachidate and zinc arachidate monolayers as dopant sources in InGaAs/InP. This new diffusion source, described in Chapter 3, can solve all of the above problems without increasing the complexity of processing. PIN photodetectors and junction field-effect transistors (JFETs) have been fabricated using Cd diffusion from the LB film. Electrical characteristics of the photodetectors and the JFETs are also presented in Chapter 3.

The results of ELO GaAs FETs and LB film diffusion source are summarized in Chapter 5. This chapter also contains conclusions and suggestions for future work.

To avoid repetition and maintain continuity of the presentation, standard fabrication processes used during this investigation are described in the Appendix. These processes are n and p type ohmic contacts for GaAs, InGaAs and InP; Schottky contacts for n-GaAs; wet chemical etching and ion beam assisted etching of GaAs, InGaAs/InP and AlGaAs/GaAs; reactive ion etching of spin-on glass; plasma etching of silicon nitride; plasma enhanced chemical vapor deposition of silicon dioxide and nitride. These processes are simply referred at the point of use without giving details as if the reader is conversant with it. Any exceptions to the processes are mentioned explicitly.

## **CHAPTER 2**

## **Epitaxial Lift-off GaAs for Electronics**

## 2.1 Introduction

A novel technique of GaAs MESFET and HEMT fabrication that is independent of growth substrate is described in this chpter along with their DC and RF characteristics. This new technique uses epitaxial lift-off (ELO) for removing the epitaxial layer structure of GaAs MESFET or HEMT from its growth substrate. The new technique has been developed with a specific application in sight, i.e., integrability of the FETs for making an integrated circuit (IC). The requirement of integrability has forced a choice of simpler FET material structure accompanied with an unconventional fabrication process that guarantees reasonable DC and RF performance with uniformity of electrical characteristics over a large area.

This chapter is divided in six parts. Reasons for investigating ELO GaAs FET technology are given in section 2.1. Section 2.2 is an overview of GaAs FET technology from a device technologist's point of view. Previous work on ELO of GaAs is reviewed in section 2.3. Section 2.4 describes ELO GaAs MESFET and AlGaAs/GaAs HEMT development, along with their DC and RF performance characteristics. A statistical study of DC parameter distribution across an ELO and on-wafer HEMT samples appears in section 2.5. Stability assessment of ELO HEMT under continuous DC bias is presented in section 2.5.3. The ELO FET experiments are summarized in section 2.6.

The work on ELO GaAs FETs described in this chapter would not have been possible without collaborations with Dr. Catherine Caneau for Organometallic Chemical Vapor Deposition (OMCVD) growth of GaAs and AlGaAs/GaAs epitaxial layers and that with Tom J. Gmitter for epitaxial lift-off of GaAs.

Heteroepitaxial growth of GaAs on silicon<sup>2</sup> and InP<sup>3</sup> substrates has been motivated by the possibility of combining the advantages of each of these materials. However, material grown in this manner has very high dislocation densities at the GaAs/Si and GaAs/InP interfaces due to a large lattice mismatch and requires a thick (~2-3  $\mu$ m) buffer layer to obtain device quality material. Also, stress resulting from a large difference in the thermal expansion coefficients of GaAs, InP and silicon, leads to undesirable substrate bowing as the sample is cooled from the growth temperature. A new technique of fabricating GaAs

MESFETs on polished semiconductor or non-semiconductor substrates described in the following sections overcomes these problems.

Heteroepitaxy of GaAs on silicon and InP requires direct growth on high dielectric constant semiconductor buffer layer to ensure single crystal GaAs growth. Buffer layer resistivity in excess of  $10^6 \Omega$ -cm is required for good device isolation. It is difficult to obtain a very high resistivity buffer layer even in an extremely clean epitaxial growth reactor because of the presence of residues from previous growths. Degradation of high frequency performance of the GaAs FETs owing to signal loss and capacitive coupling to the conducting substrate is an unavoidable consequence of it. Epitaxial lift-off is used to graft GaAs onto a new substrate covered with a thick, low dielectric constant buffer layer to realize the full advantage of high speed GaAs devices. The ability of choosing a buffer independent of the epitaxial growth system is a key to reducing parasitics associated with conducting substrates. Since the buffer deposition can be done outside of the epitaxial growth reactor, it can be chosen from a wide variety of available insulators that is most compatible with a particular application.

During the heteroepitaxy of GaAs on silicon, prolonged high temperature processing degrades the threshold voltages of the silicon MOSFETs.<sup>4</sup> In contrast, ELO GaAs FET fabrication is a low temperature process except only one short, high temperature (420°C) ohmic contact alloying step that is well below any temperature capable of causing a threshold shift in the silicon devices. Because of the low temperature processing, thermal expansion mismatch induced stresses are also minimum.

One reason for development of GaAs MESFETs on silicon is integration of high complexity, low power CMOS integrated circuits with high speed GaAs circuits. Although we have fabricated MESFETs only on unprocessed silicon wafers, this technique is expected to work equally well with wafers containing functional silicon circuits. Another possible application of ELO GaAs on silicon is monolithic integration of light emitting devices such as GaAs LEDs and laser diodes with high complexity silicon driver circuits.<sup>5</sup> The GaAs MESFETs on sapphire (section 2.4.1.2.4) can be readily used for monolithic millimeter wave integrated circuits (MMICs) with appropriate changes in fabrication sequence. A novel use of ELO GaAs on InP, as described in the chapter on ELO applications is the integration of GaAs MESFETs with InGaAs/InP PIN photodetectors for making an optoelectronic integrated circuit (OEIC). The proposed OEIC takes advantage of the mature GaAs FET and InGaAs/InP photodetector technologies.

## 2.2 Background on GaAs FET Design Principles and Technology

GaAs FET development is driven by the promise of superior high frequency performance and radiation hardness over its counterpart in silicon, namely, metal-oxide semiconductor field-effect transistors (MOSFETs). Good device and fabrication process designs are required for realization of these advantages. A brief overview of a GaAs MESFET design is given in this section. A high electron mobility field-effect transistor (HEMT) described in the later part of this chapter can also be designed following the same general guidelines with the exceptions of relations for saturated drain current and channel pinch-off voltage. A more rigorous treatment of the subject can be found in the recent texts by Sze<sup>6</sup> and Ali, et al.<sup>7</sup> An n-Channel MESFET design is discussed here but a p-channel MESFET can also be designed following the same relations with appropriate changes in voltage polarity and charge carrier velocity.

The MESFET design starts with specification of the saturated drain current and channel pinch-off voltage. The saturated drain current is given by

$$I_{dss} = q v_s N a = 192 N a$$

(2.1)

and the channel pinch-off voltage (gate voltage where drain current goes to zero) is determined by Poisson's equation

$$\left| V_{\rm P} \right| = \frac{q N a^2}{2\varepsilon_{\rm S}} = 7 N a^2 \qquad (2.2)$$

where N is the channel doping in  $10^{16}$  cm<sup>-3</sup>, a is the channel thickness in  $\mu$ m,  $\epsilon_s$  is dielectric constant of GaAs, I<sub>dss</sub> is mA/mm, and v<sub>s</sub> is electron saturation velocity in cm/s. The channel thickness and the doping are determined by solving the equations 2.1 and 2.2 simultaneously. For FETs with short < 2  $\mu$ m gate lengths, electron transport under the gate is with saturation velocity v<sub>s</sub>. The frequency at which current gain of an FET becomes unity is defined as unity current gain frequency f<sub>t</sub>. The f<sub>t</sub> is an important figure of merit for FETs operating at high frequency because it determines the upper limit of operating digital circuits. The required gate length for a given unity current gain frequency f<sub>t</sub> is obtained from the relations:

$$f_t = \frac{1}{2\pi\tau}$$

(2.3)

and

$$\tau = \frac{L}{v_s}$$

(2.4)

where L is the gate length in cm and  $\tau$  is the electron transit time under the gate in seconds. The relation for f<sub>t</sub> can also be stated as:

$$f_t = \frac{g_m}{2\pi C_G} \approx \frac{g_m}{2\pi C_{GS}}$$

(2.5)

where  $C_G$  is the total gate capacitance in Farads, and  $g_m$  is the extrinsic transconductance of FET in siemens (S). The gate capacitance includes the gate-source capacitance  $C_{GS}$  and the gate-drain capacitance  $C_{GD}$ . The gate capacitance  $C_G$  can be approximated by the gate-source capacitance  $C_{GS}$  because under the normal biasing conditions, the  $C_{GD}$ < the  $C_{GS}$ . The extrinsic transconductance  $g_me$  (as seen at the FET terminals, often referred to as  $g_m$ ) is an important figure of merit of an FET determining its gain, is related to the intrinsic transconductance  $g_{mi}$  by

$$g_{me} = \frac{g_{mi}}{1 + R_S g_{mi}}$$

(2.6)

where  $R_S$  is the source resistance. From 2.3 and 2.5

$$g_{mi} = \frac{C_{GS}}{\tau}$$

(2.7)

Another useful relation for the intrinsic transconductance is given by

$$g_{mi} = v_s Z \quad \frac{q N \varepsilon_s}{2(V_{bi} - V_{GS})}$$

(2.8)

where Z is the gate width in cm,  $\varepsilon_s$  is the permittivity of GaAs, q is the electronic charge in coulombs, N is channel doping in cm<sup>-3</sup> and V<sub>bi</sub> is the built-in voltage of the gate-channel Schottky diode. The equation 2.8 predicts that the intrinsic transconductance is maximum near zero gate bias.

The maximum frequency at which an FET can amplify the signal power is an important figure of merit for microwave amplifiers and is given by:

$$f_{max} = \frac{f_t}{2[G_0(R_G + R_S) + 2\pi f_t C_{DG} R_G]^{0.5}}$$

(2.9)

where  $C_{GD}$  is the gate-drain capacitance in Farads and  $G_0$  is the output conductance of the FET in siemens (S). As seen in equation 2.9,  $f_{max}$  includes parasitic elements of the FET, so it may be considered as a better indicator of the high frequency capability of the FET.

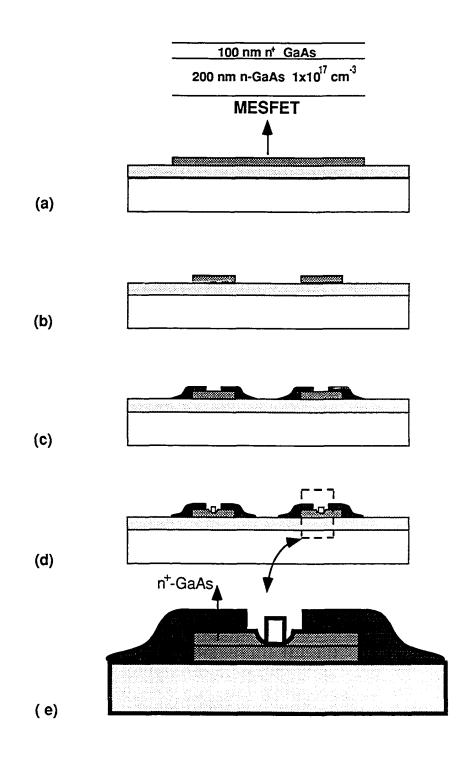

A quick look at the analytical relationships describing the high frequency figures of merits of an FET reveals that parasitic resistances and capacitances are detrimental to the high frequency performance. The  $f_t$  can be increased by increasing the transconductance which in turn can be improved by increasing channel doping. An increase in the channel doping is accompanied by an increased gate capacitance. Thus, the overall ratio of gm and CGS remains unaffected. So, the gate length must be reduced for increasing the unity current gain frequency  $f_t$ . The  $f_{max}$  can be improved by reducing the parasitics such as source and drain resistances as well as gate-source and gate-drain capacitances. The source and the drain resistances have two components: the contact resistance R<sub>c</sub> between the ohmic metal and the semiconductor, and the sheet resistance R<sub>s</sub> of the semiconductor. An ohmic contact to a heavily doped layer of GaAs on a lower doped channel layer can reduce both to give low source resistance. As shown in Figure 2.4(d), the heavily doped contact layer must be removed before putting down the Schottky gate metal. The process of removing heavily doped contact layer is termed as 'gate recess etch'. In a gate recess etch, the gate is first defined with photolithography and the highly conducting ohmic contact layer is etched using one of the etchants described in the Appendix with the source-drain current Ids as an etch depth monitor. This is the most conventional epitaxial FET fabrication technique. Other approaches include FETs with refractory gates and self aligned, ion implanted source-drain ohmic contact regions, non-alloyed ohmic contacts with recessed gates,8-9-10 and alloyed ohmic contacts without gate recess. A comprehensive review of GaAs MESFET gate fabrication technology is done by Weitzel, et al.<sup>11</sup> Each of these techniques with the exception of the self aligned gates have been tried in the course of this work.

The FETs can either be operated in enhancement mode or depletion mode. A depletion mode FET has a conducting channel present at a zero gate bias and with application of negative gate bias, the channel can be gradually pinched-off. The enhancement mode FETs have much thinner channel compared to the depletion mode FETs. The channel is completely depleted of electrons at zero gate bias because of the built-in field of the gate-channel Schottky diode and the FET is normally off. With application of small positive gate voltage, sufficient to forward bias the gate-channel Schottky diode, the FET is turned on. The enhancement mode devices are particularly useful for low power digital circuits.

#### 2.2.1 Evaluation of FET Parasitic Resistances

FET parasitic resistances include source resistance  $R_S$ , gate resistance  $R_G$  and drain resistance  $R_D$ . The gate resistance is the resistance of the gate metal. The source/drain resistance includes the contact resistance between the ohmic metal and the semiconductor layer ( $R_c$ ) as well as the sheet resistance ( $R_{sh}$ ) of the semiconductor layer.<sup>12</sup> The sheet resistance has two components:  $R_{sh1}$ , sheet resistance of the semiconductor directly under the contact, and  $R_{sh2}$ , sheet resistance of the semiconductor between the two contacts.

The total contact resistance is given by

$$R = 2 R_{c} + \frac{R_{sh2} L}{W} = \frac{2 R_{sh1} L_{t}}{W} + \frac{R_{sh2} L}{W}$$

(2.10)

where  $R_c$  is contact resistance, W is contact width, L is contact length and Lt is contact transfer length. The  $R_c$  can either be evaluated by measurements on a planar transmission line pattern<sup>13-14</sup> or a vertical Kelvin resistor.<sup>15-16-17</sup> A transmission line pattern consists of several ohmic contacts to a semiconductor bar with different spacings between them (Figure 2.1(a)).

Figure 2.1(a): A transmission line pattern for ohmic contact resistance evaluation

Resistance between two adjacent pair of contacts is measured and plotted against the contact spacing. Extrapolation of straight line to the zero contact spacing gives twice the value of  $R_C$  and the slope of the line gives the sheet resistance  $R_{sh}$  of the semiconductor (Figure 2.1(b)). The contact resistivity  $\rho_c$  is given by

Figure 2.1(b): Contact resistance evaluation by transmission line technique

$$\rho_{\rm c} = \frac{1}{2} \, R_{\rm c} \, W \, l_{\rm x} \tag{2.11}$$

where  $l_x$  is as shown in figure 2.1(b), related to contact transfer length Lt by the following relation:

$$l_{x} = \frac{2 R_{c} W}{R_{sh2}} = \frac{2 R_{sh1} L_{t}}{R_{sh2}}$$

(2.12)

The contact resistance evaluation by the TLM technique is quick when  $Lt \ll L$  but not very accurate because of the uncertainty in measurement of the small gap between the ohmic contact pads shown in Figure 2.1(a). The contact resistance thus obtained is of limited use because the TLM does not accurately represent actual conditions in an FET. The TLMs are made on highly doped layer where surface depletion effect can be neglected, whereas in an actual FET, the gate is placed in a recess (Figure 2.4(e)) on a lower doped channel. So, the effect of surface depletion is considerable and the source/drain resistance obtained from TLM can be significantly different from the actual R<sub>S</sub> and R<sub>D</sub>. The technique described in the following paragraph can be used to obtain the source and the drain resistances fairly accurately.

The setups for  $R_{GS}$  and  $R_{GD}$  measurement are shown in Figures 2.2(a) and (b), respectively, with equivalent circuits. As shown in the setups, a constant current is injected into the gate and the potential drop across drain-source terminals is measured. The gate current must be high enough to forward bias the gate-channel Schottky diode. With this technique absolute values of the source and the drain resistances cannot be obtained because  $0.5R_{ch}$  is included in the measurements.

Figure 2.2 (a): A schematic and equivalent circuit of a measurement setup for  $R_{GS}$  extraction

Extraction of the absolute source and drain resistances requires  $R_{GS}$  and  $R_{GD}$  measurements on a set of FETs with different gate lengths. Next, the measured resistances are plotted as a function of gate length and the Y-axis intercept gives true source or drain resistance.<sup>18</sup>

Figure 2.2 (b): A schematic and equivalent circuit of a measurement setup for  $R_{GD}$  extraction

#### 2.3 Review Of ELO Technology

Promise of reusing a growth substrate for low cost, thin film GaAs solar cells<sup>19</sup> was initially the reason for developing ELO technology. It was soon followed by the first ELO GaAs MESFET<sup>20</sup> operating at microwave frequency, made on a glass substrate by selective etching<sup>21</sup> of the growth substrate from epitaxial layers of MESFET. For historic purpose, it should be noted here that the concept of removing growth GaAs substrate by selective etching of a sacrificial layer of Ga<sub>1-x</sub> Al<sub>x</sub> As (x > 0.6) was first described by Stern, et al, in 1974.<sup>22</sup> The first ever published account of removing an epitaxially grown

GaAs layer by selective etching of AlGaAs and bonding it onto a glass substrate for making a photocathode appeared in 1975.<sup>23</sup> However, it took almost one and a half decade to optimize<sup>24</sup> the ELO technique. The credit for optimized lift-off also belongs to improvement in the epitaxial growth techniques enabling growth of high purity, thin, AlAs sacrificial layer. A reason for the renewed interest in the ELO is the possibility of integrating photodetectors<sup>25</sup> and lasers with glass or lithium niobate wave guides for optoelectronic integrated circuits. The most attractive feature of the ELO is its promise of grafting semiconductors on an arbitrary host without regards for compatibility of crystal structure and lattice matching. Most of the work on ELO with the exception of Chan, et al,<sup>26</sup> has been centered around preprocessing the devices and then lifting-off to a new host with minimum or no processing after lift-off.<sup>27</sup>-<sup>28</sup> Preprocessing lends itself to the use of well established GaAs processing techniques. High temperature processing also does not pose any problem unlike the postprocessing. On the other hand, postprocessing of lift-off GaAs film as described by Chan, et al., facilitates photolithographic accuracy in alignment of the grafted devices to the substrate features. It will be shown later that excellent device isolation with negligible sidegating is obtained with postprocessing of ELO GaAs MESFETs.<sup>29</sup> A similar isolation characteristics can be obtained with the preprocessed devices at the expense of considerable increase in processing.

#### 2.4 Investigation of ELO GaAs FETs

To accomplish the goals of this thesis, a comprehensive study of ELO GaAs for MESFET and HEMT fabrication independent of GaAs substrate was undertaken. This section describes this study which was aimed at developing ELO FETs with reproducible and uniform characteristics suitable for small scale integrated circuits.

## 2.4.1 ELO GaAs MESFETs

ELO MESFET fabrication was initially done following a conventional fabrication process that is used for making on-wafer FETs. As mentioned in the introduction, this standard process has been modified following systematic experimental studies to suit the requirements of integrated circuit. Three different fabrication processes accompanied by appropriate epitaxial layer structures were investigated in this thesis, namely: MESFETs with alloyed contacts and recessed gates, with non-alloyed contacts and recessed gates, and with alloyed contacts but without recessed gates. Each of them has been described in the following sections along with their DC and RF characteristics.

## 2.4.1.1 Fabrication of GaAs MESFETs With Alloyed Ohmic Contacts and Recessed Gates

As mentioned in section two, gate recess enables us to keep the parasitic source and drain resistances to a low level in the FETs with  $n^+$  GaAs layer for ohmic contacts. MESFETs with recessed gates were fabricated either on a silicon substrate covered with SiO<sub>2</sub> or SiN dielectric buffer or on polished sapphire substrate following an identical procedure. MESFETs were also fabricated on GaAs wafer following an identical fabrication process for studying effect of ELO on MESFET characteristics.

A MESFET structure consisting of a 100 nm thick n<sup>+</sup> cap, 200 nm n = 1 x 10<sup>17</sup> cm<sup>-3</sup> channel and 50 nm undoped AlAs sacrificial layer was grown on a semiinsulating GaAs substrate using MBE. On-wafer MESFETs were fabricated using an epitaxial layer structure consisting of a 100 nm n<sup>+</sup> = 2-3 x 10<sup>18</sup> cm<sup>-3</sup> ohmic contact layer, 500 nm n = 1 x  $10^{17}$  cm<sup>-3</sup> channel and 50 nm undoped AlAs sacrificial layer (if ELO was required), on a semiinsulating GaAs wafer by organo-metallic chemical vapor deposition (OMCVD).

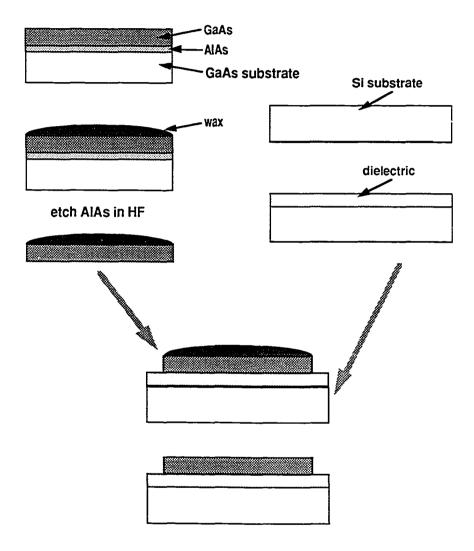

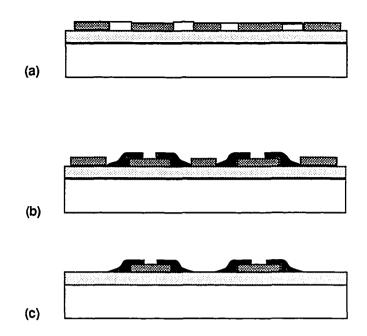

The epitaxially grown MESFET layer structure was lifted-off from the GaAs substrate by selectively etching the AlAs sacrificial layer and transferred onto a sapphire substrate or a 5  $\Omega$ -cm resistivity, p-type, <100> oriented, Si substrate, typical of those used for NMOS/CMOS circuits, that has been covered either with ~250 nm of plasma enhanced chemical vapor deposited Si<sub>3</sub>N<sub>4</sub> or with 1.5 µm of thermal oxide. The lifted-off film typically measured 0.5 cm x 1 cm and was held on the silicon substrate by Van der Waals forces. Figure 2.3 shows the ELO process sequence.

Figure 2.3 : ELO process sequence

Figure 2.5: A photomicrograph of an ELO GaAs MESFET on Si with gate length of 1  $\mu m$  and gate width of 100  $\mu m$

The MESFETs were fabricated following a standard procedure (Figure 2.4) comprising of mesa etch in a solution of  $1 \text{ H}_2\text{SO}_4$ :  $8 \text{ H}_2\text{O}_2$ :500 H<sub>2</sub>O for isolation; NiAuGe source-drain ohmic contact formation by photolithography, evaporation and lift-off; contact alloy at 420°C for 20 seconds under flowing argon; gate recess etch for I<sub>dss</sub> adjustment; and Ti/Au Schottky gate metallization. A photomicrograph of a typical ELO MESFET is shown in Figure 2.5.

## 2.4.1.2 DC and RF Characteristics of MESFETs With Alloyed Contacts and Recessed Gates

DC parameters of the MESFETs on silicon, sapphire and GaAs substrates were obtained with an HP 4145 parameter analyzer. Current gain and power gain (maximum available gain, MAG) of the MESFETs at radio frequency (RF) were obtained using a Cascade prober and HP 8510 network analyzer.

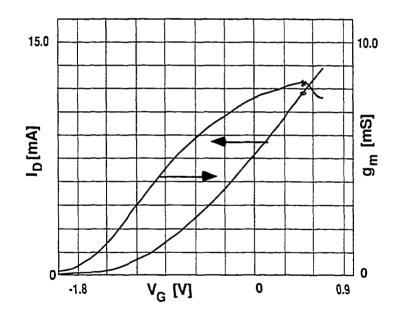

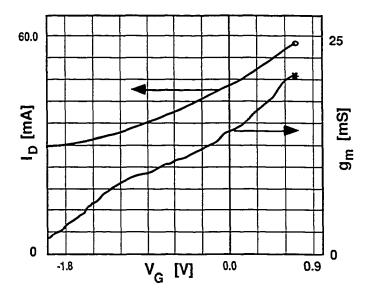

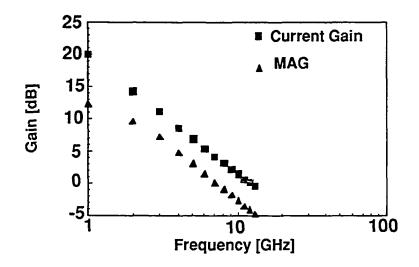

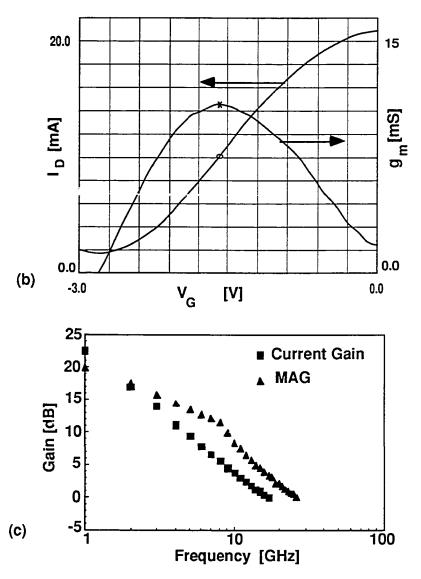

Figure 2.6(a) DC Transfer characteristics of an on-wafer GaAs MESFET with  $W_g = 100 \ \mu m$ ,  $I_{dss} = 75 \ mA/mm$ ,  $g_{m-max} = 82 \ mS/mm$ , and  $V_P = -2V$

#### 2.4.1.2.1 DC and RF Characteristics Of On-wafer MESFETs

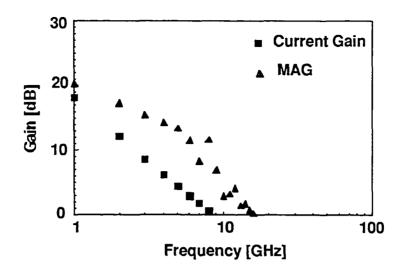

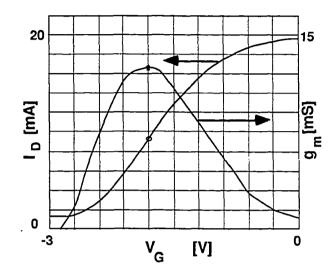

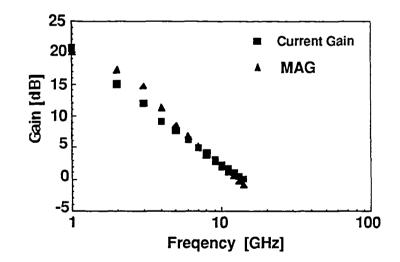

An on-wafer MESFET had a saturated drain current  $I_{dss} = 75$  mA/mm, a maximum transconductance  $g_m = 82$  mS/mm at  $V_{GS} = 0.5$  V, and a pinch-off voltage  $V_P = -2$  V (Figure 2.6(a)). The MESFET had a gate-source resistance  $R_{GS} = 3.2 \Omega$ -mm, gate-drain resistance  $R_{GD} = 4.2 \Omega$ -mm and contact resistance  $R_c = 0.75 \Omega$ -mm. Figure 2.6(b) shows an unity current gain frequency  $f_t = 13$  GHz and a maximum frequency of oscillation,  $f_{max} = 16$  GHz for a 1.1 µm gate length MESFET. These are typical for GaAs MESFETs with this gate length.

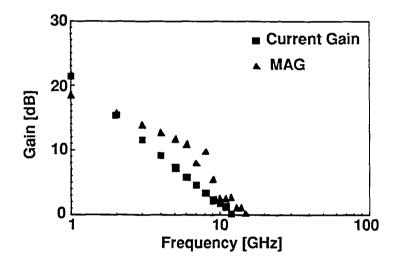

Figure 2.6(b) RF characteristics of on-wafer GaAs MESFET with gate length  $L_g = 1.1 \ \mu m$ ,  $f_t = 13 \ GHz$ ,  $f_{max} = 16 \ GHz$

## 2.4.1.2.2 ELO MESFETs on 1.5 $\mu$ m Thick Thermal Oxide

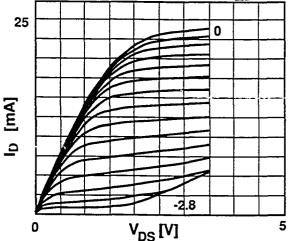

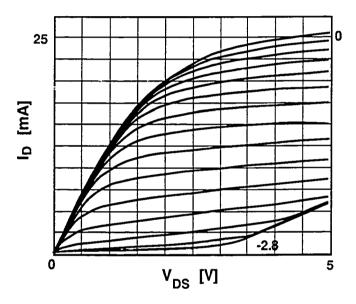

The MESFETs had a source-drain spacing of 4  $\mu$ m and a gate-source spacing of ~0.5 to 1.0  $\mu$ m with a gate length of 1.5  $\mu$ m. The contact resistance as measured from transmission line testers ranged from 0.075  $\Omega$ -mm to 0.22  $\Omega$ -mm. The MESFETs had a saturated drain current I<sub>dss</sub> of 130 mA/mm, a maximum extrinsic transconductance g<sub>m</sub> = 135 mS/mm at V<sub>GS</sub> = 0 V and a pinch-off voltage V<sub>P</sub> of -1.6 V (Figure 2.7). The avalanche breakdown of the channel occurred at V<sub>DS</sub> = 3 V, a relatively low voltage, and is attributed to a highly doped (2 x 10<sup>19</sup> cm<sup>-3</sup>) n<sup>+</sup> layer for ohmic contacts. Devices fabricated later with lower doping in the ohmic contact layer had a substantially higher channel breakdown voltage.

Figure 2.7 (a): Typical drain I-V characteristics and (b) DC transfer characteristics of an ELO MESFET with 250  $\mu$ m gatewidth on 1.5  $\mu$ m SiO<sub>2</sub>/Si with alloyed contacts and recessed gates. I<sub>dss</sub> = 130 mA/mm, g<sub>m-max</sub> = 135 mS/mm.

Figure 2.8 shows an unity current gain frequency  $f_t$  of 12 GHz and a maximum frequency of oscillation  $f_{max}$  of 14 GHz for a MESFET with a 1.3  $\mu$ m long and 100  $\mu$ m wide gate, typical frequencies for a GaAs MESFET of these dimensions fabricated on a GaAs substrate.

Figure 2.8: RF characteristics of an ELO MESFET on SiO<sub>2</sub>/Si with

$L_g = 1.3 \ \mu m. \ f_t = 12 \ GHz, \ f_{max} = 14 \ GHz.$

With the thick thermal oxide, the parasitic gate pad capacitance to the p-type silicon substrate becomes negligible and the speed is dominated by the intrinsic gate capacitance. It will be seen in the next section that the dielectric buffer layer thickness plays a dominant role in the high frequency operation of ELO FETs.

The RF output conductance was obtained by fitting the measured S-parameters to an equivalent circuit model and was ~1 mS for a 100  $\mu$ m wide device from 0.5 to 10 GHz, typical for GaAs MESFETs on GaAs substrates. In MESFETs made on the GaAs substrate, injection of hot electrons from the channel into the substrate is an important source of output conductance, but in our case, this is eliminated by the large SiO<sub>2</sub> barrier of ~7-9 eV under the channel that confines electrons in the channel under normal biasing conditions. Traps in the semiconductor or at the semiconductor/dielectric buffer, therefore, are believed to contribute to the output conductance. Further study is required to determine the exact conduction mechanism.

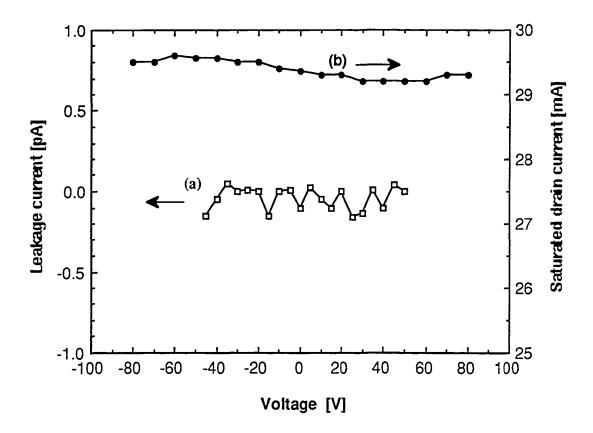

Figure 2.9: (a) Leakage current between two pads 200  $\mu$ m wide and 20  $\mu$ m apart (b) Sidegating characteristics of an ELO MESFET showing < 1% change in I<sub>dss</sub> over ±80 V on a side gate located 50  $\mu$ m away from FET

As seen in Figure 2.4, the devices are fabricated on completely isolated mesas of GaAs, which has resulted in an extremely low sidegating and excellent electrical isolation between devices because of the insulating buffer layer. Figure 2.9(a) shows subpicoampere leakage current, which was noise limited, between two pads 200  $\mu$ m wide and 20  $\mu$ m apart for an applied bias of  $\pm$  50 V. For comparison, typical leakage currents on a GaAs substrate are a nanoampere or more at substantially lower biases. For MESFETs fabricated on the semiinsulating GaAs substrates, drain current modulation or sidegating, caused by surface leakage currents resulting from traps at the substrate surface<sup>30</sup> gives rise to cross talk between neighboring devices. This is largely eliminated as well since the application of  $\pm$ 80 V to a side gate 50  $\mu$ m away from the gate of an FET produced < 1% change in I<sub>dss</sub> (Figure 2.9(b)). Dielectric breakdown of the 200 nm silicon nitride buffer at 80 V limited

the measurement to this voltage. Residual drain current modulation may be from capacitive coupling to the conducting Si substrate.

## 2.4.1.2.3 Submicron Gate ELO GaAs MESFETs on Thin Silicon Nitride

The epitaxial layer structure for the MESFETs consisted of a 100 nm thick,  $n^+$  (2 x 10<sup>18</sup> cm<sup>-3</sup>) cap and a 200 nm thick  $n = 2 \times 10^{17}$  cm<sup>-3</sup> GaAs channel. This layer structure is identical to the previous one except the doping in the cap layer. The doping level in the cap layer was reduced by an order to improve the channel breakdown voltage. MESFETs with 0.1, 0.2 and 0.4 µm gate lengths were fabricated after transferring the MESFET layers onto a silicon substrate covered with ~0.25 µm thick, plasma enhanced chemical vapor deposited silicon nitride buffer layer. Fabrication procedure was identical to that described in the previous section except the gate lithography. The submicron gates were defined by electron beam lithography and remaining process was identical to the photolithographically defined gates.

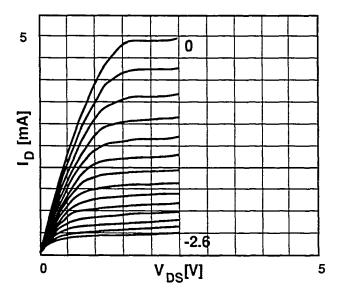

Figure 2.10: Drain I-V characteristics of a 0.1  $\mu$ m gate length ELO MESFET on 0.25  $\mu$ m thick SiN/Si with W<sub>g</sub> = 50  $\mu$ m, I<sub>dss</sub> = 98.2 mA/mm, g<sub>m-max</sub> =75 mS/mm. V<sub>G</sub>; -0.2 V/step

A MESFET with 0.1  $\mu$ m gate length and 50  $\mu$ m gate width, operated in depletion mode, had an I<sub>dss</sub> = 98.2 mA/mm, a maximum transconductance g<sub>m</sub> = 75 mS/mm at V<sub>GS</sub> = 0 V. The channel was not completely pinched off at -2.6 V (Figure 2.10). The gates tend to burn-out at higher gate biases due to excessive heating. MESFETs with 0.4  $\mu$ m gate length could be completely pinched-off. Figure 2.11 shows a unity current gain frequency  $f_t$  of 34 GHz and a maximum frequency of oscillation  $f_{max} = 23$  GHz for a 0.1 µm gate length device. The  $f_t$  has not scaled up in proportion with the ten fold scaling down of gate length because of parasitic capacitance between the gate pad and the conducting silicon substrate.

Figure 2.11 : RF characteristics of 0.1  $\mu$ m gate length ELO MESFET on 0.25  $\mu$ m SiN/Si showing f<sub>t</sub> = 34 GHz and f<sub>max</sub> = 23 GHz.

These results do not reflect true performance of a submicron gate device because the distance between the source and the drain  $(4 \ \mu m)$  electrodes was not reduced with the gate length reduction. So the extrinsic transconductance has suffered from the high parasitic source resistance. Nevertheless, this is an impressive rf performance for an ELO MESFET.

## 2.4.1.2.4 ELO GaAs MESFETs on Sapphire

Sapphire is a popular substrate for millimeter wave integrated circuits because of low signal loss in the sapphire substrate at these frequencies. Because of the large mismatch in the lattice constants of the two and differences of their crystal structures, the GaAs layers grown directly on sapphire have large number of dislocations. Single crystal GaAs FET layers can be bonded to sapphire substrate using ELO to obtain superior device performance as compared to the directly grown FETs. ELO GaAs MESFETs described in this sections were developed with the above considerations.

The epitaxial layer structure used for these devices was same as the one used for submicron gate MESFETs described in the previous section. MESFET fabrication was also done following the procedure identical to the one described earlier for the ELO MESFETs on thermal oxide.

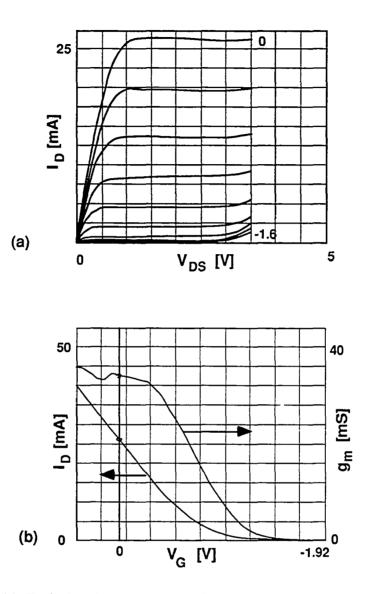

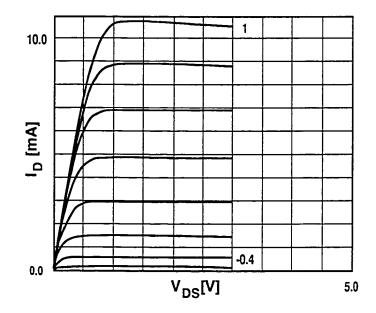

An enhancement mode MESFET with 1.3  $\mu$ m long and 100  $\mu$ m wide gate had drain current I<sub>ds</sub> = 108 mA/mm at V<sub>GS</sub> = 1 V, pinch-off voltage V<sub>p</sub> = -0.4 V and a maximum transconductance g<sub>m</sub> = 100 mS/mm at V<sub>GS</sub> = 0.6 V (Figure 2.12).

Figure 2.12: Drain I-V characteristics of an enhancement mode ELO GaAs MESFET on sapphire.  $W_g = 100 \ \mu m$ ,  $I_{ds} = 108 \ mA/mm$ ,  $g_{m-max} = 100 \ mS/mm$

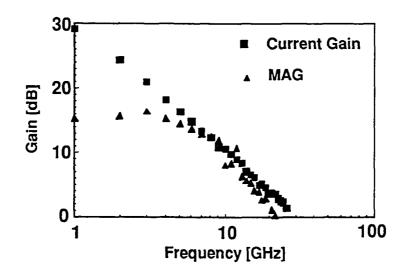

Figure 2.13 shows an unity current gain frequency  $f_t = 8.5$  GHz and a maximum frequency of oscillation  $f_{max} = 17$  GHz for a 1.1 µm gate length MESFET. The reason for lower  $f_t$  is not known. A significantly higher  $f_{max}$  value may be from lower output conductance and lower signal loss in the sapphire substrate at microwave frequencies as compared to the conducting silicon substrate.

Figure 2.13: RF characteristics of an enhancement mode ELO MESFET on sapphire  $L_g = 1.1 \mu m$ ,  $W_g = 100 \mu m$ ,  $f_1 = 8.5 \text{ GHz}$ ,  $f_{max} = 17 \text{ GHz}$

## 2.4.2 Problems Encountered While Processing ELO GaAs MESFETs

Two problems significantly limiting the yield of ELO GaAs MESFETs are blistering of the ELO GaAs during the ohmic contact annealing and adhesion of the ELO GaAs to the new host. These problems and their possible solutions are discussed in this section.

Blistering of GaAs film during high temperature ohmic contact annealing step due to vaporization of volatile impurities trapped at the substrate-film interface is a problem significantly affecting the yield of devices.<sup>31</sup> In our process, removal of most of the GaAs film in mesa etching step significantly reduces the number of sites for impurity trapping. It also confines the blistering induced damage to a considerably smaller mesa area (typical mesa dimensions are: 100  $\mu$ m x 25-40  $\mu$ m) as opposed to the whole ELO film. So, the number of devices affected by blistering are significantly lower. Figure 2.14 shows a 4 mm x 6 mm area ELO FET wafer with only local blistering.

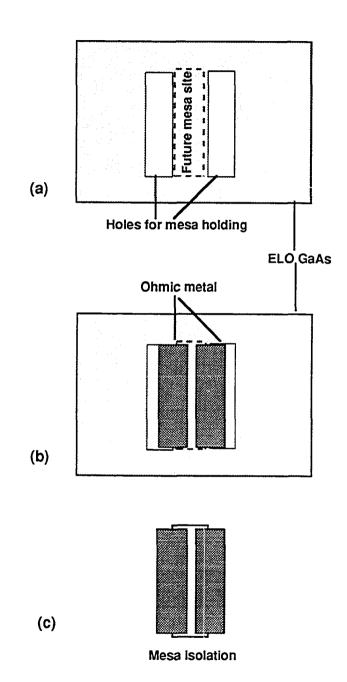

Another problem encountered while working with the ELO GaAs is the adhesion of the ELO GaAs to the new host. It was found that the Van der Waals bonding of the ELO GaAs film to the new host is not always sufficient for holding the film to the substrate through the whole processing sequence which can involve several photolithographic, etch and metallization steps. This problem was solved by altering the conventional FET fabrication sequence. The mesas were 'tacked' down to the buffer layer with ohmic metal before their isolation<sup>32</sup> (Figure 2.15). As a result, a significant improvement in the testable

Figure 2.14: A photomicrograph of a 4 mm x 6 mm area ELO FET wafer showing only local blistering

device yield was obtained. Top and cross section views of the altered process are shown in Figures 2.15 and 2.16, respectively.

Figure 2.15: Top view of altered FET process with equal amount of ohmic metal on GaAs mesa and dielectric buffer

Figure 2.16: Cross sectional view of the altered FET process shown in Figure 2.15 (a) Hole etch next to 'future mesa' site (b) Ohmic metal deposition (c) Mesa isolation

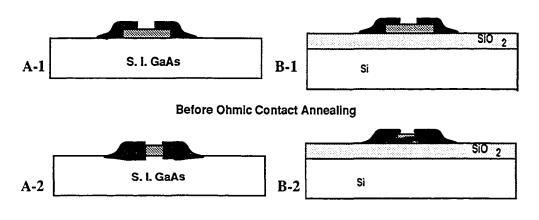

In the previous section on ELO MESFET fabrication, the conventional NiAuGe ohmic contact metal was used to obtain low contact resistance. When the same contact metallization was used for contacting extremely narrow stripes of MESFET mesas in an amplifier circuit (to be discussed in the chapter 4), it was observed that the eutectic formed by AuGe alloy at the annealing temperature (typically 420°C) reacts with the ELO GaAs film and flows laterally in the space between the source and the drain contacts, causing an electrical short (Figure 2.17(B-2)). Energy dispersive X-ray analysis (EDX) on the alloyed samples confirmed presence of gold in the channel. AuGe contact alloy is known for its large vertical as well as lateral penetration in the GaAs substrate but the lateral flow over several  $\mu$ m is unusual. It was found that the alloy flow is directly related to the ratio of the insulating buffer area under ohmic metal to the area covered on GaAs mesa. The problem was most severe when the SiO<sub>2</sub> buffer and GaAs mesa area under the ohmic metal were comparable (Figure 2.15). A new mask designed later had about 10-15% ohmic metal on buffer without causing alloy flow (Figure 2.18).

#### After Ohmic Contact Annealing

Figure 2.17: Illustration of AuGe ohmic contact alloy flow A-1, A-2: AuGe Ohmic contact to FET on GaAs wafer, B-1, B-2: AuGe Ohmic contact to ELO FET on SiO<sub>2</sub>/Si

Alloy flow problem is unique to the ELO films grafted to the substrates covered with dense dielectrics. On annealing, the contact alloy first penetrates vertically into the film (as it would have in on-wafer contacts of Figure 2.17(A-2)) and when it reaches the virtually impervious dielectric buffer, it flows laterally and shorts the drain and the source contacts. Non-alloyed ohmic contacts described in the next section were developed to eliminate ELO GaAs blistering as well as alloy flow during annealing. Another problem with ELO GaAs processing is nonuniform wet chemical etching which is described in section 2.4.4.

Figure 2.18: New FET process with only 15-20% ohmic metal on dielectric buffer

#### 2.4.3 Development of Non-alloyed Ohmic Contacts

Two different contacting schemes were considered to address the need for a non-alloyed, shallow ohmic contact. The first one involved use of Pd/Ge solid phase reaction contacts.<sup>33</sup> These contacts are thermally stable over a wide temperature range of 250 to 550°C, are non-penetrating and have contact resistance similar to that obtained with the alloyed NiAuGe contacts when annealed at 400°C. The Pd/Ge contacts were not pursued further because the blistering of the ELO GaAs film at the annealing temperatures has not been completely eliminated. Several preliminary experiments also indicated that it would have required considerable amount of effort to reproduce the published results consistently in our laboratory at Bellcore.

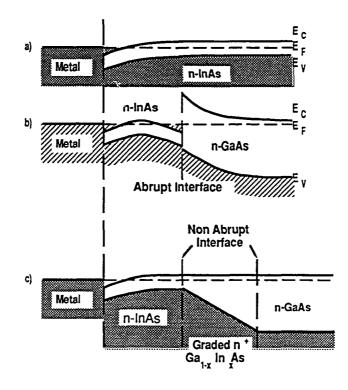

The second contacting scheme uses a thin, heavily doped, graded, psuedomorphic layer of  $In_xGa_{1-x}As$  on n<sup>+</sup> GaAs in the MESFET layer structure of the previous section. This contact was first proposed by Woodall, et al.<sup>34</sup> At room temperature, the surface Fermi level of InAs is pinned in the conduction band, so it provides low resistance path for electron flow, irrespective of the top metallization (Figure 2.19(a)). A graded layer of  $In_xGa_{1-x}As$  is required for smooth transition of large (~0.66 ev) discontinuity in the conduction bands of the InAs and GaAs (Figure 2.19(b)). Without this graded layer the current flow will be limited by the large barrier at the InAs/GaAs interface. With a high n-doping in the InAs and GaAs layers and the compositional grading of the In<sub>x</sub>Ga<sub>1-x</sub>As layer,  $\Phi_b < 0$  can be obtained as shown in Figure 2.19(c).

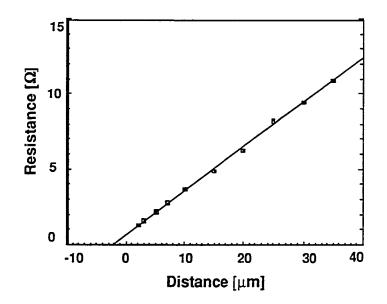

A test layer structure consisting of 25 nm n<sup>+</sup> In<sub>x</sub> Ga<sub>1-x</sub>As (x = 0.13, 0.4, 0.7, and 1, each 6 nm thick), 200 nm n<sup>+</sup> GaAs (2 x 10<sup>18</sup> cm<sup>-3</sup>) and 400 nm n-GaAs (n = 1 x 10<sup>17</sup> cm<sup>-3</sup>), was grown on a semiinsulating GaAs substrate using OMCVD (Figure 2.20(a)). The In<sub>x</sub>Ga<sub>1-x</sub>As thickness was below the critical thickness that causes misfit dislocations. A transmission line pattern was fabricated by ion milling of mesas down to the semi insulating substrate, a subsequent evaporation of 5 nm Ti/300 nm Au in an electron beam evaporator and lift-off. Contact resistance was evaluated by four probe measurement technique on the transmission line pattern. As shown in Figure 2.20(b), Y-axis intercept of the linear extrapolation of the resistance as a function of contact spacing gives a contact resistance of 0.06  $\Omega$ -mm and a specific contact resistivity of 7.5 x 10<sup>-7</sup>  $\Omega$ -cm<sup>2</sup>. This is comparable to the best reported results in literature.<sup>8-9-10</sup>

Figure 2.19: Band diagram of a non-alloyed ohmic contact to n-GaAs (a) Shows that any metal can make ohmic contact to n-InAs (b) Abrupt interface of n-InAs/n-GaAs due to conduction band discontinuity (c) A graded n-In<sub>x</sub>Ga<sub>1-x</sub>As layer makes ohmic contact to n-GaAs

| 24 nm  |           | $n^+$ - GaAs $\rightarrow$ In <sub>x</sub> Ga <sub>1-x</sub> As<br>(x=0.13, 0.4, 0.7, 1) |

|--------|-----------|------------------------------------------------------------------------------------------|

| 200 nm |           | n+-GaAs cap                                                                              |

| 400 nm |           | n-GaAs Channel                                                                           |

| 50 nm  |           | 1 x 10 <sup>17</sup> cm <sup>-3</sup><br>u-AlAs, Release layer                           |

|        | S.I. GaAs |                                                                                          |

Figure 2.20: (a) Epitaxial layer structure for MESFET with non-alloyed ohmic contact

A contact layer structure grown later with indium (In) content of up to 70% and without final layer of InAs had a similar contact resistance. Beyond ~70% In content in InGaAs, the Fermi level is pinned at the surface, so any further increase in In content does not improve the contact resistance.<sup>35</sup> Reduced indium content also helps improving the

Figure 2.20: (b) Contact resistance characteristics obtained from four probe measurements on a transmission line fabricated in the epitaxial layer structure shown in Figure 2.20(a). Contact width 100  $\mu$ m. R<sub>c</sub> = 0.06  $\Omega$ -mm,  $\rho_c = 7.5 \times 10^{-7}$   $\Omega$ -cm<sup>-2</sup>

surface morphology of the strained layer which in turn improves uniformity of wet chemical etching. It should be noted here that in our scheme of non-alloyed contacts, the  $n^+$ -GaAs to  $n^+$ -GaInAs was step graded as opposed to the more popular continuous grading. With the step grading of the In content, material growth is simplified without significant increase in the contact resistance.

## 2.4.3.1 Fabrication of MESFETs With Non-alloyed Ohmic Contacts

Enhancement and depletion mode MESFETs were made on GaAs wafer as well as ELO GaAs on silicon substrate using the epitaxial layer structure described in the previous section. MESFET fabrication was done following a standard fabrication procedure involving mesa etch down to semiinsulating GaAs or silicon dioxide dielectric buffer layer by ion milling, 5 nm Ti/ 200 nm Au ohmic contacts by electron beam evaporation and lift-

off, 10 nm Ti/ 14 nm Au gate metal evaporation and lift-off following gate definition by photolithography and recess etch in 1  $H_3PO_4$ : 1  $H_2O_2$ : 38  $H_2O$  and 1  $H_2SO_4$ : 8  $H_2O_2$ : 500  $H_2O$  solutions.

#### 2.4.3.2 DC Characteristics of an ELO MESFET With Non-alloyed Contacts

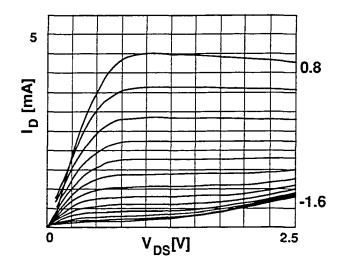

A depletion mode ELO MESFET with 1.5  $\mu$ m long gate had I<sub>ds</sub> = 180 mA/mm, maximum extrinsic transconductance g<sub>m</sub> of 180 mS/mm at V<sub>G</sub> = 0.8 V and pinch-off voltage V<sub>p</sub> = -1.6 V as shown in Figure 2.21. Contact resistance R<sub>C</sub> and specific contact resistivity as obtained from four terminal measurements on a transmission line tester were 0.15  $\Omega$ -mm and 5.25 x 10<sup>-6</sup>  $\Omega$ -cm<sup>2</sup> respectively.

Figure 2.21: Drain I-V characteristics of an ELO GaAs MESFET with non- alloyed contacts. Gate width  $W_g = 25 \mu m$ .  $I_{ds} = 180 \text{ mA/mm}$ ,  $g_{m-max} = 180 \text{ mS/mm}$ . Scale:  $V_{GS}$ , -0.2 V/step.

An enhancement mode MESFET made on a GaAs wafer with 1  $\mu$ m long gate had I<sub>ds</sub> = 77 mA/mm, maximum extrinsic g<sub>m</sub> = 100 mS/mm at V<sub>G</sub> = 0 V and pinch-off voltage V<sub>P</sub> = -0.2 V.

#### 2.4.3.3 RF Characteristics of an ELO MESFET With Non-alloyed Contacts

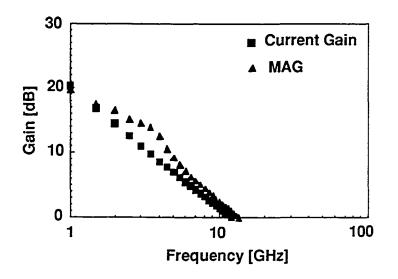

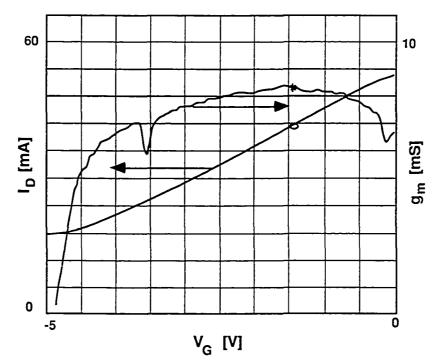

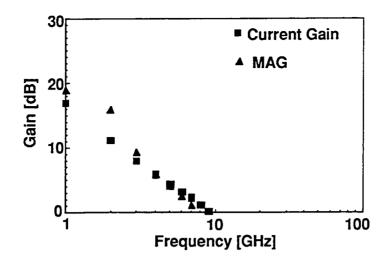

Figure 2.22(a) shows a transfer characteristics of an enhancement mode MESFET with the non-alloyed ohmic contacts. Current gain and maximum available gain as a function of frequency for the same MESFET are shown in Figure 2.22(b). A unity current gain frequency  $f_t = 12.5$  GHz and a maximum frequency of oscillation  $f_{max} = 7.5$  GHz is obtained for the 1 µm gate length MESFET operated in enhancement mode at  $V_{GS} = 0.5$  V. The MESFET had a maximum transconductance  $g_m = 201$  mS/mm, gate source resistance  $R_{GS} = 0.55 \Omega$ -mm, and gate-drain resistance  $R_{GD} = 1.1 \Omega$ -mm.

Figure 2.22(a): DC Transfer characteristics of an ELO MESFET on SiO<sub>2</sub>/Si with non-alloyed contact.  $g_{m-max} = 201 \text{ mS/mm}$ . Gate width  $W_g = 100 \mu \text{m}$

## 2.4.4 Development of MESFETs and HEMTs Without Recessed Gates