New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

Fall 1-31-2004

# Configurable computer systems can support dataflow computing

Anish Arvind Sathe New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Sathe, Anish Arvind, "Configurable computer systems can support dataflow computing" (2004). *Theses*. 530.

https://digitalcommons.njit.edu/theses/530

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## CONFIGURABLE COMPUTER SYSTEMS CAN SUPPORT DATAFLOW COMPUTING

#### by Anish Arvind Sathe

This work presents a practical implementation of a uni-processor system design. This design, named  $D^2$ -CPU, satisfies the pure *data-driven* paradigm, which is a radical alternative to the conventional von Neumann paradigm and exploits the instruction-level parallelism to its full extent. The  $D^2$ -CPU uses the natural flow of the program, *dataflow*, by minimizing redundant instructions like fetch, store, and write back. This leads to a design with the better performance, lower power consumption and efficient use of the onchip resources. This extraordinary performance is the result of a simple, pipelined and superscalar architecture with a very wide data bus and a completely out of order execution of instructions. This creates a program counter less, distributed controlled system design with the realization of intelligent memories. Upon the availability of data, the instructions advance further in the memory hierarchy and ultimately to the execution units by themselves, instead of having the CPU fetch the required instructions from the memory as in controlled flow processors. This application (data) oriented execution process is in contrast to application ignorant CPUs in conventional machines. The D<sup>2</sup>-CPU solves current architectural challenges and puts into practice a pure data-driven microprocessor. This work employs an FPGA implementation of the D<sup>2</sup>-CPU to prove the practicability of the data-driven computer paradigm using configurable logic. A relative analysis at the end confirms its superiority in performance, resource utilization and ease of programming over conventional CPUs.

## CONFIGURABLE COMPUTER SYSTEMS CAN SUPPORT DATAFLOW COMPUTING

by Anish Arvind Sathe

A Thesis Submitted to the Faculty of New Jersey Institute of Technology In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

**Department of Electrical and Computer Engineering**

January 2004

$\langle$

## **APPROVAL PAGE**

## CONFIGURABLE COMPUTER SYSTEMS CAN SUPPORT DATAFLOW COMPUTING

**Anish Arvind Sathe**

Dr. Sotirios Ziavras, Thesis Advisor Professor of Electrical and Computer Engineering, NJIT Date

Dr. Edwin Hou, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT. Date

Dr. Alex Gerbessiotis, Committee Member Assistant Professor of Department of Computer Science, NJIT. Date

## **BIOGRAPHICAL SKETCH**

Author: Anish Arvind Sathe

**Degree:** Master of Science

Date: January 2004

## **Undergraduate and Graduate Education:**

Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2004

Bachelor of Engineering in Electrical Engineering, Government College of Engineering, Pune, India, 2001

Major: Electrical Engineering

Dedicated to my parents

#### ACKNOWLEDGEMENT

First of all, I would like to thank Dr. Ziavras for his guidance and support during the whole tenure of my study for this thesis. I think only with his timely advice and great encouragement, I am able to complete this thesis work.

At the same time, I am also thankful to Dr. Hou and Dr. Gerbessiotis for participating in the thesis committee and providing valuable suggestions for improvement. Also many thanks to the entire staff of the Electrical and Computer Engineering department at NJIT.

Also I would like to thank senior colleagues, Tirupati, Satchit, Zafrul, Sunil and Xizhen for their immense help during practical difficulties. And finally, although not in the least, I want to thank all my friends here in NJIT who are behind me in hard time.

| C | Chapter Pa                                                 |    |  |

|---|------------------------------------------------------------|----|--|

| 1 | INTRODUCTION                                               | 1  |  |

|   | 1.1 Conventional von Neumann Architecture                  | 1  |  |

|   | 1.2 Dataflow Architectures                                 | 2  |  |

|   | 1.3 Related Work with the Dataflow Paradigm                | 3  |  |

|   | 1.4 Motivation                                             | 5  |  |

|   | 1.5 Objective                                              | 7  |  |

|   | 1.5.1 Design Objective                                     | 7  |  |

|   | 1.5.2 Reconfigurable Computing Systems                     | 8  |  |

| 2 | THE D <sup>2</sup> -CPU                                    | 12 |  |

|   | 2.1 Introduction                                           | 12 |  |

|   | 2.1.1 Some commonly used terms in the data-driven paradigm | 12 |  |

|   | 2.1.2 Design Requirements                                  | 12 |  |

|   | 2.2 D <sup>2</sup> -CPU Design                             | 13 |  |

|   | 2.2.1 General Instruction Format                           | 14 |  |

|   | 2.2.2 Execution Ready Unit (ERU)                           | 14 |  |

|   | 2.2.3 Hardware Manager (HM)                                | 17 |  |

|   | 2.2.4 External Cache (EXT-CACHE)                           | 18 |  |

|   | 2.2.5 Processor Unit for the PIM (PU-PIM)                  | 20 |  |

|   | 2.2.6 Support for Instruction Relocation                   | 20 |  |

|   | 2.2.7 Support for Exceptions                               | 21 |  |

|   | 2.2.8 Support for Loop Implementation                      | 22 |  |

# **TABLE OF CONTENTS**

# TABLE OF CONTENTS (Continued)

| C | Chapter F                                                      |      |

|---|----------------------------------------------------------------|------|

| 3 | DESIGN OF A FPGA BASED D <sup>2</sup> -CPU                     | . 24 |

|   | 3.1 Introduction                                               | . 24 |

|   | 3.2 Implementation of the D <sup>2</sup> -CPU                  | . 24 |

|   | 3.2.1 Instruction Set Format                                   | . 24 |

|   | 3.2.2 ERU Design                                               | . 27 |

|   | 3.2.3 Hardware Manager (HM)                                    | . 32 |

|   | 3.2.4 Out-Buffer                                               | . 33 |

|   | 3.2.5 EXT-CACHE (DSRAM <sub>i</sub> )                          | . 35 |

|   | 3.2.6 Main-Memory and PU-PIM <sub>i</sub> (DRAM <sub>i</sub> ) | . 39 |

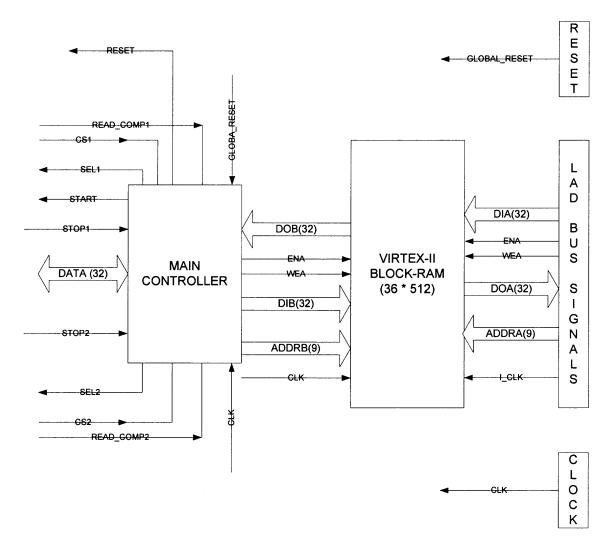

|   | 3.2.7 Main-Controller and Xilinx Virtex-II Block RAM           | . 41 |

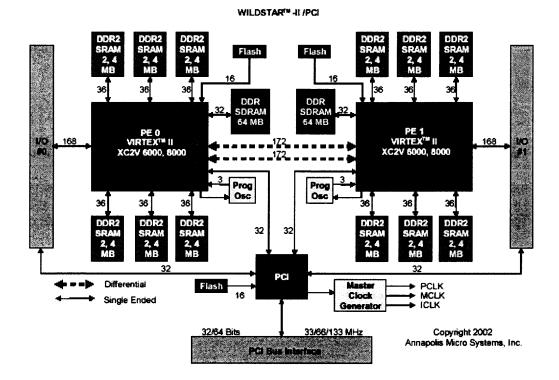

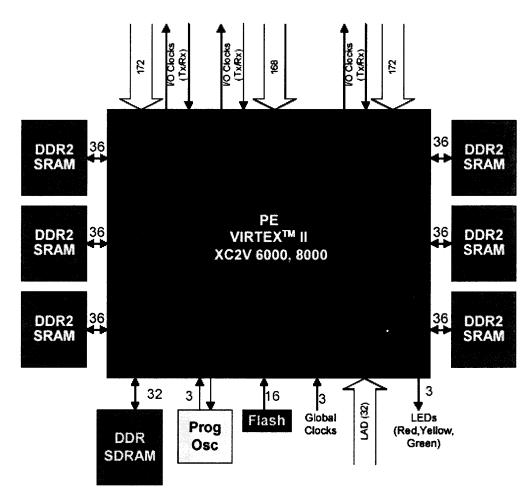

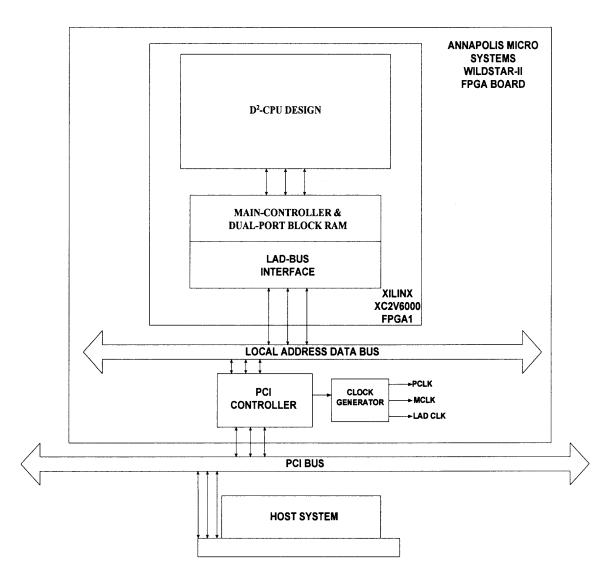

|   | 3.3 Overview of the Wildstar-II Board                          | . 42 |

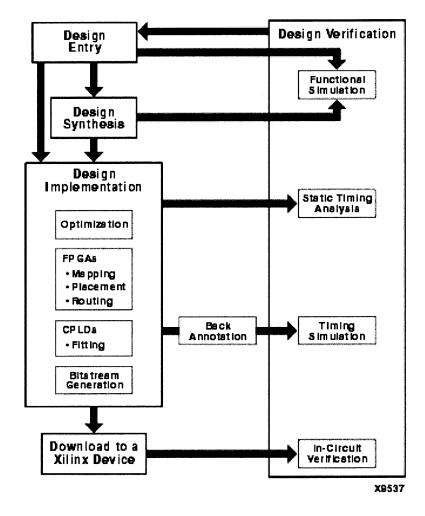

|   | 3.4 Design Flow and Implementation                             | . 45 |

| 4 | DATA FLOW GRAPHS and PROGRAMMING WITH D <sup>2</sup> -CPU      | . 49 |

|   | 4.1 Dataflow Graphs                                            | . 49 |

|   | 4.1.1 Introduction                                             | . 49 |

|   | 4.1.2 Dataflow Programs                                        | . 49 |

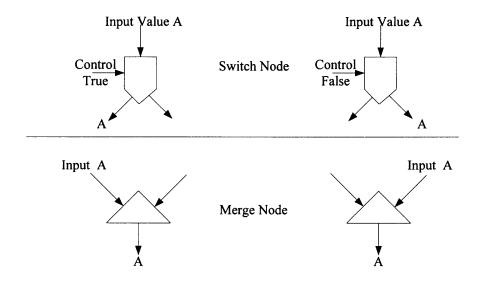

|   | 4.1.3 Types of Nodes                                           | . 51 |

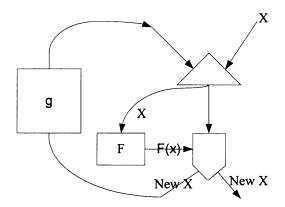

|   | 4.1.4 Reentrancy                                               | . 52 |

|   | 4.2 Programming with D <sup>2</sup> -CPU                       | . 54 |

|   | 4.2.1 Instruction Set                                          | . 54 |

# TABLE OF CONTENTS (Continued)

| Chapter                                          |  |

|--------------------------------------------------|--|

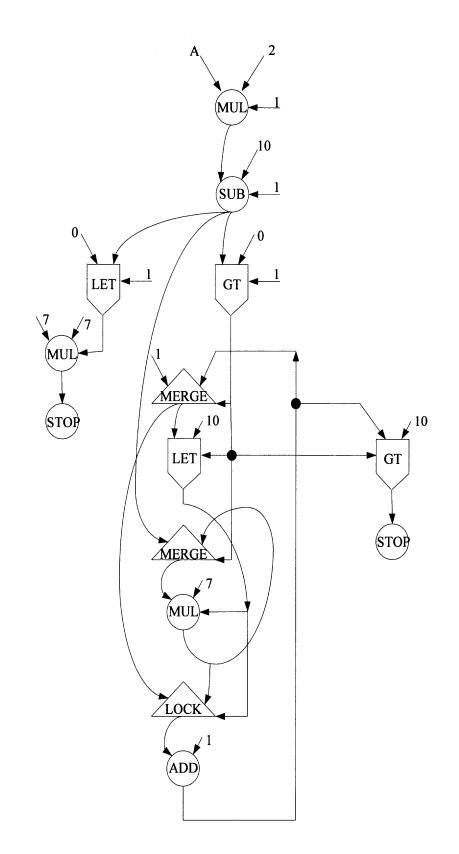

| 4.2.2 Sample Program                             |  |

| 5 RESULTS AND ANALYSIS OF D <sup>2</sup> -CPU 60 |  |

| 5.1 Results                                      |  |

| 5.2 Analysis                                     |  |

| 5.2.1 Storage Resources and Bus                  |  |

| 5.2.2 Turnaround time                            |  |

| 5.2.3 Software Support                           |  |

| 6 CONCLUSION                                     |  |

| APPENDIX: DESIGN REPORT FILES67                  |  |

| REFERENCES                                       |  |

# LIST OF TABLES

| Table | Pa                                                 | Page |  |

|-------|----------------------------------------------------|------|--|

| 3.1   | SRAM* Instruction Dependency                       | 30   |  |

| 4.1   | Instructions and OPCODEs                           | 55   |  |

| 4.2   | Sample Program in High Level and Assembly Language | 57   |  |

| 4.3   | Equivalent D <sup>2</sup> -CPU Code                | 58   |  |

| 5.1   | Results: Contents of Read and Write Buffer         | 61   |  |

| Figur | 'igure                                         |      |

|-------|------------------------------------------------|------|

| 2.1   | D <sup>2</sup> - CPU Architecture              | . 15 |

| 3.1   | OPCODE Format                                  | . 25 |

| 3.2   | OPFL Format                                    | . 25 |

| 3.3   | CAN, CAD, and CR Format                        | . 26 |

| 3.4   | The ERU Design                                 | . 29 |

| 3.5   | Hardware Manager                               | . 33 |

| 3.6   | Out-Buffer                                     | . 34 |

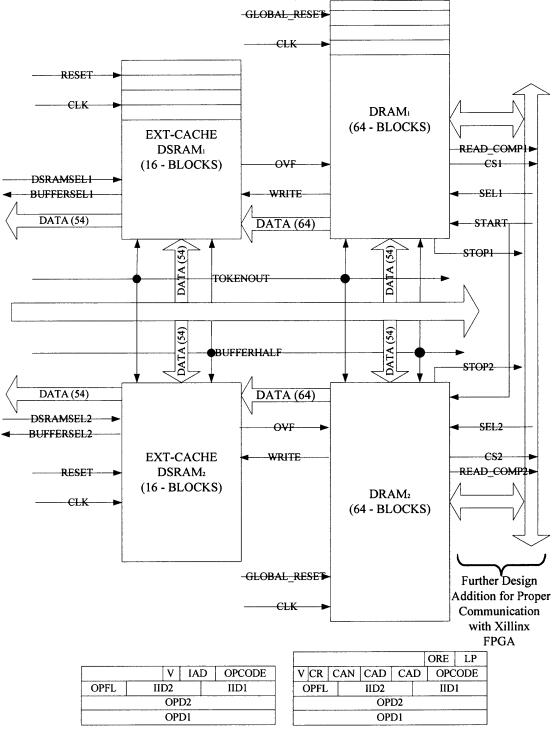

| 3.7   | EXT-CACHE and DRAM Memory Modules              | . 36 |

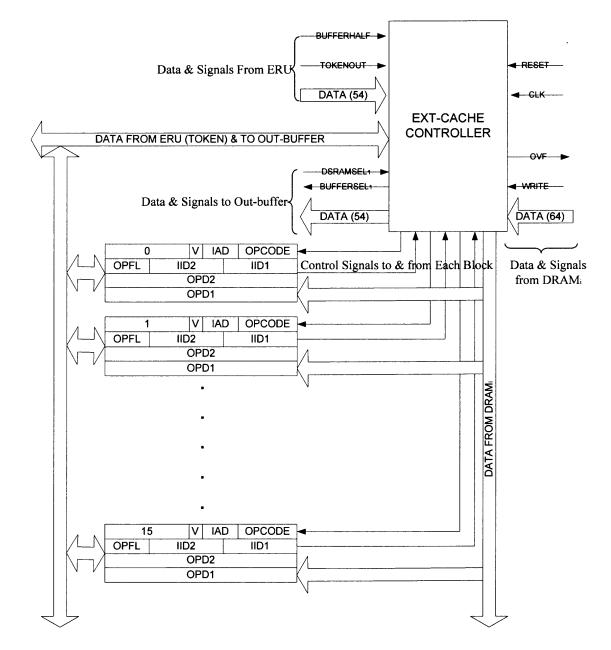

| 3.8   | Multithreading Approach to EXT-CACHE           | . 37 |

| 3.9   | Pure Data-driven Approach to EXT-CACHE         | . 39 |

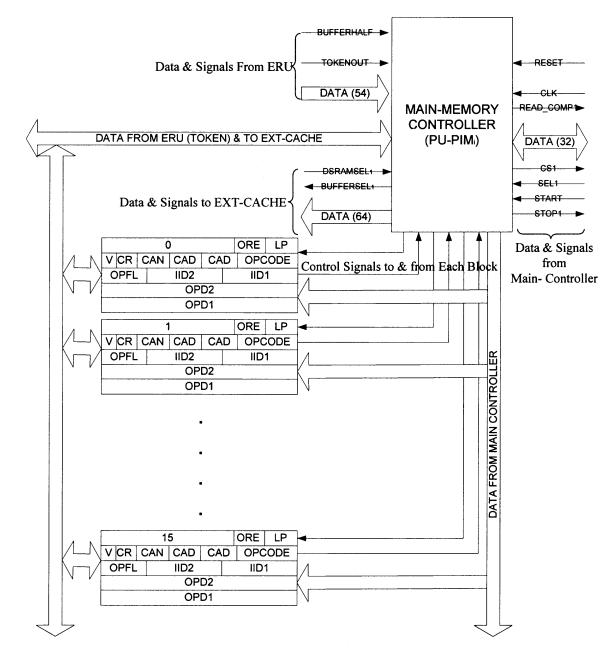

| 3.10  | Pure Data-driven Approach to Main-Memory       | . 40 |

| 3.11  | Main-Controller and Xilinx Virtex-II Block RAM | . 42 |

| 3.12  | Wildstar-II/PCI Block Diagram                  | . 43 |

| 3.13  | Wildstar-II Processing Module                  | . 44 |

| 3.14  | Communicating with the Host System             | . 46 |

| 3.15  | FPGA design flow                               | . 47 |

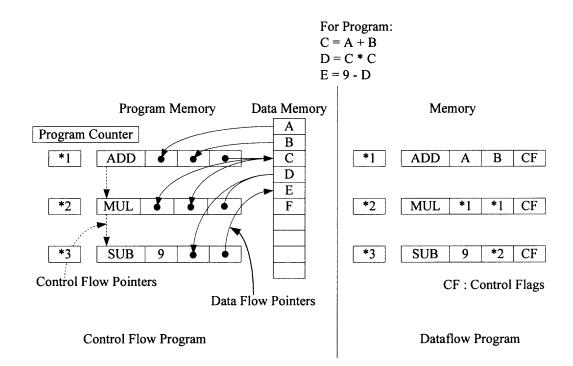

| 4.1   | Comparison: Control Flow vs. Dataflow          | . 50 |

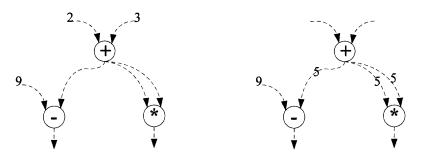

| 4.2   | Nodes, Arcs and Firing of Nodes                | . 51 |

| 4.3   | Switch and Merge Node.                         | . 51 |

# LIST OF FIGURES

# LIST OF FIGURES (Continued)

| Figure |                                              |    |

|--------|----------------------------------------------|----|

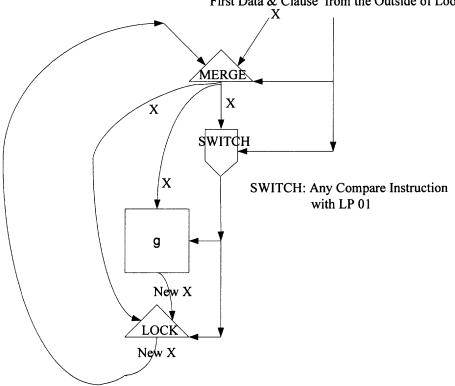

| 4.4    | Lock Method for Reentrancy.                  | 53 |

| 4.5    | Lock Method Used in D <sup>2</sup> -CPU.     | 56 |

| 4.6    | Flow Diagram for Code Presented in Table 4.3 | 59 |

.

#### CHAPTER 1

#### **INTRODUCTION**

#### **1.1 Conventional von Neumann Architecture**

Conventional computers are based on a control flow mechanism. The order of program execution is decided by the user and is stated in the program. The program counter (PC) is used at the hardware level to obey this order. This PC sequences the execution of instructions in a program. Ultimately, the PC leads to the sequential execution of a program on a *control-driven* architecture. These types of computers use shared memory to hold instructions and data objects. Instructions and data objects are stored differently. Many instructions can change shared memory. So, dependencies and control flow have to be followed carefully for the correct execution of programs. The central processing unit (CPU) fetches each instruction and its data and executes it. This makes the CPU the master of computer system, where as the shared memory remains "dumb". This creates a large amount of redundant operations and, in turn, low utilization of the resources directly related to the implementation of application algorithms.

Each fetch instruction directly or indirectly relates to memory use. For programming flexibility, these computer systems became very complex at the hardware level with large complex instruction sets. This has created many processor families, though the emphasis remains on the reducing the complexity, leading to RISC, or increasing operations per cycle leading to pipelining and super-pipelining, or increasing the parallel operations per cycle leading to superscalars and VLIW machines.

To increase the clock frequency and decrease the cycles per instruction (CPI) functional units are divided into smaller sets of logic. Different stages are created for each functional unit leading to *pipelining*. With more advanced technology the stages are further

divided to develop *super-pipelined* CPUs which ideally increase throughput in linear with the number of stages.

Through many years of research, it was realized that only 25% of the instructions of complex instruction sets are used often. This fact implies 75% of the hardware-supporting other instructions are not used frequently. So, putting such instructions into software saved valuable chip space leading to RISC processors; the latter space can now be used for large register sets, local caches, and , sometimes, for floating point units. Instruction and data caches can then be made separate. This modification gives higher clock rate, fewer cycles per instruction (CPI). They are often called *scalar-RISC* processors.

With the advent of VLSI technology more on-chip area is available and that can be used to increase in resources and, sometimes, for resource duplications. This leads to *superscalar* processors with more than one functional unit. Pipelining and super-scalar principles are used to create super-scalar, super-pipelined processors, which result in less than one CPI. Very large instructions (VLIW) were introduced to reduce memory latencies.

Unfortunately, the trend in CPU design has been to take advantage of increases in transistor densities to include additional features. Today's processors are nothing else but combinations of past research and that can implement wide instruction issue (VLIW), out-of-order instruction execution (data-flow after instruction issue), aggressive speculation, and in-order retirement of instructions.

#### **1.2 Dataflow Architectures**

In a dataflow computer, the execution of an instruction is driven by the data availability instead of being guided by the program counter. Ideally, in the pure dataflow computation model an instruction is executed as soon as its operands become available. The instructions in dataflow programs are not ordered in any way and there is no need of a program counter. Instructions under this model carry their own data, i.e. operands, with them. As soon as an instruction produces a result, the result is broadcasted to all needy instructions. Again, as soon as any instruction gets all its operands, it is ready to execute and it moves to the CPU in the dataflow paradigm. Thus, the CPU doesn't fetch any instruction from memory. In short, the CPU is deprived of its Master right in the dataflow model, becoming a PU and memories become intelligent. This gives distributed control in the computer system.

The dataflow model has the potential to exploit all the parallelism available in a program. Since the execution is driven only by the availability of operands at the inputs to the functional units, its parallelism is limited only by the actual data dependencies in the application program rather control dependencies that become problematic in the conventional von Neumann model. The dataflow execution follows precisely dataflow graphs, which have embedded inherent parallelism. Thus, dataflow architectures represent a radical alternative to von Neumann architectures. There is a lot of work already done for the dataflow paradigm and there are also other architectures available which use both dataflow and von Neumann architectures to exploit, the inherent parallelism in dataflow and the ease of control flow in von Neumann respectively.

#### **1.3 Related Work with the Dataflow Paradigm**

The dataflow computation paradigm till now has been primarily employed in the implementation of parallel computers, where this paradigm is basically applied among instructions running on different PC-driven processors. The majority of dataflow multiprocessors and multi-computers used COTS (Commercial Off The Shelf) processors, which gave them the advantage of fast designing however they still remain PC driven at individual processor level. In contrast, a data-driven processor was introduced in [9] that utilizes a self-timed pipeline scheme to achieve distributed control. This design is based on

the observation that the *data-driven* paradigm can accommodate very long pipelines that are controlled independently, since packets flowing through them always contain enough information and data on the operations to be applied. However, this processor design also suffers from several constraints imposed by current design practices. Several data-driven architectures have been introduced for the design of high performance ASIC devices [10, 11]. In addition, several techniques have been developed for the implementation of ASICs in VLSI when the dataflow graphs of application algorithms are given. However, these techniques employ straightforward, one-to-one mapping of nodes from the dataflow graph onto distinct functional units in the chip. An exception is the recently proposed implementation of dataflow computation on FPGAs [12].

Multithreading is another widely used principle in CPU design. For multithreaded processors, each program is partitioned into a collection of instructions. Such a collection is called a thread. Instructions in a thread are issued according to the conventional von-Neumann model of computation, i.e. they are sequential. Similar to the dataflow model, instructions are run based on data availability [5]. A large degree of thread-level parallelism is derived through a combination of programmer, compiler, and hardware efforts. Similar to the above case COTS processors can be used for this purpose. Data dependencies are taken care of by the compilers and split-phase techniques guarantee no trouble without extra memory-access delay. Multithreading supports the dataflow execution among threads. The Tera Multi-threaded architecture (MTA) is an example of a distributed shared memory parallel machine with multithreaded computational processors and interleaved memory modules connected via a packet-switched interconnection network [7]. Similarly Efficient Architecture for Running Threads (EARTH) is a multiprocessor that contains multithreaded nodes [6]. Again each node contains a COTS RISC processor for executing threads sequentially and an ASIC synchronization unit that supports dataflow like thread synchronizations and scheduling. A thread is activated when all its input data become available and then they can spawn or create many other threads. This principle directly relates to the dataflow graphs.

As far as single processors are concerned, the hyper-threading technology, introduced in the Intel Pentium-IV, provides thread-level-parallelism (TLP) on a single processor, resulting in increased utilization of processor execution resources [19]. As a result, resource utilization yields higher processing throughput. The hyper-threading technology is a form of simultaneous multi-threading technology (SMT) where multiple threads of software applications can run simultaneously on one processor. However, this is achieved by the duplication of resources on each processor. To match the instruction level parallelism (ILP) of applications, it is a usual practice to design microprocessors with resource duplication. Several copies of commonly used functional units are implemented in the CPU, which is called super-scaling. Multiple-issue processors [8], an alternative to vector processing units, apply this super-scaling principal for dynamic execution whereas VLIW can be used for static scheduling. In VLIW, the compiler combines many independent instructions together to be sent simultaneously to the CPU. Each component instruction is to use its own execution unit in the CPU. Resource widening [4] is another concept implemented in the Intel IA-64. This Explicit Parallel Instruction Computing (EPIC) design approach used in the Intel IA-64 is similar to the VLIW paradigm but increases the hardware complexity.

#### **1.4 Motivation**

The high complexity of individual processors has a dramatic negative effect on the overall complexity and performance of parallel computers. Current design families, like RISC, CISC, and VLIW processors show several deficiencies. They are characterized by large amounts of redundant operations and low utilization of resources directly related to the

implementation of application algorithms. In all these architectures, an instruction fetch operation is still required only due to the von Neumann PC-driven basic model. The CPU request to the memory is not part of any application algorithm but the result of centralized control during program execution. To reduce this time penalty, all of today's implementations use instruction *pre-fetching* with an instruction cache. This wasted recourses which could be otherwise used in more direct application related tasks. Another problem with current designs is the fact that the operands do not often follow their instructions to the CPU. The only exception is the instructions that either use immediate data or their operands reside in the CPU registers. Additional fetch cycles may then be needed to fetch these operands from either the main memory or the attached cache. However, these fetch cycles also should be avoided, if possible. These fetch cycles are even unavoidable with current dataflow designs that use activation frames. Again, to mitigate this problem current designs choose data cache memories; corresponding transistors could be otherwise be used in more productive tasks. In contrast, in the pure dataflow paradigm computing, the instructions go to the execution unit on their own (Intelligent Memory) if needed, along with their operands, as soon as they are ready to execute.

Thus, advances in current CPU design lack the potential for dramatic performance improvements because they don't match well with the natural execution of program flows. To get rid of such critical problems or, sometimes, to lessen this effect, designers used many expensive hardware techniques. However, this hardware is not used to run the relevant program directly but just aid in increasing the efficiency or through put. This results in small productive utilization of the overall hardware system. The time penalty of fetching instructions and operands in conventional von Neumann architectures is reduced by extensively using instruction and data pre-fetching, software preprocessing, internal data forwarding and cache techniques. Resulting new architectures result in the following

penalties:

- 1. In an effort to hide the mismatch between the application's needs and the PC-driven execution model, we waste numerous on chip resources. Many hundreds of thousands or millions of transistors are needed to implement some of the above techniques within a single CPU, whereas the productive utilization of these resources is rather small.

- 2. Power consumption increases for two reasons. Firstly, the overheads of the instruction fetch cycle, which is not an application requirement, appears for each individual instruction in the program. This is too much an overhead to pay for centralized control during program execution. Since these are inter-chip data transfers that are quite expensive and time consuming, this cost is very substantial. Secondly, unnecessary power consumption results from pre-fetching unneeded instructions and data into caches. Mobile computing, recently popular and dominating the computer field needs very high power efficiency for longer battery usage.

- 3. Numerous cycles are wasted when a hardware exception or interrupt occurs. This is because after the CPU gets informed about the external event, it has to store the current state of the machine and then fetch code to run the corresponding interrupt service routine. If the appropriate context switching is selected outside of the CPU, then the appropriate instructions can arrive promptly.

#### 1.5 Objective

#### **1.5.1 Design Objective**

It is now widely accepted that the procedure applied within many advanced microprocessors for the execution of CPU resident instructions resembles closely the data-driven computation paradigm. This is due to the fact that these advanced microprocessors apply Tomasulo's algorithm with super-pipelining techniques with using resource reservation stations that keep track of data dependencies between instructions in the CPU.

The data-driven CPU ( $D^2$ -CPU), proposed in [1], is a design technique based on the pure dataflow computation paradigm. For ease and efficiency of instruction decoding and implementation, it also uses principles like large register files and active instructions with their operands within the processing unit, simple instructions, and multiple issues of

instructions. In this design, the dataflow model of execution is applied simultaneously to all instructions in the program. This proposed  $D^2$ -CPU design has the following architectural objectives:

- 1. This innovative design has a radical single processor design that implements the datadriven computation paradigm in its pure form. It also employs active memory techniques.

- 2. A processor design with distributed control that minimizes the amount of redundant operations and maximizes performance.

- 3. High utilization of resources in productive work, i.e. work not associated with redundant operations but supports direct application flow.

- 4. Low hardware complexity for high performance.

- 5. Low cost and power consumption.

Our main objective here is to implement the  $D^2$ -CPU design on the FPGAs.

#### 1.5.2 Reconfigurable Computing Systems

Field-Programmable Gate-Arrays (FPGAs) have been used in systems spanning a broad range of applications ever since their introduction in 1985 [14]. Most of the systems use FPGAs as a glue logic providing the advantages of high integration levels without the expense and risk of custom ASIC devices. However, as FPGAs have increased in capacity, their use as in-system configurable computing elements has received considerable attention. The use of FPGAs as reconfigurable computing elements is poised to expand rapidly in the commercial market, where FPGA-based parallel processors will compete with parallel computers and even some supercomputers in computationally intensive applications. Many research projects were done over the past few years in developing these FPGA-based highperformance machines. Reconfigurable FPGA technology holds the potential of reshaping the future of computing by providing the capability to dynamically alter hardware resources to optimally serve immediate computational needs [13].

The FPGA-based reconfigurable systems can be used as specialized co-processors, processor-attached functional units, attached message routers in parallel machines, and specialized systems for parallel processing. This was made possible with the advent of multimillion gate FPGAs. In the past decade, FPGA-based configurable computing machines have acquired significant attention for improving the performance of algorithms in several fields, such as DSP, data communications, genetics, image processing, pattern recognition, etc. FPGA-based co-processors are implemented as attached co-processors dedicated to offloading computationally intensive tasks from host processors in PCs and workstations. Reconfigurable co-processors are viable platforms for a wide-range of computationallyintensive applications. The FPGA-based configurable computing systems have garnered support from the scientific and academic communities. Many research projects have demonstrated the viability of configurable computing systems that can deliver the performance of supercomputers for specific applications. Most of the FPGA-based parallel machines currently reside in multi-FPGA systems interconnected via a specific network [15]. Some of the configurable computing systems are:

- 1. The Ganglion Project at the IBM Almaden Research Centre used XC3090 and XC3042 FPGA devices to implement a feed-forward, fully interconnected neural network on a single VME board.

- 2. DEC's Paris Research Lab has designed and implemented four generations of FPGA-based configurable co-processors called Programmable Active Memories (PAMs).

- 3. SPLASH-1 includes a 32-stage linear-logic array with a VME-interface to a SUN workstation. Each stage consists of an XC3090 FPGA and a 128Kbyte static memory buffer. SPLASH-1 outperformed Cray-2 by a factor of 325 in specific applications and a custom built NMOS device by a factor of 45. SPLASH-2 uses 17 XC4010 FPGA devices arranged in a linear array and also interconnected via a 16x16 crossbar.

- 4. PRISM-1 from Brown University coupled XC3090 with the Motorola M68010 microprocessor and PRISM-11 coupled XC4010 FPGA devices as co-processors to an AMD29050 RISC processor.

Advances in VLSI technology not only brought about multi-million gate FPGAs, but also facilitated the integration of numerous functions onto a single FPGA chip. Peripherals formerly attached to the FPGA at the board level now can be embedded into the same chip with the configurable logic. According to Xilinx predictions, the count of FPGA system gates will exceed 50 million and FPGA chips will operate at more than 500 MHz [16].Thus, the availability of multi-million system gates in FPGAs introduced a new design paradigm, System-On-a-Chip (SOC), with which entire systems can be implemented on a single FPGA chip without the need for expensive non-recurring engineering charges or costly software tools.

The FPGAs have provided an alternative method to computing by supporting the fine-tuning of hardware to match software requirements. The fact that the number of system gates in FPGAs has been increasing rapidly in recent years encourages the development of large–scale application-specific custom computing machines on FPGAs for better hardware performance. While these FPGA-based Custom Computing Machines (CCMs) may not challenge the performance of microprocessors for all applications, for specific applications an FPGA-based system can offer extremely high performance. This led us to develop an FPGA-based D<sup>2</sup>-CPU proposed in [1].

The main objective of this thesis is to design a general purpose  $D^2$ -CPU architecture and implement it on an FPGA. The data-driven computation model is applied simultaneously to all the instructions in the program. Not only the CPU but the L<sub>1</sub> cache, L<sub>2</sub> cache, and main memory are also implemented with this principle. This thesis mainly aims at implementing this architecture to prove the viability of the data-driven computational paradigm with current FPGA technologies.

The proposed design concept is discussed in Chapter 2. The detailed implementation is reported in Chapter 3. The theory of dataflow graphs and programming with the  $D^2$ -CPU

are introduced in Chapter 4. Chapter 5 summarizes design results and comparative analysis with conventional designs and Chapter 6 concludes and proposes future design objectives and challenges related to the data-driven paradigm and especially to the  $D^2$ -CPU. The target system is the Annapolis Micro systems (AMS) Wildstar-II development board that has two Xilinx Virtex-II FPGAs.

## **CHAPTER 2**

# THE D<sup>2</sup>-CPU

## 2.1 Introduction

### 2.1.1 Some Commonly Used Terms in the Data-driven Paradigm

This Chapter begins by introducing briefly the semantics of the data-driven computer

paradigm. The terms here basically describe the sequence of steps for the implementation of

an instruction under the data-driven computation paradigm.

- 1. *Instruction Issuance or Firing*: It is the departure of the instruction for the execution unit. An instruction is fired just after all of its operands become available to it.

- 2. *Token Propagation*: It is the propagation of an instruction's result to other instructions that need it. As soon as an instruction completes execution, it makes copies of its result for all other instructions that need it. Different tokens that contain the same result are then forwarded to different needy instructions.

- 3. *Instruction Dissolvement*: It is the destruction of the instruction just after it produces its entire token for other receiving instructions. It depends upon the instruction. Loop instructions have to be treated differently because they may be reused in the programs.

## 2.1.2 Design Requirements

Following are the major requirements clearly mentioned in [1] for the D<sup>2</sup>-CPU design that

satisfied our objective and are in line with the data-driven computation paradigm.

- 1. Programs are developed using fine-grain graphical, or equivalent, languages that show explicitly all data dependencies among the instructions. Libraries of existing routines can further aid programming, as long as they are developed in this manner. Also, usage of a graphical language simplifies code development and facilitates better assignment of tasks to parallel computers containing many D<sup>2</sup>-CPU.

- 2. Instructions contain all their operand fields, as in the pure data-driven model.

- 3. A software preprocessor finds all the instructions in the program that can run in the very beginning because of non-existent data dependencies. These head instructions are to be sent first to the execution unit.

- 4. Following the head instructions to the execution unit are instructions that are to receive all their input operands from one or more head instructions. These instructions can proceed for execution just after they receive their operands.

- 5. Instructions that are to receive one or more operands from instructions that are ready to execute but are still missing one or more operands leave for an external cache, called EXT-CACHE, where they wait to receive their tokens. To reduce the traffic, instructions that will receive the same result are grouped together in the cache in an effort to collectively receive a single token that can be used to write all relevant operand fields. If not all of the token receiving instructions that do not fit.

- 6. Only one copy of each instruction, including its operands, resides at any given time within the entire machine, i.e. in the memory, cache, and CPU. This is in contrast to the wide redundancy of instructions and data present in the cache, memory and CPU of the conventional control driven model.

- 7. Instructions do not keep pointers to their parent instructions. Therefore, they are dormant till they are forced into the EXT-CACHE or the execution unit in order to receive their tokens.

- 8. After an instruction is executed, it is dissolved. However, special care is needed for instructions that have to be reused in software loops. A relevant technique that permits instruction reuse is presented in the next Chapter.

- 9. Instructions have unique IDs for token passing only while they reside outside of the execution unit. These IDs are used to find instructions and force them into the EXT-CACHE or execution unit. In the latter case, an interface actually keeps track of these IDs so that minimal information is manipulated or stored in precious execution unit resources.

# 2.2 D<sup>2</sup>-CPU Design

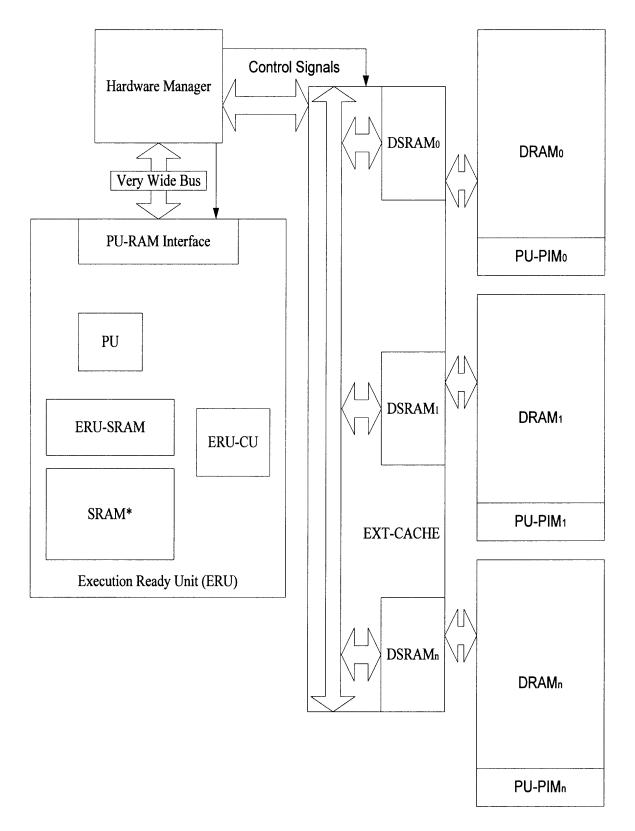

This Section will present the innovative  $D^2$ -CPU design proposed in [1]. Primarily this design takes advantage of advances in Processor In Memory (PIM), cache memory, and IC technologies to implement efficiently the data-driven paradigm. Figure 2.1 shows the system architecture. We will start with the core of this design, i.e. the Execution Ready Unit (ERU) and will advance to the main-memory. The instruction format at each level is different.

#### **2.2.1 General Instruction Format**

Each instruction comprises an opcode field (OPCODE) and, without loss of generality, up to two operand fields (OPD<sub>1</sub> and OPD<sub>2</sub>). The number of operand fields depends upon the type of operation, i.e. unary or binary respectively. Depending upon its location in the system, each instruction also consists of its own instruction ID defined by its location in the main memory (IAD), instruction IDs upon which  $OPD_1$  and/or  $OPD_2$  are depended-  $IID_1$  and  $IID_2$ , respectively. It also comprises the FLAG field that points to instruction location for dependence. This FLAG field makes each instruction intelligent and decides its further action. The instruction format at each location will be discussed in detail below. For token propagation, each token consists of an IAD i.e. the instruction ID that generates this token and its RESULT.

#### 2.2.2 Execution Ready Unit (ERU)

The ERU is the core of this system and replaces conventional CPUs. It consists of functional units and big register files in terms of on-chip caches. The ERU comprises the following components:

Processing Unit (PU): In the PU, the operations specified by the instructions are executed. It contains several functional units that can be used by a single, or simultaneously, by multiple instructions. Its design follows the basic RISC model. The PU contains at least one copy of an adder, a multiplier and a logic unit. For multimedia and engineering applications a vector unit also can be added to the PU. Each instruction at the input to the PU level only comprises of the OPCODE, OPD<sub>1</sub>, OPD<sub>2</sub> and IAD fields, whereas at the output it forms tokens with the IAD and RESULT fields.

Figure 2.1 D<sup>2</sup>- CPU Architecture [1].

- Static RAM in the ERU (ERU-SRAM): It contains instructions ready to execute, i.e. instructions with all of their required operand fields filled. However these instructions cannot proceed to the PU, because the functional units that they require are currently used by some other instructions. This cache storage of ready to execute instructions guarantees very high performance. An instruction at this point consists of the OPCODE, OPD<sub>1</sub>, OPD<sub>2</sub> and IAD fields.

- *SRAM*\* (static RAM): It contains instructions with one or more unfilled operand fields that are all to be written by one or more instructions currently residing in the PU and/or ERU-SRAM. Therefore, these instructions are going to execute in the very near future. Whenever the PU unit becomes available, an instruction from the ERU-SRAM, which has a large number of recipient instructions in the SRAM\*, will go for execution. An instruction at this point consists of the OPCODE, OPD<sub>1</sub>, OPD<sub>2</sub>, IAD and IID<sub>1</sub> and/or IID<sub>2</sub> fields.

- *ERU-Control Unit (ERU-CU)*: It is the control unit of the ERU. It keeps track each time of the total number of result recipient instructions in the SRAM\* for each instruction currently in the ERU-SRAM. It also facilitates data forwarding within the ERU, for recipient instructions in the SRAM\*.

- PU-RAM interface: It receives all instructions entering to the ERU from the hardware manager. It distributes the instructions accordingly to the PU, ERU-SRAM and SRAM\*. When an instruction produces a result, then the PU-RAM interface propagates this token to the EXT-CAHCE and DRAM.

#### 2.2.3 Hardware Manager (HM)

The hardware manager is placed between the ERU and EXT-CACHE. It performs the following tasks:

- It initially sends the head instructions from the EXT-CACHE of the program to the ERU for execution.

- Whenever one of the remaining instructions proceeds to the ERU, it first makes a request to the HM for a virtual ID. This virtual ID will uniquely identify the instruction during its residency in the ERU. The ID is a small number in the range 0 to n-1, where n is the maximum number of instructions that can reside simultaneously in the ERU. Obviously these IDs are recycled. Virtual IDs are assigned to instructions by the HM, in place of their physical ID/address due to the following reasons:

- 1. To minimize the required bandwidth between the ERU and external components. This is due to the fact that each instruction carries with it IAD,  $IID_1$  and/or  $IID_2$ .

- 2. To minimize the size of the ERU internal resources storing the instructions' IDs, especially SRAM\* resources.

- 3. To minimize the required resources, that processes the ERU resident information.

- It maintains a table that can be accessed to quickly translate on the fly virtual IDs into physical IDs and also vice-versa.

The instruction at this point consists of the OPCODE,  $OPD_1$ ,  $OPD_2$ , IAD and  $IID_1$  and/or  $IID_2$  fields. The IAD, and  $IID_1$  and/or  $IID_2$  fields contain the virtual ID at the ERU side whereas the physical IDs at the EXT-CACHE side.

#### 2.2.4 External Cache (EXT-CACHE)

The external to the execution unit cache (EXT-CACHE) is distributed. It is formed as a collection of Distributed SRAMs (DSRAM). The main-memory is also correspondingly in distributed in nature and formed as a collection of Distributed RAMs (DRAM). For each DRAM module there is one DSRAM module. The EXT-CACHE contains at any time instructions that are to receive a token from instructions residing at that time in the ERU. In fact, three classes of instructions may reside in the EXT-CACHE at any time during the program execution. Those are:

- 1. Instructions with two unfilled operand fields. One of these fields is to be filled with data that will arrive from an instruction currently in the ERU.

- 2. Instructions with one unfilled operand field for which the token is to arrive from an instruction currently residing in the ERU. These instructions can not fit in the ERU because the SRAM\* is fully occupied.

- 3. Instructions that are not missing any operands but they can not fit in the ERU-SRAM because it is fully occupied. But such instructions ideally have to be in the ERU.

As already mentioned in our objective, only one copy of each yet to execute instruction is present in the system at any time during the program execution. The part of the program that still needs to be executed is distributed among the off-chip DRAM and EXT-CACHE, and the on-chip ERU-SRAM, SRAM\*, and PU. The currently achievable transistor density for chips allows the implementation of large memories to realize the ERU-SRAM, SRAM\*, and DSRAM components so that they very rarely overflow. Without hardware faults, there is no possibility for the appearance of deadlocks in this design. Even if the ERU-SRAM is fully occupied at some time, the instructions in it will definitely execute in the near future because the PU will be released soon by the currently executing instructions. If one or more instructions outside of the ERU are ready to execute but can not enter the ERU because the ERU-SRAM is fully occupied, then they wait in the external queue until space is released in the ERU-SRAM. A similar technique is applied if the SRAM\* is fully occupied. In fact, the ERU-SRAM and SRAM\* can be combined to single component. For the sake of simplicity, it was proposed to be separate.

For each program memory (main memory) module DRAM<sub>i</sub>, there is a distinct EXT-CACHE module DSRAM<sub>i</sub>, for each  $i = 0, 1, 2, 3 ..., 2^d - 1$ . An instruction in the EXT-CACHE consists of the OPCODE, OPD<sub>1</sub>, OPD<sub>2</sub>, IAD, IID<sub>1</sub>, IID<sub>2</sub> and FLAG fields. The operand field locator (OPFL) in each FLAG field indicates instruction dependency or status, i.e. how many operands (nil, one or two) the instruction still needs to go for execution.

As already discussed above each token leaving the ERU also contains the virtual ID of that instruction. The hardware manager changes this virtual ID to the physical ID and then broadcasts this token to all DSRAMs in the EXT-CACHE. The important point is that the DSRAM entries are created dynamically by the hardware manager, have a very short life span, and exists only inside the DSRAM. They are created only when instructions leave for the ERU. That is, it doesn't load into the computer system pointers to parent instructions, which is in line with objectives specified in Chapter 1.

The ERU receives instructions from the hardware manager for execution. Truly the hardware manager forces instructions into the ERU by first storing them into the FIFO buffers and then prompting the ERU to read from these buffers using a very wide bus. Asynchronous communications with appropriate acknowledgments between these two units achieve this task. Therefore, it is not the ERU that fetches instructions for execution, but it is fed with instructions directly by the EXT-CACHE which is a fundamental principle of data-driven paradigm. Here, the program counter is replaced by short IDs i.e. IADs. Fetching shorter IDs is not a heavy penalty to pay for the elimination of the program counter and still the PC- driven CPU requires the implementation of a wide address bus and appropriate control lines. The ERU needs fewer pins to fetch this ID, whereas PC-driven CPUs need more pins to access instructions.

#### 2.2.5 Processor Unit for the PIM (PU-PIM)

Each DRAM has a unique PU-PIM attached to it. This unit carries out the following tasks:

- 1. It loads the corresponding DSRAM<sub>i</sub> with all those instructions from the DRAM<sub>i</sub> that are to receive tokens from the instructions leaving for the ERU and also missing data for two operand fields. Also, it always updates appropriately the DSRAM<sub>i</sub> directory.

- 2. It removes instructions from the DRAM<sub>i</sub> that are not to be executed further because of loop exiting. The reuse of instructions for the implementation of program loops is addressed later in this Chapter.

- 3. It maintains three distinct lists of addresses for instructions in the DRAM<sub>i</sub>, if any, that do not fit in the EXT-CACHE, ERU-SRAM and SRAM\*, respectively. These lists are kept in the local DRAM<sub>i</sub> for instructions that do not fit in one of these units because of respective overflow.

- 4. It copies data from tokens broadcast by the ERU via HM into the appropriate fields of instructions appearing in the EXT-CACHE and SRAM\* units.

- 5. It caries out garbage collection in the DRAM<sub>i</sub> since the data-driven model of computation necessitates deallocation of the memory space dynamically through instruction dissolvement.

- 6. It finds the instructions in the  $DRAM_i$  and  $DSRAM_i$  that are to receive their last operand from instructions leaving for the ERU and forwards them to the HM that finally stores them into the SRAM\*.

- 7. It services requests by the program loader and the operating system for instruction loading and relocation in the DRAM<sub>i</sub>.

Incorporation of the DRAM i.e. program memory in the  $D^2$ -CPU is necessary [1], as accessing data with distinct addresses is quite natural. In fact, there exist many devices that work extreme efficiently using strict memory addressing schemes.

#### 2.2.6 Support for Instruction Relocation

Multiprogramming and virtual memory are now common practices, and very convenient features for the PC-driven paradigm. But both of them require support of instruction relocation. Instruction relocation in the data-driven computation seems to be a very difficult problem to solve because of the need for token passing with ever changing instruction addresses. [1] Proposes the following solution for the implementation of instruction relocation in a way that token passing using original instruction IDs is still possible.

- The compiler-loader combination assigns the original instruction IDs to correspond to absolute memory addresses. If a memory location is free at that time, then the corresponding instruction, if any, is loaded there. The instruction's context ID, in other words program number, is also stored in the memory along with that instruction. If the memory location is occupied by another instruction, then the former instruction is relocated early according to the method described below.

- A distinct ID memory module ID\_MEM<sub>i</sub> is associated with each DRAM<sub>i</sub>. The two memory modules have the same location. The j<sup>th</sup> entry in ID\_MEM contains the starting address of a hash table containing pointers to all instructions with original ID equal to j, but with different context IDs, for j = 0, 1, 2...2<sup>m</sup>- 1. When an instruction with original ID 'k' relocates in the DRAM, then the respective PU-PIM unit stores in the hash table pointed at by the value in address 'k' of the ID\_MEM the context ID and the new address of this instruction.

- The PU-PIM unit keeps track of the location of all instructions in the DRAM. It updates the hash table whenever an instruction is relocated. This scheme implements memory indirect addressing for token propagation with maximum flexibility.

## **2.2.7 Support for Exceptions**

Exception are of two types, either software or hardware. The  $D^2$ -CPU [1] handles both in different way. If it is a software exception and code determines that an erroneous result will show up with the execution of such an instruction, then a thread of instructions are activated to deal with this problem. This thread basically removes faulty instructions from the system. This leads to run time availability of some exception routines. It is not necessary to halt the

execution of instructions that do not belong to the exception routine. If required, however, because of high priority, then the HM can temporarily ignore all instructions in the EXT-CACHE with context ID different from that of the exception determining instruction.

For hardware exceptions, exception routines are initially stored in the DRAM memory. The HM receives the exception request along with an exception ID. This ID uniquely determines the address of the first instruction in the exception routine. The hardware manager forces the PU-PIM to make a copy of the exception routine code, sends the activation token to the first instruction and disables all transfers to the ERU of instructions that have different context ID than this exception ID. It also sends this exception ID to the ERU to disable the execution of instructions with different context IDs. Every exception routine contains a last instruction that upon execution forces the hardware manager to enable all context IDs for the resumption of program execution.

### 2.2.8 Support for Loop Implementation

A bit in each instruction can indicate its inclusion in a loop, so that the instruction can be preserved at the end of its execution for future executions. Only its operand fields are emptied, if necessary, after each execution. Upon exiting a loop, the last instruction sends a special dissolve token to the first instruction in a special routine that removes all loop instructions from the memory; only the PU-PIMs are involved in this process. As far as conditional branching, instructions that are not executed are dissolved similarly by special routines.

Though the methods described in [1] are adequate, a lot of work may be needed in instruction relocation, exceptions and in loop implementations.

The  $D^2$ -CPU design has some similarities with the VLIW architecture. Similar to VLIW,  $D^2$ -CPU has a wide instruction bus, long instructions and many instructions can travel

at a time from the HM to the ERU. Since VLIW is a PC-driven architecture, there are lots of redundant instructions. Secondly, any code is portable with  $D^2$ -CPU, as there is no need for the compiler to group together simple instructions into large ones as needed in VLIW. So there is no need of expensive compilers for the  $D^2$ -CPU model.

The next Chapter discussed in depth a practical approach to  $D^2$ -CPU design. The  $D^2$ -CPU design is implemented on a FPGA, which alters some of the architectural part proposed above. Also, some trivial architectural part is modified as first priority of this thesis work is to prove the feasibility of the pure data-driven model on FPGAs. Instruction relocation and exception handling are not implemented in this work, whereas loop support is implemented.

#### **CHAPTER 3**

# DESIGN OF A FPGA BASED D<sup>2</sup>-CPU

#### 3.1 Introduction

This Chapter deals with a practical implementation of the  $D^2$ -CPU design. The first part explains architectural details. This part demonstrates how the  $D^2$ -CPU design proposed in Chapter 2 will take shape into reality and also discusses difficulties and solutions to them. It also shows how some difficulties lead to few minor changes in the proposed architecture, keeping its purity, as a data-driven machine, intact. The second part mainly deals with its implementation on an FPGA board. Required software and hardware issues are dealt with detail in this part.

# **3.2 Implementation of the D<sup>2</sup>-CPU**

# **3.2.1 Instruction Set Format**

As already discussed, the instruction format changes at each level of the  $D^2$ -CPU design. All fields used by the instructions at different levels are explained below. The instruction format at each level is dealt with detail at the respective design description in this Chapter.

There are in all 12 fields:

• Operand1 (OPD<sub>1</sub>): It holds the first operand. As specified in [1], there are two operand fields either for unary or binary operations. Each is 16 bits wide. Either this field is already filled at compile time or required data from some other instruction, whose address is specified in IID<sub>1</sub>. The length of IID<sub>1</sub> depends upon instruction locality, as either it presents a virtual ID or physical ID. In the first case it is six bits wide and in the second it is seven. Each time, when a token is broadcasted from the

ERU, its address field (namely IAD) is compared with  $IID_1$ , and if matched the  $OPD_1$  is filled with data associated with the token. As a general rule, for unary operations like shift, only this operand is used.

- Operand2 (OPD<sub>2</sub>): It holds the second operand. This is 16 bits wide. If required, it is either supposed to be filled at compile time or depends on another instruction whose address is specified by IID<sub>2</sub>. IID<sub>2</sub> is seven bits wide.

- Operation Code (OPCODE): It is the opcode of the instruction to be executed. There are six bits in this field, out of which the last two bits are reserved to indicate which pipeline it belongs to, i.e. adder, multiplier or shift/logical/comparator. The remaining four bits are used for different shift/logical/comparator instructions. The details of the opcodes and their use in dataflow graphs are discussed in the next Chapter.

| 0000: AND | 0001: OR   | 0010: NAND | 00: Invaild |

|-----------|------------|------------|-------------|

| 0011: NOR | 0100: XOR  | 0101: NOT  | 01: ADD     |

| 0110: EQT | 0111: NEQT | 1000: GT   | 10: MUL     |

| 1001: LT  | 1010: GET  | 1011: LET  | 11: S/L/C   |

| 1100: SHL | 1101: SHR  | 1110: RAL  |             |

| 1111: RAR |            |            |             |

|           |            |            |             |

Figure 3.1 OPCODE Format.

• Instruction Address (IAD): Except DRAM, this field is identity for instructions at the remaining levels. Even a token contains this field, where it signifies the address of the result producing instruction. The number of bits in IAD is either six or seven depending upon virtual ID or physical ID, respectively.

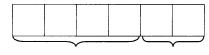

Figure 3.2 OPFL Format.

Operand Field Locator (OPFL): This is a two-bit field and decides the dependency of instructions. IID<sub>1</sub> and/or IID<sub>2</sub> provide instruction addresses on which OPD<sub>1</sub> and/or OPD<sub>2</sub> are dependant.

Clause Answer (CAN): A bit flag which holds the boolean answer for a clause on which the particular instruction depends upon. If the instruction does not depend upon any clause, then CAN is set to '1' and the clause required (CR) bit is set to '0' at compile time. Otherwise CAN is set to '0' and CR to '1'. Clause address (CAD) provides the instruction address on which CAN depends. Whenever a token is propagated its address is compared to CAD, and if matched, the result's last bit is stored in CAN. The instruction will go for execution only if the CAN bit is set to '1'. Obviously CAD is the address of such an instruction which provides a boolean answer, like EQT, NEQT, LT, GT etc.

| CAI | CAD (7) |         | N(1) | CR(1) |

|-----|---------|---------|------|-------|

| CR  | CAN     | CAD     | Sta  | tus   |

| 0   | 1       | Invalid | Rea  | ady   |

| 1   | 0       | Valid   | Not- | ready |

| 1   | 1       | Valid   | Re   | ady   |

| 0   | 0       | Invalid | Inv  | alid  |

Figure 3.3 CAN, CAD, and CR Format.

- Valid Bit (VB): This is a one-bit flag. '1' in this field indicates the instruction is valid and '0' indicates the instruction is invalid. This is a peculiar flag, as this is present at every level in the D<sup>2</sup>-CPU design, including DRAM. As all types of memories are implemented in the conventional style of cache design, this bit indicates the validity of the instruction.

- Loop (LP): This is a two-bit field. This field is used in particular for implementing loop structures in the D<sup>2</sup>-CPU design. "00" indicates the instruction is not involved in any loop structure. "01" in those fields indicates a "merge" node, "11" indicates a

"lock" node, and "10" is assigned to a "switch" node in a loop i.e. a conditional instruction that immediately follows lock node. Details about loop implementation, switch node and merge node are explained in the next Chapter for dataflow graphs and programming with  $D^2$ -CPU design.

• Operand Reuse (ORE): This is also a two-bit field. This field is for instructions, which are involved in loop execution. This field affects the OPFL field. After an instruction inside the loop is sent for execution, its OPFL changes depending upon ORE. '1' in any field of ORE indicates the respective OPD has to be reused, so the respective OPFL field is set to '0'. Thus, in the next iteration it will keep the respective OPDs intact. Details are discussed in the next Chapter.

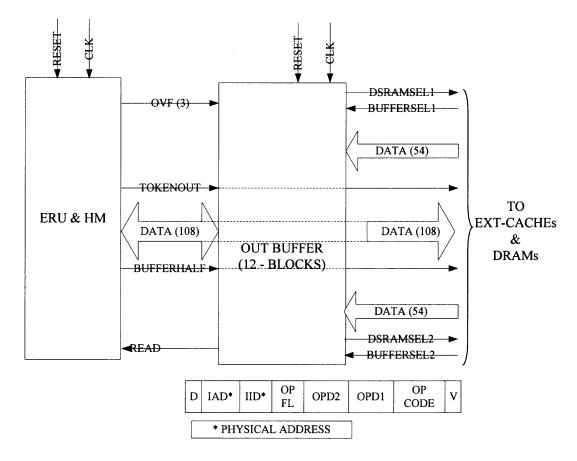

# 3.2.2 ERU Design

The ERU is basically divided into three parts; the SRAM\* and ERU-SRAM memories and the functional units. As dataflow machines are inherent parallel machines, it doesn't make any sense to use single functional unit. As also proposed in [1], one adder, one multiplier and one logic unit are implemented. As the multiplier and adder will take more time to execute than any shift, compare or logical operation, the latter three functionalities are grouped together in one logic unit. By sticking to the basic, "simple is fast" of superscalar RISC principle, three pipelines are implemented, one for each functional unit. So, the SRAM\* and ERU-SRAM are also divided into three parts. A First-In-First-Out (FIFO) buffer is used, for tokens propagated from the ERU to the off-chip memory systems. Figure-3.4 shows an architectural overview of the ERU. The design details of each part in the ERU are discussed below:

• Functional Unit (FU): As already mentioned, three functional units are implemented. 16-bit functional units are generally implemented. For the sake of simplicity, a nonpipelined 8-bit multiplier available by Xilinx as a standard component is used. Though it is an 18 \* 18 multiplier, only the last 8 bits are used, tying the remaining bits to '0'. It produces a 16-bit result. The adder also is a non-pipelined unit. The adder is a 16-bit unit that produces 16-bit results. The logical unit performs shift, rotate, logical functions (and, or, not, etc.), and compare functions (equal to, less than, greater than, etc.). For unary shift and rotate functions only OPD<sub>1</sub> is considered. As all compare instructions are boolean in nature, they produce results as '0' or '1' and this is assigned to the 0<sup>th</sup> bit of the result. This result is used for clause answers; programming is discussed in detail in the next Chapter.

The input to the functional units is a 44-bit wide instruction, consisting of an OPCODE (6-bit),  $OPD_1$  (16-bit),  $OPD_2$  (16-bit), and IAD (6-bit) whereas the output is 22-bit wide token, comprising of IAD and RESULT (16-bit). Each unit puts its result on a 66-bit wide data bus and let FIFO know about it.

• ERU-SRAM: The ERU-SRAM contains ready to execute instructions. The instructions with all required operands filled, that can not execute due to the unavailability of a functional unit are located inside ERU-SRAM. So, the ERU-SRAM can be of any size, but for the sake of simplicity and FPGA realization, minimum of two instructions are assumed in the ERU-SRAM. As mentioned already, the valid bit indicates the resident instruction's validity; the reaming fields constitute the OPCODE (6-bit), OPD<sub>1</sub> (16-bit), OPD<sub>2</sub> (16-bit), and IAD (6-bit).

A count filed, associated with each instruction in the ERU-SRAM, where 2bit count indicates the number of instructions in the SRAM\* depending upon the particular instruction, is also implemented. Since relatively large logic is required to

DATA (104) CI I RESET SRAMSEL SRAM\* OVF (3 BIT) (12 - BLOCKS) OP FL OP D IAD IID v OPD2 OPD1 CODE ERUSEL OUTSRAM **CLK** RESET ERU-SRAM (2 - BLOCKS) OP v IAD OPD2 OPD1 CODE ALUSEL ERUOUT L CLK ADD MUL SHF/LOG/CMP RESE RESULTADD RESULT MUL IAD1 D1 RESULT SLC

DATA(66)

V IAD

FIFO

D1

CLI

READ

IAD2

DATAOUT (44)

IAD1

D1

D2

BUFFERHALF

BUFFERFULL

RESULTSEL1

implement it, it is not included in this version of the  $D^2$ -CPU design due to our FPGA realization.

Figure 3.4 The ERU Design.

SRAM\*: The SRAM\* consists of instructions with either an unfilled operand field or filled with both/required operands. Each SRAM\* has 12 blocks (instructions) in it. The instruction format is as shown in Figure 3.4. A single bit field D determines a dependency whereas OPFL determines which operand field needs to be filled with a token from the instruction IID. Table 3.1 below clears this functionality. The valid bit as usual indicates validity of the instruction.

| D | IID     | OPFL    | STATUS      |

|---|---------|---------|-------------|

| 0 | Invalid | Invalid | Independent |

| 1 | Valid   | 0       | OPD1 Needed |

| 1 | Valid   | 1       | OPD2 Needed |

Table 3.1 SRAM\* Instruction Dependency

In general, the SRAM\* closely resembles in functionality with a large number of reservation stations in Tomasulo's algorithm and it truly makes the whole system work "totally out of order". This is not restricted to only the CPU in the  $D^2$ -CPU design, as it is generally implemented in new microprocessors (e.g. Intel Pentium-IV), where execution becomes out of order for only the instructions residing in the CPU. The EXT-CACHE and DRAM look like as a large extension of reservation stations. This idea makes the  $D^2$ -CPU design a pure data-driven processor, but complicates it.

Each SRAM\* receives two instructions from HM on a very wide (104-bit) bus. Both instructions strictly do not belong to the same functional unit. Each SRAM\* unit scans just the last two bits of each instruction to find out its place. Each SRAM\* indicates its empty status to the memory system through overflow (OVF) signal. • FIFO Buffer: FIFO plays two important roles in the overall working of the system; first, the FIFO buffer plays a cushion between totally unreliable (in number) ERU outputs and consistent inputs to the memory system by means of tokens. Dataflow machines are runaway machines; and firing one instruction subsequently fires many instructions in different parts of the code. This causes any number from 0 to 3 outputs from functional units at any clock cycle. Whereas the in-out data bus to ERU is a bidirectional data bus, it needs some kind of consistency in its operation. FIFO provides this consistency in the input and output of the ERU. The FIFO has bufferhalf and bufferfull signals which play an important role in the overall working of the system as follows:

*Bufferhalf*: This signal indicates its half filled status to the memory system, which in turn stops sending instructions to ERU and receives tokens from ERU.

*Bufferfull*: This signal indicates its full status to the all functional units, ERU-SRAMs, and SRAM\*s, so that they will temporarily stop giving outputs and just insert "bubbles" in the pipeline. Still SRAM\* keeps on the receiving instructions, till it gets filled.

Secondly, the FIFO buffer provides the necessary scanner for each SRAM\* unit. At each clock pulse, an unfilled instruction operand in the SRAM\* gets its operand if its IID field matches with any IAD field in the FIFO. This is an important mechanism to keep consistency in data in and around ERU.

The FIFO sends two tokens out to the hardware manager, whenever there is no data in to the ERU. This is achieved with the help of the bufferhalf signal as explained already. All the activities inside the ERU are synchronized with the clock, even keeping the necessary handshaking signals. Synchronization is implemented for the sake of simplicity, whereas handshaking signals provide more flexibility. This synchronization makes each SRAM\*, ERU-SRAM, functional unit, and FIFO buffer very similar to a conventional four-stage pipeline; a very important difference is that it is "totally out of order". Another important feature of the ERU is that it doesn't have any central control unit, and all the controls are distributed in each unit. Each unit (e.g. SRAM\*) has an autonomous behavior for processing of data and just depends for data upon another unit. This feature achieves our objective of distributed control in the D<sup>2</sup>-CPU design.

In short, the ERU of the  $D^2$ -CPU processor is a superscalar, pipelined, and executed totally out of order assuming distributed control.

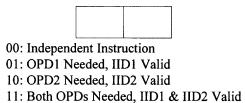

## 3.2.3 Hardware Manager (HM)

Figure 3.5 shows the hardware manager. The basic function of the HM is to convert on the fly a physical address to a virtual one and vice-versa. The HM accepts two instructions at a time from the memory system on a bidirectional data bus (108 bits wide) and converts its required IAD and IID fields from the physical to a virtual address using a table. Then, it puts the same instructions to the input bus of the ERU. Similarly, it accepts two tokens from the ERU, converts the IAD fields to a physical address, makes two copies of it and puts it on the same bidirectional data bus. The reason for two copies is explained in the memory system Section for better understanding.

Let us justify the bidirectional data bus. In fact unidirectional data buses can be used in place of one bidirectional data bus, which would have increased the overall through put of the system. As the data consistency is the main issue in the data-driven design. A mismatch between an instruction and its required token can lead to non-execution of such an instruction and some serious flaws. Even this flaw can be corrected using buffers at each communication level with two unidirectional buses, in place of a bidirectional bus, where these buffers provide a guarantee for data consistency. Again, it is a tradeoff between logic required to implement and the design throughput. For FPGA realization, a bidirectional data bus is used, to reduce logic required to implement the buffers.

### Figure 3.5 Hardware Manager.

From here onwards memory system part is assumed to contain an out-buffer, two cache memories, and the corresponding two main memories.

### 3.2.4 Out-Buffer

The Out-buffer is just an extension to the SRAM\* in the memory system. It can contain 12 instructions with the same format as that for the SRAM\*; the only difference is that IAD and IID represent physical addresses in palace of virtual. The format is shown in Figure 3.5. The Out-buffer receives one instruction from each DSRAM<sub>i</sub> and DRAM<sub>i</sub> pair of memory. It's an FIFO buffer which decides, depending upon the status of the overflow (OVF) signal from the SRAM\* which instructions should be put on the data bus to the ERU. It makes sure that no

two instructions requiring the same fictional units will be available on the data bus. If no such two instructions are available then it will just assign one instruction to the data bus; such cases should be avoided by properly loading the program memory modules.

# Figure 3.6 Out-Buffer.

From here onwards there will only be unidirectional buses (54-bits wide) from each lower level of the memory to a higher level as no data flows from the opposite way. Thus, there will be a unidirectional bus from the DRAM<sub>i</sub> to the DSRAM<sub>i</sub> and from the DSRAM<sub>i</sub> to the Out-buffer. All such buses end at a single Out-buffer. Tokens flow directly from the ERU to each memory module (e.g. DRAM<sub>i</sub>, DSRAM<sub>i</sub> etc.) via a unidirectional bus (108-bit), which is just a continuation of the data bus between the ERU and Out-buffer. The respective tokenout and bufferhalf signals accompany this bus. Data consistency is maintained by stopping all the transactions between any memory modules, whenever a token is out from the ERU. This part is very important for correct functionality of the  $D^2$ -CPU and tokenout and bufferhalf signals achieve this objective.

This 108-bit unidirectional data bus is further divided into two 54-bit unidirectional data buses which carry two identical tokens to two different pairs of the memory module. That's the reason why the HM manager makes two copies of the same token and put them on the 108-bits wide data bus. The functionality of the pair of memory modules and instruction format in each is discussed further. This special instruction format takes advantage of intelligent memories and each memory controller (PU-PIM<sub>i</sub>) uses this format to feed instructions further in the system hierarchy and to the ERU ultimately.

### 3.2.5 EXT-CACHE (DSRAM<sub>i</sub>)

Figure 3.7 shows two pairs of the DRAM<sub>i</sub> and DSRAM<sub>i</sub> and also includes their instruction formats at the bottom. As proposed in [1], there can be multiple pairs of such memory modules, but two are used in our FPGA implementation. Each block consists of one instruction with the OPCODE (6-bit),  $OPD_1$  (16-bit),  $OPD_2$  (16-bit), IAD (7-bit), IID<sub>1</sub> (7-bit), IID<sub>2</sub> (7-bit), OPFL (2-bit), and VB (1-bit) fields. There are two approaches to implement such caches, as both needs extensive support from the main memory. The main memory construction will be discussed below whereas these two approaches are immediately discussed here. The first approach is multithreading, while the second one is the pure datadriven approach.

Multithreading approach: In this case, each cache consists of different threads or blocks, where each thread consists of four (in fact, any small number) instructions. Out of these four, the first instruction will be always an independent instruction, i.e. an instruction with required operands already available at compile time and the remaining three instructions either can depend upon the first or may be interdependent. But none of them depends upon any other instruction out of that thread. So, each thread is totally independent of each other for data but can be depended for a clause on one another.

Figure 3.7 EXT-CACHE and DRAM Memory Modules.

This clause is totally taken care in main memory and when any thread complies with this condition in main memory, can be moved further to EXT-CACHE. So each EXT-CACHE consists of set of totally independent threads.

*Advantages*: By doing this, the design complexity considerably decreases. A conventional cache design can be directly implemented in which each thread is considered as a block with one tag. An example of a fully associative cache is shown in Figure 3.8. It also shows the IAD/IID format once the instruction leaves the EXT-CACHE.

| TAG1 |      | OPD2 | OPD1 | OPCODE | V |

|------|------|------|------|--------|---|

|      | OPFL | OPD2 | OPD1 | OPCODE | ۷ |

|      | OPFL | OPD2 | OPD1 | OPCODE | ۷ |

|      | OPFL | OPD2 | OPD1 | OPCODE | V |

| TAG2 |      | OPD2 | OPD1 | OPCODE | V |

|      | OPFL | OPD2 | OPD1 | OPCODE | ۷ |

|      | OPFL | OPD2 | OPD1 | OPCODE | V |

|      | OPFL | OPD2 | OPD1 | OPCODE | ۷ |

|      | •    |      |      |        |   |

| TAGn |      | OPD2 | OPD1 | OPCODE | V |

|------|------|------|------|--------|---|

|      | OPFL | OPD2 | OPD1 | OPCODE | V |

|      | OPFL | OPD2 | OPD1 | OPCODE | V |

|      | OPFL | OPD2 | OPD1 | OPCODE | V |

If the main-memory has 'm' threads and the cache has 'n' threads, then the # of bits in the TAG field is m/n. Fully Associative Cache

The IAD/IID fields, of an instruction after it leaves the cache for the Out-buffer consists of:

| TAGi       | Cache Address | IL     |

|------------|---------------|--------|

|            |               |        |

| Log₂ (m/n) | ) Log₂ (n)    | 2- bit |

Figure 3.8 Multithreading Approach to EXT-CACHE.

So by keeping the ERU and Out-buffer design the same we can still enjoy the use of conventional proven cache designs. Each OPFL locator indicates dependency; if any bit in OPFL is '1', the last 2-bit of the corresponding OPD will give the address of the instruction, out of the remaining three instructions in that particular thread, which needs to execute before these instructions. In fact a lot of memory is saved in two IID and one IAD fields. Also, whenever any token is out, it just need to match tag address of only one thread, and if that matches then the particular result will be dropped in any required operand field of the remaining unexecuted instructions in that thread. So a lot of saving in the logic is achieved.

• Pure *Data-driven* Approach: In the multithreading approach flexibility is lost as dependency remains only inside a thread. But our approach develops a pure dataflow structure without any relevant compromise. So as shown in Figure 3.9, a block consists of only one instruction in our implementation. Each instruction belongs to one of the three classes already defined in Chapter 2.

A total of 16 such blocks are implemented, which can operate totally in parallel. Depending upon its internal states, defined by its flags, each block will "inform" the cache-controller about its readiness. Then, the cache-controller will choose on a first-come-first-serves basis an instruction to forward to the Out-buffer. Similarly, tokens propagated by ERU also broadcasted on a same data bus. Each block, if required, compares the IAD of the token with its IIDs and if a match occurs, fills the respective OPD, indicated by OPFL. This gives maximum flexibility, which is used dynamically to exploit the full level of parallelism in the application program.

Figure 3.9 Pure Data-driven Approach for the EXT-CACHE.

## 3.2.6 Main-Memory and PU-PIM<sub>i</sub> (DRAM<sub>i</sub>)

The main memory has same structure with the EXT-CACHE. As already mentioned, to implement any of the above two approaches respective main-memory support is needed in the same style as that for EXT-CACHE. As the pure data-driven approach is used, here we mainly discuss its efficient implementation in the main-memory.

Figure 3.10 Pure Data-driven Approach to Main-Memory.

Figure 3.10 shows the actual implementation of DRAM<sub>i</sub>. The structure is the same to that of the EXT-CACHE. The only difference is instruction format, which supports clauses and static loop implantation with the help of the Lock method. Both these uses are discussed in the next Chapter. Whenever a block is ready, it will indicate this to the PU-PIM (main-memory controller) with control signals and then PU-PIM will decide, on a first-come-first-

served basis, which instruction should go to EXT-CACHE and should modify the flags accordingly.